Разработка арифметико-логического устройства под управлением микропрограммного автомата

О.Ю. Жарова

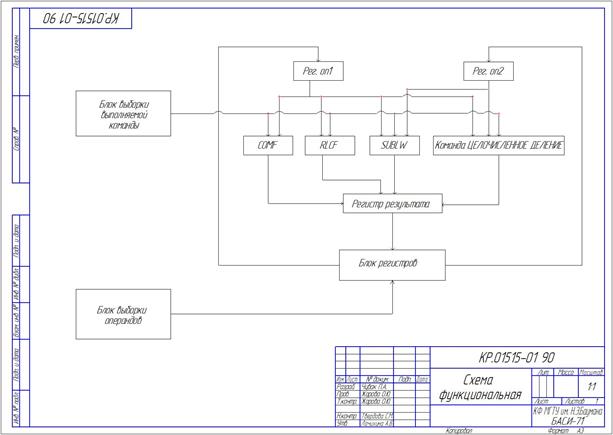

Разработка арифметико-логического устройства под управлением микропрограммного автомата

Методические указания по выполнению курсовой работы

по дисциплине «Аппаратные средства вычислительной техники»

Калуга

УДК 681.3-7

ББК 32.973

Данные методические указания разработаны в соответствии с учебным планом специальности «Информационная безопасность автоматизированных систем».

Указания рассмотрены и одобрены:

кафедрой ЭИУ6-КФ «Информационная безопасность автоматизированных систем»

протокол № ___ от ___________ 2015 г.

Зав. кафедрой ЭИУ6-КФ ______________д.т.н., доц. Мазин А.В.

методической комиссией факультета ЭИУК

протокол № _____ от ____________________ 2015 г.

Председатель методической комиссии

факультета ЭИУК ___________________к.т.н., доц. Адкин М.Ю.

методической комиссией Калужского филиала МГТУ им. Н.Э. Баумана

протокол № _____ от ____________________ 2015 г.

Председатель методической комиссии

Зам. Директорапо учебнойработе

КФ МГТУ им. Н.Э. Баумана _________________ Перерва О.Л.

Рецензент:

к.т.н., доц. _________________ Адкин М.Ю.

Авторы: ассистент

кафедры ЭИУ6-КФ__________________ Жарова О. Ю.

В методических указаниях изложены практические приемы проектирования узлов вычислительной техники. Предназначено для студентов специальности «Информационная безопасность автоматизированных систем» и может быть рекомендовано к применению при проведении курсовой работы по курсу «Безопасность операционных систем».

© Калужский филиал МГТУ им. Н.Э. Баумана, 2015 г.

© Кафедра ЭИУ6-КФ, 2015г.

© Жарова О.Ю., 2015г.

Цель работы: разработать АЛУ для заданного набора команд.

Задачи:Разработать АЛУ для заданного набора команд, управление которым должно осуществляться микропрограммным автоматом, на вход которого подается код операции и адрес операндов, после чего происходит, и выполнение заданной операции с занесением результатов в регистр результата.

Требования к отчету:

Пояснительная записка должна быть объемом не менее 40 страниц.

Графическая часть выполняется в виде приложения в соответствии с ЕСПД.

Выполнение курсовой работы

Необходимо разработать АЛУ реализующее заданные команды. Для управления АЛУ в разрабатываемой схеме должен содержаться МПА и СК. Выборка операндов должна производиться из регистровой памяти. Способ адресации - регистровый. результат должен помещаться обратно в регистровую память, либо формировать признак в регистре признаков. Общая схема должна представлять собой упрощенную функциональную схему фон-неймановской вычислительной машины.Для проверки правильности работы схемы необходимо написать программу на ассемблере с использованием заданных команд.

Этапы работы:

Этап 1: отдельные модели на каждую команду в среде моделирования. Программы на языке ассемблер, для каждой команды. Исследовательская часть записки.

Этап 2: Общая модель АЛУ с управляющей частью. Конструкторская часть записки.

Этап 3: Оформление графической части. Технологическая часть записки.

Оформление пояснительной записки:

Пояснительная записка должна быть оформлена в соответствии с ГОСТ 2.105-95. Пример содержания приведен в приложении 1.

Содержание пояснительной записки:

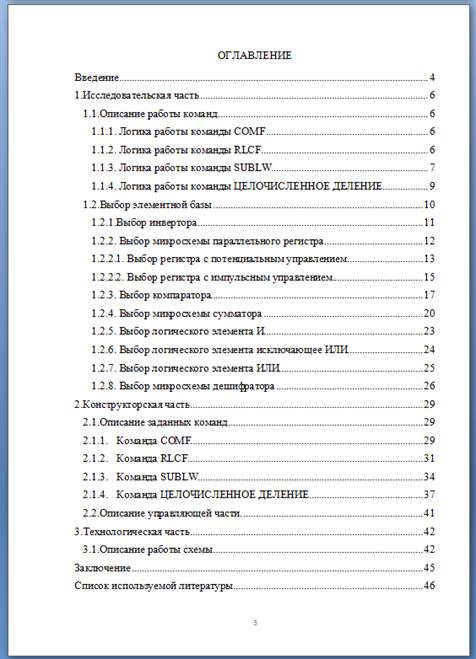

Оглавление: страницы должны в обязательном порядке совпадать.

Введение: общие теоретические сведения по теме курсовой работы цель, задача и задание курсовой работы.

Исследовательскую часть:

1.1. Подробное описание работы заданных команд, обязательно приведены примеры работы каждой команды в двоичном виде.

1.2. Выбор элементной базы. Выбор каждого элемента должен производиться на основе анализа двух аналогов. Аналог это микросхема, которая выполняет по меньшей мере те же действия, что и требуемый элемент. Ее функционал может включать дополнительные возможности, но не может быть заведомо ниже требуемого.

Конструкторскую часть:

2.1. Описание принципа функционирования схемы при выполнении каждой из заданных команд. Должны быть приведены программы на языке ассемблер реализующие команды с теми же операндами.

2.2. Описание схемы управления АЛУ.

Технологическую часть:

3. Подробное описание принципов взаимодействия с моделью. Инструкции использования модели для каждой команды, а именно, каким образом и в какой генератор шаблонов можно ввести код операции и адреса операндов, в каком регистре формируется результат, и как его интерпретировать, если результат не конкретное число а признак.

Список литературы.

Примеры оформления приведены в Приложении 1.

Теоретическая часть

Арифметико-логическое устройство (АЛУ) предназначено для арифметической и логической обработки данных.

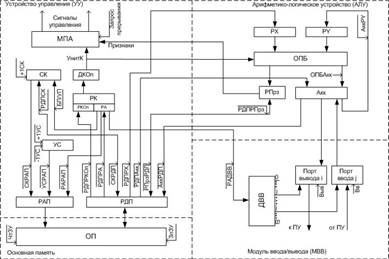

Рисунок 1 Типовая функциональная структура ВМ.

АЛУ содержит:

Операционный блок (ОПБ) непосредственно выполняет арифметические и логические операции над данными. Выбор конкретной операции из возможного списка определяется КОп команды (поступает из ДКОп). В действительности КОп сначала преобразуется в МПА в иную форму, затем из МПА поступает в АЛУ. ОПБ современных АЛУ представляют собой комбинационные схемы, то есть не обладают внутренней памятью и до момента сохранения результата операнды должны присутствовать на входе ОПБ.

Регистры операндов (PX, PY) обеспечивают сохранение операндов на входе ОПБ до получения результата операции и его записи.

Регистр признаков (РПрз) предназначен для фиксации и хранения признаков (флагов) результата последней выполненной операции. Формирование флагов осуществляется блоком формирования состояний РПрз, который может либо входить в состав ОПБ, либо реализуется в виде внешней схемы, расположенной между ОПБ и РПрз.

Аккумулятор (Акк) содержит один из операндов, участвующих в операции. В него же помещается результат выполнения операции.

Основная память (ОП). Вне зависимости от типа используемых СБИС ячейка ОП представляет собой массив запоминающих элементов (ЗЭ), способных хранить единицу информации, как правило, в виде одного байта.

Все ячейки ОП являются адресуемыми и организованы в виде матрицы. Выбор определенной ячейки осуществляется подачей разрешающих сигналов на соответствующую строку и столбец этой матрицы. Это обеспечивается дешифратором адреса памяти, преобразующим адрес ячейки из РАП в разрешающие сигналы, подаваемые в горизонтальную и вертикальную линии матрицы, на пересечении которых и находится ячейка.

ОП реализуется на базе нескольких СБИС. Процесс обращения к ячейке состоит из выбора нужной микросхемы (на основании старших разрядов) и выбора ячейки внутри этой микросхемы (на основании младших разрядов).

Практическая часть

Для построения схемы АЛУ потребуется знание стандарта ГОСТ 2.743-91 «ОБОЗНАЧЕНИЯ УСЛОВНЫЕ ГРАФИЧЕСКИЕ В СХЕМАХ. ЭЛЕМЕНТЫ ЦИФРОВОЙ ТЕХНИКИ», введенного 01.01.93.

Настоящий стандарт устанавливает общие правила построения условных графических обозначений (УГО) элементов цифровой техники в схемах, выполняемых вручную или с помощью печатающих и графических устройств вывода ЭВМ во всех отраслях промышленности. Ниже приведены основные положения и примеры УГО элементов, которые потребуются для построения АЛУ.

Возможные варианты элементов для реализации АЛУ

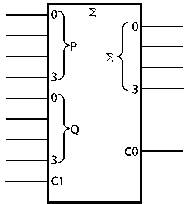

Сумматор

Рисунок 6 – Функциональная схема микросхемы 74HC283

В качестве сумматора можно использовать микросхему 74HC283, который представляет собой четырехзначный двоичный сумматор с ускоренным переносом.

Таблица состояний микросхемы 74HC283

| Входы | Выходы | |||

| Ai | Bi | C0 | C1 | Si |

Рисунок 7 – Условное графическое обозначение микросхемы 74HC283

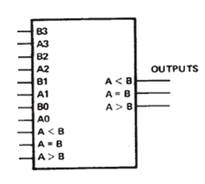

Компаратор

Рисунок 8- Функциональная схема регистра 7485

Для сравнения чисел в качестве компаратора можно использовать микросхему 7485 (4-хразрядный компаратор).

Таблица состояний регистра 7485

| Входы | Выходы | |||

| x | y | FA=B | FA>B | FA<B |

Рисунок 9 – Условное графическое обозначение микросхемы 7485

Инвертор

Рисунок 10- УГО инвертора.

В качестве инвертора можно использовать микросхему 74ALS которая осуществляет преобразование логической единицы в логический ноль и наоборот.

Таблица состояний логического элемента 74ALS

| Вход | Выход |

| x | y |

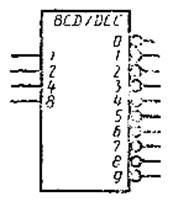

Дешифратор

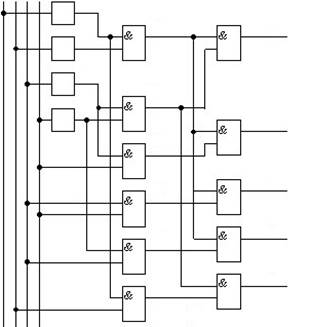

Рисунок 11 – Функциональная схема микросхемы 74HC138

В качестве дешифратора в управленческой части можно использовать дешифратор 74HC138.

Таблица состояний микросхемы 74HC138

| №входного набора | Входы | Выходы | |||||||||

| X3 | X2 | X1 | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | |

Рисунок 12 – Условное графическое обозначение микросхемы 74HC138

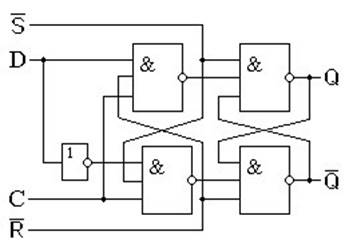

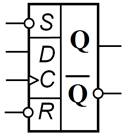

Триггер

Рисунок 13 – Функциональная схема микросхемы CD4013B

В качестве триггера можно использовать микросхему CD4013B, которая является двухступенчатым D – триггером flip-flop.

Таблица состояний D– триггера

| Режим работы | Входы | Выходы | ||||

| Асинхронный | Синхронный | |||||

| S | R | C | D | Q | Q | |

| Асинхронная установка 1 | x | x | ||||

| Асинхронная установка 0 | x | x | ||||

| Запрещенное состояние | x | x | ||||

| Установка 1 | ↑ | |||||

| Установка 0 | ↑ |

Рисунок 14 – Условное графическое обозначение микросхемы CD4013B

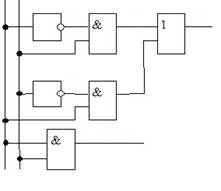

Логический элемент И

Рисунок 15 – Условное графического обозначение логического элемента И

В качестве этого элемента можно использовать микросхему 74HC08. При подаче напряжения низкого уровня на один или оба входа каждого элемента на выходе микросхемы 74HC08 устанавливается напряжение низкого уровня. Если на оба входа подается напряжение высокого уровня, то на выходе формируется напряжение высокого уровня.

Таблица истинности микросхемы 74HC08

| Входы | Выходы | |

| A | B | Y |

Приемы реализации АЛУ

Построение схемы АЛУ в данной курсовой работе выполняется в среде разработки Proteus.

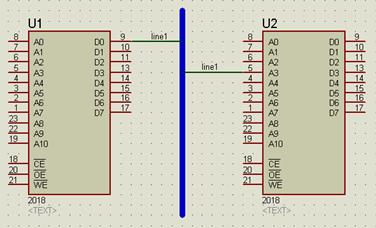

Изначальное задание операндов в регистровой памяти, задание кода операции и адресов операндов проще всего реализовать с использованием генераторов шаблонов PatternGenerator, при преобразовании модели в электрическую принципиальную схему, информационные входы подсоединяются к некоторому условному разъему, как и информационные выходы результирующего регистра. К этому же разъему подсоединяются управляющие входы, по которым задаются код операции и адреса операндов в регистровой памяти. Генераторы шаблонов в электрической принципиальной схеме не отображаются. Для оптимизации схемы необходимо использовать шину.

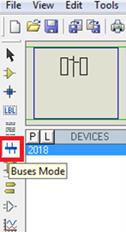

Работа с шиной в Proteus

Для того чтобы пользоваться шиной, необходимо в боковом меню выбрать BusesMode, как показано на рисунке:

В поле создания схемы нужно установить курсор и выполнить однократное нажатие левой кнопкой мыши, после чего можно провести линию (шину) необходимой длины. Так же однократным кликом левой кнопки мыши указываются повороты шины, а двойным – конец шины. Далее можно поставить 2 элемента, входы/выходы которых будут соединяться.

Для того чтобы подать сигнал с выхода «9» регистра U1 на вход «5» регистра U2, следует провести провода от «9» и «5» к шине, после чего добавить для них одинаковый Label. Label создаётся при помощи клика правой кнопки мыши по проводу и выбора в появившемся меню пункта «PlaceWireLabel»

Использование шины делает схему менее нагруженной, упрощает процесс ее создания, а так же облегчает понимание схемы.

Индивидуальные задания

Выполняются на основе системы команд PIC18XX 2 (см стр.214 -216 datasheet), и процессоров Intel, так же каждому отдельно выдается определенный вид команды деления.

| Вар. | Команды PIC | Команды Intel |

| 1. | ADDWF, MULWF, | NEG |

| 2. | IORLW | JNAE, SHR |

| 3. | RLCF, SUBLW | JAE |

| 4. | BTG, NEGF | JNB |

| 5. | MULLW | JBE, RCL |

| 6. | RLNCF, ADDLW | JNBE |

| 7. | SUBWF, SETF | JE |

| 8. | INCFSZ, BTFSS | JNE |

| 9. | RRCF, ANDLW | JL |

| 10. | BTFSS | JNGE, ROL |

| 11. | DCFSNZ, CLRF | JGE |

| 12. | XORWF, SUBFWB | JNL |

| 13. | INCF, MULLW | JLE |

| 14. | COMF, BCF | JNLE |

| 15. | RLNCF, ANDWF | JG |

| 16. | ADDWF, SUBLW | JNLE |

| 17. | BSF | JP, SUB |

| 18. | IORWF | JPO |

| 19. | RRNCF, MULWF, | JS |

| 20. | COMF, SUBLW | JNS |

| 21. | RRCF | JC, TEST |

| 22. | ADDWF, XORWF | JNC |

| 23. | SETF, IORWF | ADD |

| 24. | RRCF, INFSNZ, | JNO |

| 25. | RLNCF, DECF | JO |

| 26. | RLNCF, MULLW | XOR |

Приложение 1. Оформление курсовой работы

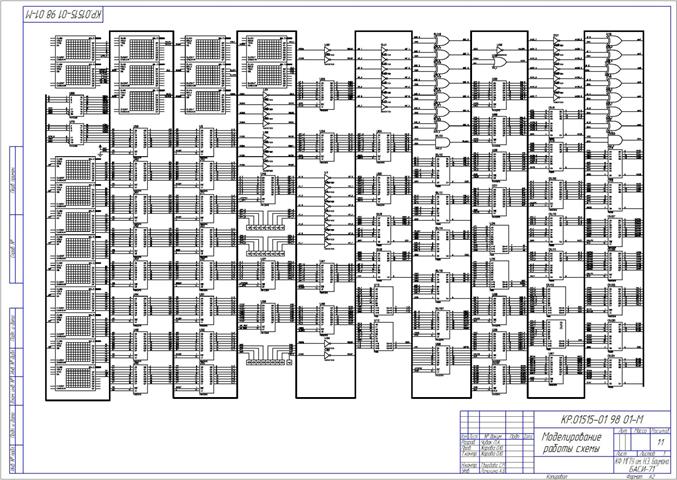

Приложение 2. Пример оформления графической части.

О.Ю. Жарова

Разработка арифметико-логического устройства под управлением микропрограммного автомата

Методические указания по выполнению курсовой работы

по дисциплине «Аппаратные средства вычислительной техники»

Калуга

УДК 681.3-7

ББК 32.973

Данные методические указания разработаны в соответствии с учебным планом специальности «Информационная безопасность автоматизированных систем».

Указания рассмотрены и одобрены:

кафедрой ЭИУ6-КФ «Информационная безопасность автоматизированных систем»

протокол № ___ от ___________ 2015 г.

Зав. кафедрой ЭИУ6-КФ ______________д.т.н., доц. Мазин А.В.

методической комиссией факультета ЭИУК

протокол № _____ от ____________________ 2015 г.

Председатель методической комиссии

факультета ЭИУК ___________________к.т.н., доц. Адкин М.Ю.

методической комиссией Калужского филиала МГТУ им. Н.Э. Баумана

протокол № _____ от ____________________ 2015 г.

Председатель методической комиссии

Зам. Директорапо учебнойработе

КФ МГТУ им. Н.Э. Баумана _________________ Перерва О.Л.

Рецензент:

к.т.н., доц. _________________ Адкин М.Ю.

Авторы: ассистент

кафедры ЭИУ6-КФ__________________ Жарова О. Ю.

В методических указаниях изложены практические приемы проектирования узлов вычислительной техники. Предназначено для студентов специальности «Информационная безопасность автоматизированных систем» и может быть рекомендовано к применению при проведении курсовой работы по курсу «Безопасность операционных систем».

© Калужский филиал МГТУ им. Н.Э. Баумана, 2015 г.

© Кафедра ЭИУ6-КФ, 2015г.

© Жарова О.Ю., 2015г.

Цель работы: разработать АЛУ для заданного набора команд.

Задачи:Разработать АЛУ для заданного набора команд, управление которым должно осуществляться микропрограммным автоматом, на вход которого подается код операции и адрес операндов, после чего происходит, и выполнение заданной операции с занесением результатов в регистр результата.

Требования к отчету:

Пояснительная записка должна быть объемом не менее 40 страниц.

Графическая часть выполняется в виде приложения в соответствии с ЕСПД.

Выполнение курсовой работы

Необходимо разработать АЛУ реализующее заданные команды. Для управления АЛУ в разрабатываемой схеме должен содержаться МПА и СК. Выборка операндов должна производиться из регистровой памяти. Способ адресации - регистровый. результат должен помещаться обратно в регистровую память, либо формировать признак в регистре признаков. Общая схема должна представлять собой упрощенную функциональную схему фон-неймановской вычислительной машины.Для проверки правильности работы схемы необходимо написать программу на ассемблере с использованием заданных команд.

Этапы работы:

Этап 1: отдельные модели на каждую команду в среде моделирования. Программы на языке ассемблер, для каждой команды. Исследовательская часть записки.

Этап 2: Общая модель АЛУ с управляющей частью. Конструкторская часть записки.

Этап 3: Оформление графической части. Технологическая часть записки.

Оформление пояснительной записки:

Пояснительная записка должна быть оформлена в соответствии с ГОСТ 2.105-95. Пример содержания приведен в приложении 1.

Содержание пояснительной записки:

Оглавление: страницы должны в обязательном порядке совпадать.

Введение: общие теоретические сведения по теме курсовой работы цель, задача и задание курсовой работы.

Исследовательскую часть:

1.1. Подробное описание работы заданных команд, обязательно приведены примеры работы каждой команды в двоичном виде.

1.2. Выбор элементной базы. Выбор каждого элемента должен производиться на основе анализа двух аналогов. Аналог это микросхема, которая выполняет по меньшей мере те же действия, что и требуемый элемент. Ее функционал может включать дополнительные возможности, но не может быть заведомо ниже требуемого.

Конструкторскую часть:

2.1. Описание принципа функционирования схемы при выполнении каждой из заданных команд. Должны быть приведены программы на языке ассемблер реализующие команды с теми же операндами.

2.2. Описание схемы управления АЛУ.

Технологическую часть:

3. Подробное описание принципов взаимодействия с моделью. Инструкции использования модели для каждой команды, а именно, каким образом и в какой генератор шаблонов можно ввести код операции и адреса операндов, в каком регистре формируется результат, и как его интерпретировать, если результат не конкретное число а признак.

Список литературы.

Примеры оформления приведены в Приложении 1.