Интегральные микросхемы (ИМС) логических элементов

КОНСПЕКТ ЛЕКЦИЙ

(4 семестр)

для студентов 1 курса

специальностей 11.02.01 Радиоаппаратостроение

11.02.02 Техническое обслуживание и ремонт

радиоэлектронной техники (по отраслям)

г. Нижний Новгород

2016г.

Содержание

1 Интегральные микросхемы логических элементов………………3

2 Усилительные устройства…………………………………………..3

2.1 Структурна схема усилителя………………………………10

2.2 Классификация усилителей………………………………...11

2.3 Показатели качества усилителей…………………………. 12

2.4 Обратная связь в усилителях………………………………18

2.5 Питание усилителей по постоянному току………………..20

2.6 Стабилизация режима работы усилителя…………………22

2.7 Анализ АЧХ ШПУ……………………………………….....25

2.8 Резонансные усилители…………………………………….28

2.9 Оконечные каскады (усилители мощности)………………32

2.10 Усилители постоянного тока……………………………..35

Литература…………………………………………………………...46

Интегральные микросхемы (ИМС) логических элементов

В основе цифровых схем лежат простейшие транзисторные ключи, характеризующиеся двумя устойчивыми состояниями (для биполярного транзистора – это режим насыщения и режим отсечки).

Рассмотрим ВАХ транзистора ОЭ:

IК нагрузочная прямая

IБ4

ЕП/RК А IБ3

IБ2

насыщение А` IБ1

0 IБ=0 UКЭ

отсечка ЕП

UКЭ НАС

UКЭ ОТС

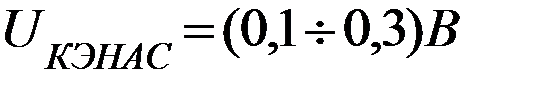

· Если транзистор находится в режиме насыщения (полностью открыт), то его выходное напряжение равно  - мало.

- мало.

Обычно принимают  и считают это малое напряжение логическим нулем (

и считают это малое напряжение логическим нулем (  ).

).

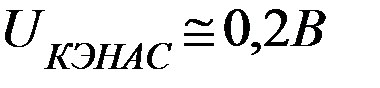

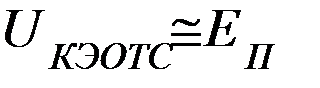

· Если транзистор находится в режиме отсечки (полностью закрыт), то его выходное напряжение равно  - велико, что соответствует логической единице (

- велико, что соответствует логической единице (  ).

).

Таким образом, имеем двоичную систему исчисления.

Существует три основных логических элемента: И (операция умножения), ИЛИ (операция сложения), НЕ (операция отрицания).

1.1 Эмиттерно-связанная логика (ЭСЛ)

1.1 Эмиттерно-связанная логика (ЭСЛ)

Схемы ЭСЛ являются самыми быстродействующими, т.к. транзисторы в них работают в ненасыщенном (активном) режиме. Время их переключения мало – единицы наносекунд.

Характерная особенность схемы:

Заземляется плюсовая клемма ИП (+ЕП). Этим ослабляется влияние нестабильности ИП на уровни напряжения  и

и  , что важно, т.к. разница между ними в данной схеме незначительна.

, что важно, т.к. разница между ними в данной схеме незначительна.

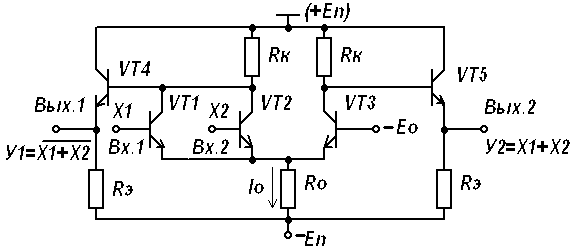

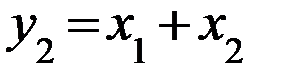

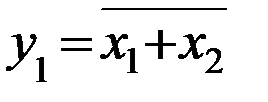

Схема осуществляет операцию ИЛИ-НЕ/ИЛИ:

|  |  |  |

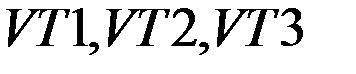

В основе схемы лежит переключатель тока, выполненный на транзисторах  .

.

Принцип работы переключателя тока:

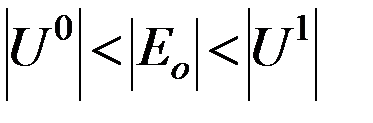

Опорное напряжение (-Ео) выбирается таким образом, чтобы выполнялось неравенство:  (

(

).

).

Опорное напряжение может восприниматься транзистором  и как

и как  , и как

, и как  , все зависит от входных сигналов.

, все зависит от входных сигналов.

Если на оба входа поданы  (

(  и

и  заперты), то тогда опорное напряжение воспринимается транзистором

заперты), то тогда опорное напряжение воспринимается транзистором  как

как  (т.к.

(т.к.  ).

).  открывается, и ток

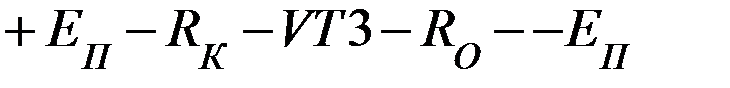

открывается, и ток  течет через правое плечо по цепи:

течет через правое плечо по цепи:  .

.

Если на оба входа (или на один из них) поданы  , то тогда опорное напряжение воспринимается

, то тогда опорное напряжение воспринимается  как

как  (т.к.

(т.к.  ) и он заперт, т.е. ток

) и он заперт, т.е. ток  течет через левое плечо по цепи:

течет через левое плечо по цепи:  открытый транзистор -

открытый транзистор -  .

.

а) Пусть  . При этом транзисторы

. При этом транзисторы  закрыты,

закрыты,  открыт, т.е. работает правое плечо. Сопротивление открытого

открыт, т.е. работает правое плечо. Сопротивление открытого  мало, следовательно, мало и падение напряжения на нем. Таким образом, на базу

мало, следовательно, мало и падение напряжения на нем. Таким образом, на базу  подается

подается  .

.  - это эмиттерный повторитель (схема ОК), т.к. нагрузкой его является резистор в эмиттерной цепи -

- это эмиттерный повторитель (схема ОК), т.к. нагрузкой его является резистор в эмиттерной цепи -  .

.

Выходное напряжение эмиттерного повторителя приблизительно равно его входному напряжению (  ).

).

на входе

на входе  будет «повторен» им, т.е. на выходе 2 установится низкий потенциал, соответствующий логическому нулю:

будет «повторен» им, т.е. на выходе 2 установится низкий потенциал, соответствующий логическому нулю:  .

.

Т.к.  заперты, их сопротивления велики. Поскольку они соединены параллельно, их общее сопротивление также будет велико, следовательно, будет велико и падение напряжения на нем. Таким образом, на вход эмиттерного повторителя

заперты, их сопротивления велики. Поскольку они соединены параллельно, их общее сопротивление также будет велико, следовательно, будет велико и падение напряжения на нем. Таким образом, на вход эмиттерного повторителя  будет подана

будет подана  , которая им «повторится», т.е. на выходе 1 установится высокий потенциал, соответствующий логической единице:

, которая им «повторится», т.е. на выходе 1 установится высокий потенциал, соответствующий логической единице:  .

.

б) Пусть  . При этом работает левое плечо.

. При этом работает левое плечо.  открыты, их сопротивления малы, общее сопротивление также мало, следовательно, мало и падение напряжения на нем. Таким образом, на вход

открыты, их сопротивления малы, общее сопротивление также мало, следовательно, мало и падение напряжения на нем. Таким образом, на вход  подается

подается  , который после «повторения» им даст на выходе 1 низкий потенциал, соответствующий логическому нулю:

, который после «повторения» им даст на выходе 1 низкий потенциал, соответствующий логическому нулю:  .

.

В этот момент  заперт, его сопротивление велико, следовательно, будет велико и падение напряжения на нем. Таким образом, на вход

заперт, его сопротивление велико, следовательно, будет велико и падение напряжения на нем. Таким образом, на вход  подается

подается  , которая после «повторения» им даст на выходе 2 высокий потенциал, соответствующий логической единице:

, которая после «повторения» им даст на выходе 2 высокий потенциал, соответствующий логической единице:  .

.

в) Пусть  ;

;  . В этом случае снова работает левое плечо.

. В этом случае снова работает левое плечо.  открыт, его сопротивление мало.

открыт, его сопротивление мало.  закрыт, его сопротивление велико. Общее сопротивление будет меньше меньшего, т.е. мало, следовательно, мало будет и падение напряжения на нем. Таким образом, на вход

закрыт, его сопротивление велико. Общее сопротивление будет меньше меньшего, т.е. мало, следовательно, мало будет и падение напряжения на нем. Таким образом, на вход  подается

подается  , который после «повторения» им даст на выходе 1 низкий потенциал, соответствующий логическому нулю:

, который после «повторения» им даст на выходе 1 низкий потенциал, соответствующий логическому нулю:  .

.

В этот момент  заперт, его сопротивление велико, следовательно, велико будет и падение напряжения на нем. Таким образом, на вход

заперт, его сопротивление велико, следовательно, велико будет и падение напряжения на нем. Таким образом, на вход  подается

подается  , которая после «повторения» им даст на выходе 2 высокий потенциал, соответствующий логической единице:

, которая после «повторения» им даст на выходе 2 высокий потенциал, соответствующий логической единице:  .

.

Таким образом, схема реализует операцию ИЛИ-НЕ/ИЛИ.