Электрическая схема управления 3 страница

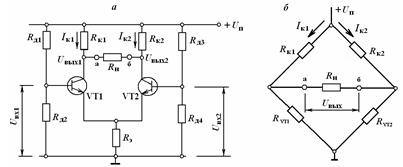

На рис. 2.46 представлен дифференциальный усилительный каскад и его эквивалентная схема [13]. Усилитель состоит из двух каскадов, у которых имеется общий эмиттерный резистор Rэ.

Элементы схемы образуют мост (рис. 2.46б), в одну диаганаль которого включен источник питания Uп, а в другую сопротивление нагрузки Rн Для балансировки моста необходимо, чтобы выполнялось условие равновесия моста Rк1 RVT2 = Rк2 RVT1. При этом условии Uвых = 0. Таким образом, если элементы схемы будут полностью идентичны, то выходное напряжение будет оставаться постоянным.

Uвых = Rк1 ∆ Iк1 - Rк2 ∆ Iк2 .

Дифференциальный усилитель имеет два входа и два выхода, поэтому для выходного напряжения можно записать

Uвых = Uвых1 - Uвых2 = - К1 Uвх1 -( - К2 Uвх2),

где К1 и К2 соответственно коэффициенты усиления каскадов на транзисторах VT1 и VT2.

В отличие от полезного сигнала, который поступает на входы дифференциального усилителя в противофазе, на входы усилителя действуют сигналы, совпадающие по фазе. Такие сигналы называются синфазными. Появление данных сигналов обусловлено действием различных дестабилизирующих факторов, например, изменением температуры окружающей среды, изменением питающих напряжений наводками внешних электромагнитных полей [13]. Для идеального дифференциального усилителя синфазные сигналы полностью подавляются. В реальных усилителях из-за не идентичности каскадов подавление будет не полным и характеризуется коэффициентом подавления синфазных помех Кпсф. Величина Кпсф в современных дифференциальных усилителях достигает 104-106. Коэффициент Кпсф в значительной степени характеризует дрейф нуля усилителя, т.е. изменение выходного напряжения при постоянном входном сигнале. Для снижения дрейфа нуля производят подбор пар транзисторов с одинаковыми параметрами и увеличение Rэ. Для увеличения Rэ в эмиттерную цепь ставится не пассивный резистор, а нелинейный двухполюсник, например, транзисторный источник тока на биполярном или полевом транзисторе. Эти схемы при небольшом статическом сопротивлении обладают большим дифференциальным сопротивлением.

|

Рис. 2.46. Дифференциальный усилительный каскад (а)

и его эквивалентная схема (б)

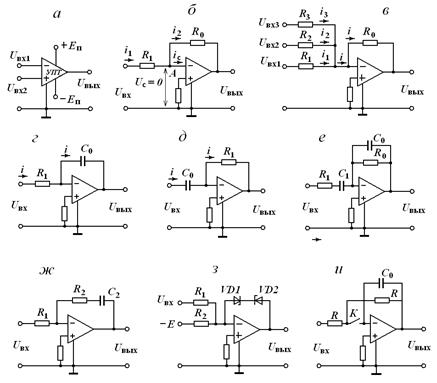

Современные операционные усилители (рис. 2.47) в виде интегральных микросхем УПТ являются универсальными многоцелевыми базовыми элементами [11]. Их применяют не только в качестве усилителей, выполняющих указанные операции, но и элементов сравнения в системах автоматического регулирования, ограничения сигналов, формирования напряжения прямоугольной или пилообразной формы, а также в схемах стабилизации напряжения и т.д.

|

Рис. 2.47. Структура и схемы включения операционных усилителей

Операционный усилитель (см. рис. 2.47а) представляетсобой микросхему УПТ [11] с двумядифференциальными входами и одним общим выходом. Один из входов называют инвертирующим (–), другой – неинвертирующим (+). Сигналу на инвертирующем входе соответствует сигнал на выходе усилителя в противофазе по отношению к входному сигналу. Сигналу на неинвертирующем входе соответствует сигнал на выходе в той же фазе. Коэффициент усиления по напряжению операционных усилителей находится в пределах 104 – 106. Постоянная времени усилителя составляет несколько микросекунд.

На рис. 2.47б приведена структура усилителя, инвертирующего и умножающего входной сигнал на постоянный коэффициент. Во входную цепь такого усилителя и в цепь обратной связи включены резисторы с активными сопротивлениями R1 и R0. Так как входной ток усилителя ic = 0, то ток через оба резистора R1 и R0будет одним и тем же – i.

По второму закону Кирхгофа ток через резистор R1 в контуре входной цепи

i1 = Uвх / R1.

Аналогично, ток в цепи резистора R0

i2 = Uвых / R0.

Так как точку А считают потенциально заземленной, то по первому закону Кирхгофа

i1 + i2 = 0.

Тогда Uвх / R1 + Uвых / R0 = 0. Отсюда

Uвых = –  Uвх = – K 1 Uвх,

Uвх = – K 1 Uвх,

где K 1 =  – коэффициент усиления усилителя.

– коэффициент усиления усилителя.

Знак минус означает, что фаза выходного напряжения сдвинута по фазе на 180о относительно входного напряжения. Следует заметить, что выходное напряжение рассматриваемого усилителя не зависит от коэффициента усиления собственно УПТ, что свидетельствует о высокой стабильности работы схемы.

На рис. 2.47в приведена схема суммирующего усилителя с тремя входами. Напряжение на выходе усилителя равно сумме входных напряжений, умноженных на соответствующие коэффициенты усиления

Uвых = –

Uвх1 +

Uвх1 +  Uвх2 +

Uвх2 +  Uвх3

Uвх3  = – K1 Uвх1 – K2 Uвх2 – K3 Uвх3,

= – K1 Uвх1 – K2 Uвх2 – K3 Uвх3,

где K1, K2, K3 – коэффициенты усиления по отдельным входам усилителя.

Из полученного выражения следует, что напряжение на выходе усилителя равно сумме входных напряжений, умноженных на соответствующие коэффициенты усиления.

В схеме интегрирующего усилителя (рис. 2.47г) напряжение на выходе усилителя

Uвых = –  Uвх = –

Uвх = –  Uвх,

Uвх,

где Т = R1C0 – постоянная времени усилителя; р = d/dt – оператор дифференцирования.

Аналогично для дифференцирующего усилителя (рис. 2.47д) получим

Uвых = –  Uвх = –

Uвх = –  Uвх.

Uвх.

Обычно схему дифференцирования, изображенную на рис. 2.47д в чистом виде не применяют: она усиливает помехи [11]. Схема приближенного дифференцирования, лишенная этого недостатка, приведена на рис. 2.47е. для этой схемы

Uвых = –  Uвх,

Uвх,

где Т = R0C1, Т1 = R0C0, Т2 = R1C1.

Резистор R1 введен для предотвращения перегрузки предыдущего каскада и сглаживания шумов, для сглаживания высокочастотных импульсных помех добавлен конденсатор C0. Так как R1 << R0 и C0 << C1, то

Uвых ≈ –  Uвх.

Uвх.

На рис. 2.47ж приведена схема, с помощью которой можно скомпенсировать бóльшую постоянную времени в системах автоматического регулирования и в значительной степени повысить быстродействие.

Схема компаратора (схема сравнения двух напряжений) представлена на рис. 2.47з. Она имеет два устойчивых состояния: при

Uвх – Е > 0, Uвых = – Um , при Uвх – Е < 0, Uвых = Um .

|

Стабилитроны VD1 и VD2 ограничивают напряжение Uвых значением Um, при котором обеспечивается наибольшее быстродействие звена, так как вывод операционного усилителя из насыщения требует значительного времени.

На рис. 2.47и представлена схема, осуществляющая запоминание мгновенного значения напряжения. При замкнутом ключе К на выходе схемы воспроизводится входной сигнал. При размыкании ключа на выходе схемы запоминается мгновенное значение входного сигнала в момент размыкания ключа.

Логические элементы

Это цифровые полупроводниковые устройства, выполненные на базе интегральных микросхем. Они выполняют определенные логические преобразования дискретных сигналов. Каждой комбинации входных сигналов соответствует на выходе сигнал, определяемый заданным правилам. При этом сигналы на входах и выходах могут иметь только два состояния, которым в соответствии с алгеброй логики присваиваются два символа – «1» (логическая единица) и «0» (логический нуль).

В технических и многих других практических приложениях логическая 1 – это знак того, что совершилось какое-то событие или ряд событий: замкнулись контакты и по цепи проходит ток, заработала аппаратура, принято решение, система выдержала испытания и т.д. В противоположность этому логический 0 означает, что контакты разомкнуты, аппаратура не работает, в цепи не проходит ток, проект отвергнут, система не выдержала испытания и т.д. [14].

Логические преобразования таких двоичных сигналов осуществляются на основе трех элементарных операций: ИЛИ – логическое сложение, дизъюнкция; И – логическое умножение, конъюнкция; НЕ – логическое отрицание, инверсия.

Основные логические функции, их элементы и схемы представлены в табл. 2.1 [12].

Число входов по ИЛИ и по И лежит в пределах от 2 до 16. Если имеющегося числа входов недостаточно, то для их увеличения используются интегральные схемы расширителей по ИЛИ, обозначаемые ЛД.

Таблица 2.1

Коэффициент разветвления по выходу характеризует нагрузочную способность логического элемента и определяется количеством входов однотипных элементов, которые можно подключить к выходу. В некоторых случаях в ТУ указывается максимальный выходной ток логического элемента.

Сигнал на выходе логического элемента задерживается относительно входного сигнала. Эта задержка определяет не только быстродействие цифровых схем, но и их работоспособность. Время задержки принято определять по уровню 0,5 U и 0,5 Uвых. При этом задержка переднего фронта и в результате длительность импульса на входе оказывается отличной от длительности импульса на выходе.

Мощность, потребляемая логической ИМС, обычно зависит от сигналов, поданных на входы. Для сравнения потребляемой ИМС мощности пользуются понятием средней мощности Pср, потребляемой базовым логическим элементом во включенном и выключенном состояниях. Это позволяет сравнить по потребляемой мощности логические ИМС различных серий.

|

Логический элемент может иметь один или несколько входов и один выход. Количество возможных комбинаций входных сигналов зависит от количества входов логического элемента и определяется по формуле:

N = 2n,

где N — количество возможных комбинаций входных сигналов; 2 — количество состояний каждого из входов (0 или 1); n — количество входов логического элемента.

В табл. 2.2 показаны операции логических элементов ИЛИ, И, НЕ, а также символические записи соответствующих операций и алгоритмы работы в виде таблиц.

Таблица 2.2

| Операция ИЛИ у = х1 + х2 | Операция И у = х1 · х2 | Операция НЕ у =  |

| Вход 1:Вход 2: Выход | Вход 1:Вход 2: Выход | Вход: Выход |

0  0 = 0 0 0 = 0 0  1 = 1 1 1 = 1 1  0 = 1 1 0 = 1 1  1 = 1 1 = 1 | 0  0 = 0 0 0 = 0 0  1 = 0 1 1 = 0 1  0 = 0 1 0 = 0 1  1 = 1 1 = 1 | 0 = 1 1 = 0 – – |

На практике чаще применяют комбинированные логические элементы, реализующие последовательно выполненные две и более логических операции (см. табл. 2.1).

В настоящее время наибольшее распространение получили логические элементы, выполненные в виде интегральных микросхем (ИМС) на основе биполярных или МОП-транзисторов.

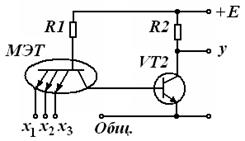

На рис. 2.48 приведен пример схемного решения элемента 3И–НЕ на основе многоэмиттерного транзистора (МЭТ).

Схема работает следующим образом. Если на все входы х1, х2, и х3элемента поданы напряжения, соответствующие уровню 1, то ток эмиттерных переходов МЭТ будет стремиться к нулю. При этом ток через резистор R1 и прямо смещенный переход МЭТ в базу транзистора VT2 достаточно велик и транзистор VT2 полностью открыт. Сопротивление транзистора VT2 (перехода коллектор – эмиттер) в открытом состоянии значительно меньше сопро-

Рис. 2.48. Схема логического элемента 3И–НЕ

тивления последовательно включенного с ним резистора R2. Поэтому почти все напряжение Е, приложенное к последовательной цепи резистор R2 – транзистор VT2, окажется приложенным к резистору R2. На коллекторе VT2, то есть на выходе элемента у, напряжение будет стремиться к нулю. Таким образом, сигнал 0 может быть на выходе такой схемы только при наличии на всех входах сигнала 1.

Микропроцессорные системы

Микропроцессорная система (МС) — это совокупность взаимодействующих больших интегральных схем (БИС) микропроцессорного комплекта, организованная в систему, т. е. вычислительная или управляющая система с микропроцессором в качестве узла обработки информации [15].

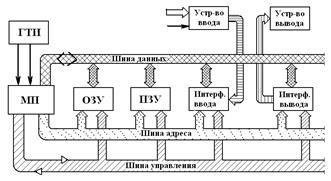

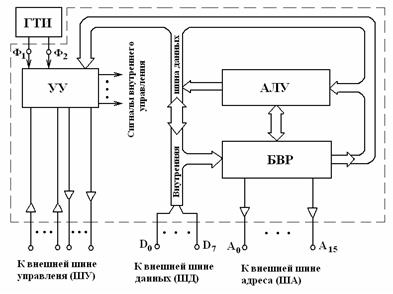

Типовая структура микропроцессорной системы изображена на рис. 2.49.

|

Генератор тактовых импульсов (ГТИ)– источник последовательности прямоугольных импульсов, с помощью которых осуществляется управление событиями во времени. Он задает цикл команды – интервал времени, необходимый для считывания выборки команды из памяти и ее исполнения. Цикл команды состоит из определенной последовательности элементарных действий, называемых состояниями (тактами).

Оперативное запоминающее устройство(ОЗУ), которое иначе называют запоминающим устройством с произвольной выборкой (ЗУПВ) или произвольным доступом (ЗУПД), служит памятью данных, подлежащих обработке, и результатов вычислений, а в некоторых микропроцессорных системах — также программ, которые часто меняются. Его характерное свойство заключается в том, что время, требуемое для доступа к любой из ячеек памяти, не зависит от адреса этой ячейки. ОЗУ допускает как запись, так и считывание слов. По отношению к этому запоминающему устройству приемлема аналогия с классной доской, на которой мелом записаны числа: их можно многократно считывать, не разрушая, а при необходимости – стереть число и записать на освободившемся месте новое. Следует иметь в виду, что информация, содержащаяся в ОЗУ, исчезает, стирается, если прерывается напряжение питания.

Постоянное запоминающее устройство(ПЗУ) — это устройство, в котором хранится программа (и при необходимости совокупность констант). Содержимое ПЗУ не может быть стерто. Оно используется как память программы, составленной заранее изготовителем в соответствии с требованиями ее пользователей. В таких случаях говорят, что программа жестко «зашита» в запоминающем устройстве. Чтобы осуществить иную программу, необходимо применить другое ПЗУ или его часть. Из ПЗУ можно только выбирать хранимые там слова, но нельзя вносить новые, стирать и заменять записанные слова другими. Оно подобно напечатанной таблице выигрышей по облигациям: можно лишь считывать имеющиеся там числа, но заменять их или вносить новые невозможно. Помимо ПЗУ используются также ППЗУ и РППЗУ.

Рис. 2.49. Структура типовой микропроцессорной системы:

ГТИ – генератор тактовых импульсов; МП – микропроцессор;ОЗУ – оперативное запоминающее устройство; ПЗУ – постоянное запоминающее устройство

Программируемое постоянное запоминающее устройство(ППЗУ) отличается от ПЗУ тем, что пользователь может самостоятельно запрограммировать ПЗУ (ввести в него программу) с помощью специального устройства — программатора, но только один раз (после введения программы содержимое памяти уже нельзя изменить).

Репрограммируемое постоянное запоминающее устройство (РППЗУ), называемое также стираемым ПЗУ, имеет такую особенность: хранимая информация может стираться несколько раз (при этом она разрушается). Иначе говоря, РППЗУ допускает перепрограммирование, осуществляемое с помощью программатора. Это облегчает исправление обнаруженных ошибок и позволяет изменять содержимое памяти.

Интерфейсомназывают устройство сопряжения. Под интерфейсом понимают совокупность электрических, механических и программных средств, позволяющих соединять модули системы между собой и с периферийными устройствами. Его составными частями служат аппаратные средства для обмена данными между узлами и программные средства — протокол, описывающий процедуру взаимодействия модулей при обмене данными.

Интерфейс микропроцессорной системы относится к машинным интерфейсам. В микропроцессорной системе применяют специальные интерфейсные БИС для сопряжения периферийных устройств с системой (на рис. 2.49 они показаны в виде модулей интерфейса ввода и интерфейса вывода). Для этих БИС характерна универсальность, осуществляемая путем программного изменения выполняемых ими функций.

Устройство вводаосуществляет введение в систему данных, подлежащих обработке, и команд.

Устройство выводапреобразует выходные данные (результат обработки информации) в форму, удобную для восприятия пользователем или хранения. Устройствами ввода-вывода служат блоки считывания информации с перфоленты и магнитной ленты (или записи на них), кассетные магнитофоны, гибкие диски, клавиатуры, дисплеи, аналого-цифровые и цифро-аналоговые преобразователи, графопостроители, телетайпы и т. п.

Особенность структуры микропроцессорной системы заключается в магистральной организации связей между входящими в ее состав модулями. Она осуществляется с помощью трех шин. По ним передаются вся информация и сигналы, необходимые для работы системы. Эти шины соединяют микропроцессор с внешней памятью (ОЗУ, ПЗУ) и интерфейсами ввода-вывода, в результате чего создается возможность обмена данными между микропроцессором и другими модулями системы, а также передачи управляющих сигналов.

Микропроцессор(МП)представляет собой функционально завершенное универсальное программно-управляемое устройство цифровой обработки данных, выполненное в виде одной или нескольких микропроцессорных БИС. Микропроцессорные БИС относятся к новому классу микросхем, одной из особенностей которого является возможность программного управления работой БИС с помощью определенного набора команд. Эта особенность нашла отражение в программно - аппаратном принципе построения микропроцессорных систем (МС) – цифровых устройств или систем обработки данных, контроля и управления, построенных на базе одного или нескольких МП.

Программно - аппаратный принцип построения МС является одним из основных принципов их организации и заключается в том, что реализация целевого назначения МС достигается не только аппаратными средствами, но и с помощью программного обеспечения – организованного набора программ и данных.

По конструктивному признаку микропроцессоры можно разделить на две разновидности:

- однокристальные микропроцессоры с фиксированной длиной (разрядностью) слова и определенной системой команд;

- многокристальные (секционированные) микропроцессоры с наращиваемой разрядностью слова и микропрограммным управлением, которые составляются из двух и более БИС.

В настоящее время выпускаются также однокристальные микропроцессоры с микропрограммным управлением.

Внутренняя логическая организация однокристальных микропроцессоров в значительной степени подобна организации ЭВМ общего назначения. Это дает возможность при разработке микропроцессорной системы на основе однокристального микропроцессора опираться на методы проектирования и использования обычных ЭВМ малой и средней производительности.

Для примера рассмотрим структуру однокристального универсального восьмиразрядного микропроцессора (рис. 2.50). В состав микропроцессора входят арифметическо-логическое устройство, управляющее устройство и блок внутренних регистров.

Арифметическо-логическое устройство(АЛУ) является ядром микропроцессора, которое, как правило, состоит из двоичного сумматора со схемами ускоренного переноса, сдвигающего регистра и регистров для временного хранения операндов. Это устройство по командам выполняет несколько простейших операций: сложение, вычитание, сдвиг, пересылку, логическое сложение (ИЛИ), логическое умножение (И).

Регистромназывается электронная схема для временного хранения двоичной информации (машинного слова). Ее строят на триггерах, общее число которых определяет разрядность регистра. Каждый триггер регистра используется для ввода, хранения и вывода одного разряда (1 или 0) двоичного числа. Разрядность регистра выбирают соответственно длине хранимого в нем слова.

Рис. 2.50. Структура однокристального восьмиразрядного

микропроцессора

Регистры, которые служат только для ввода, хранения и вывода двоичной информации, называют накопительными. От них отличаются сдвигающие регистры, которые помимо выполнения указанных функций позволяют осуществлять сдвиг двоичного числа вправо или влево (а иногда – в обоих направлениях). Если в накопительный регистр вводят числа в параллельном коде, т. е. одновременно во все триггеры, то ввод чисел в сдвигающий регистр часто производят в последовательном коде, подавая последовательно один разряд за другим, хотя возможен и вод чисел в параллельном коде.

Триггер – это устройство, обладающее двумя устойчивыми состояниями 0 и 1, способное под воздействием внешнего управляющего сигнала скачком переходить из одного состояния в другое [11].

|

Операндом называют число или символ, участвующие в машинной операции. Так, в выражении у = а + b или ω = 2k - 1 операнды – это а, b, 2, k, 1. Типичным примером операнда, используемого при процедуре обработки данных микропроцессором, служит байт.

В вычислительной технике вообще и микропроцессорной технике в частности, имеющими дело с числами, широко используются такие термины, как «бит», «слово», «байт».

Бит – это разряд двоичного числа: 0 или 1. Так, 0101 – четырехбитовое двоичное число, причем крайняя левая цифра представляет старший разряд данного числа, а крайняя правая – младший разряд. Четырехбитовое двоичное число называется тетрадой, а трехбитовое – триадой.

Слово – законченная последовательность символов (нулей и единиц) определенной длины или сигналов, представляющих эти символы. Машинное слово – специальная последовательность нулей и единиц, которая может быть прочитана или интерпретирована ЭВМ данного типа. Иначе говоря, машинное слово — это группа битов, которую обрабатывает ЭВМ за один шаг. В общем случае слово имеет переменную длину. Число двоичных разрядов (битов) в слове может находиться в пределах 1 ≤ z ≤ n . Величина п зависит от технических возможностей ЭВМ. Обычно под длиной машинного слова понимают число битов, хранимых в одном регистре ЭВМ. В технике больших ЭВМ иногда словом называют последовательность из 32 бит, полусловом — из 16 бит и двойным словом — из 64 бит. Для микропроцессорной техники основополагающим является байт. По отношению к нему определяется формат данных.

Байт – восьмибитовое слово, рассматриваемое как единица для обмена цифровой информацией между устройствами микропроцессорной системы.

Устройство управления (УУ) «руководит» работой АЛУ и внутренних регистров в процессе выполнения команды. Согласно коду операции, содержащемуся в команде, оно формирует внутренние сигналы управления блоками микропроцессора. Адресная часть команды совместно с сигналами управления используется для считывания данных из определенной ячейки памяти (записи данных в ячейку). По сигналам УУ осуществляется выборка каждой новой, очередной команды.

|

Блок внутренних регистров (БВР), расширяющий возможности АЛУ, служит внутренней памятью микропроцессора – используется для временного хранения данных и команд. Он также выполняет некоторые процедуры обработки информации. Обычно этот блок содержит регистры общего назначения и специальные регистры: регистр-акку-мулятор, буферный регистр адреса, буферный регистр данных, счетчик команд, регистр команд, регистры стека, регистр признаков [15].

На практике нередко применяют функциональный блок, содержащий микропроцессорный комплект и оформленный конструктивно в виде платы. Он может выполнять функции микро-ЭВМ, встраиваемой в измерительный прибор или другую аппаратуру (без источника питания, корпуса, пульта управления, периферийных узлов), но не способной работать как самостоятельное, автономное устройство. Такой блок, выполняющий функции управления, называютмикроконтроллером. Иногда для сокращения его называют простоконтроллером. Он может быть программируемым и непрограммируемым. Контроллеры для измерительных систем выпускают и в виде автономных устройств.

Программно-технические комплексы. В настоящее время автоматизация большинства технологических процессов осуществляется на базе универсальных микропроцессорных контроллерных средств, которые в России получили название программно-технических комплексов (ПТК) [16]. Они представляют собой совокупность микропроцессорных средств автоматизации (микропроцессорных контроллеров, устройств связи с объектом УСО), дисплейных пультов оператора и серверов различного назначения, промышленных сетей, которые позволяют связать перечисленные компоненты, программное обеспечение контроллеров и дисплейных пультов оператора. ПТК предназначены, в первую очередь, для создания распределенных систем управления технологическими процессами различной информационной мощности (от десятков входных/выходных сигналов до сотни тысяч).