Подключение светодиодов, кнопок и переключателей стенда Altera DE 2

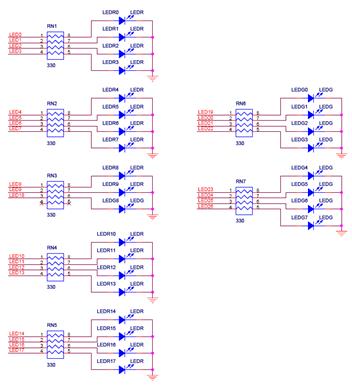

Как уже отмечалось ранее, на плате DE2 установлены 27 светодиодов, восемнадцать красных и девять зеленых. Каждый светодиод подключен непосредственно к выводам ПЛИС Cyclone FPGA. Установка на выводе ПЛИС логической единицы (сигнала высокого уровня) включает светодиод, а логический ноль (сигнала низкого уровня) выключает его. Схема подключения светодиодов изображена на рисунке 4, а имена цепей и выводов ПЛИС приведены в таблице 1.

|

Рисунок 4 – Схема электрическая принципиальная подключения светодиодов

Таблица 1. Имена цепей и выводов ПЛИС

| Имя цепи | Имя вывода ПЛИС | Позиционное обозначение |

| LEDR[0] | PIN_AE23 | LED Red[0] |

| LEDR[1] | PIN_AF23 | LED Red[1] |

| LEDR[2] | PIN_AB21 | LED Red[2] |

| LEDR[3] | PIN_AC22 | LED Red[3] |

| LEDR[4] | PIN_AD22 | LED Red[4] |

| LEDR[5] | PIN_AD23 | LED Red[5] |

| LEDR[6] | PIN_AD21 | LED Red[6] |

| LEDR[7] | PIN_AC21 | LED Red[7] |

| LEDR[8] | PIN_AA14 | LED Red[8] |

| LEDR[9] | PIN_Y13 | LED Red[9] |

| LEDR[10] | PIN_AA13 | LED Red[10] |

| LEDR[11] | PIN_AC14 | LED Red[11] |

| LEDR[12] | PIN_AD15 | LED Red[12] |

| LEDR[13] | PIN_AE15 | LED Red[13] |

| LEDR[14] | PIN_AF13 | LED Red[14] |

| LEDR[15] | PIN_AE13 | LED Red[15] |

| LEDR[16] | PIN_AE12 | LED Red[16] |

| LEDR[17] | PIN_AD12 | LED Red[17] |

| LEDG[0] | PIN_AE22 | LED Green[0] |

| LEDG[1] | PIN_AF22 | LED Green[1] |

| LEDG[2] | PIN_W19 | LED Green[2] |

| LEDG[3] | PIN_V18 | LED Green[3] |

| LEDG[4] | PIN_U18 | LED Green[4] |

| LEDG[5] | PIN_U17 | LED Green[5] |

| LEDG[6] | PIN_AA20 | LED Green[6] |

| LEDG[7] | PIN_Y18 | LED Green[7] |

| LEDG[8] | PIN_Y12 | LED Green[8] |

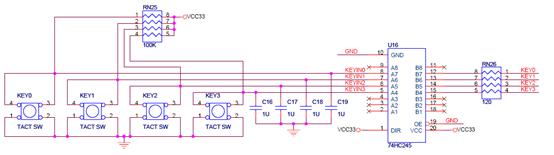

На плате DE2 установлены 4 кнопки (без фиксации), включенные по антидребезговой схеме, которые подают на выводы ПЛИС логическую единицу (+3.3В) при отжатом состоянии и логический ноль при нажатом состоянии. Схема подключения кнопок изображена на рисунке 5, а имена цепей и выводов ПЛИС приведены в таблице 2.

|

Рисунок 5 – Схема электрическая принципиальная подключения кнопок

Продолжение таблицы 1. Имена цепей и выводов ПЛИС

| Имя цепи | Имя вывода ПЛИС | Позиционное обозначение |

| KEY[0] | PIN_G26 | Pushbutton[0] |

| KEY[1] | PIN_N23 | Pushbutton[1] |

| KEY[2] | PIN_P23 | Pushbutton[2] |

| KEY[3] | PIN_W26 | Pushbutton[3] |

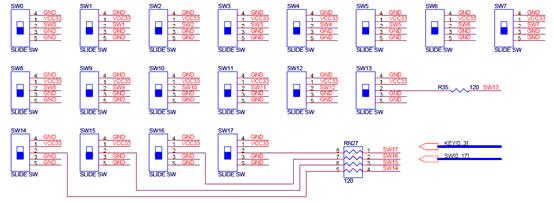

18 переключателей, установленных на плате DE2, не являются противодребезговыми, и предназначены для ввода данных на схему. Каждый выключатель связан непосредственно с выводом ПЛИС Cyclone II FPGA. Когда переключатель находится в положении “ВНИЗ” (наиболее близкий к краю платы), на выводах ПЛИС установлен сигнал низкого логического уровня (0В), а если переключатель перевести в положение “ВВЕРХ”, то на выводах установится высокий логический уровень (3.3В). Схема подключения переключателей изображена на рисунке 6, а имена цепей и выводов ПЛИС приведены в таблице 3.

|

Рисунок 6 – Схема электрическая принципиальная подключения переключателей

Продолжение таблицы 1. Имена цепей и выводов ПЛИС

| Имя цепи | Имя вывода ПЛИС | Позиционное обозначение |

| SW[0] | PIN_N25 | Toggle Switch[0] |

| SW[1] | PIN_N26 | Toggle Switch[1] |

| SW[2] | PIN_P25 | Toggle Switch[2] |

| SW[3] | PIN_AE14 | Toggle Switch[3] |

| SW[4] | PIN_AF14 | Toggle Switch[4] |

| SW[5] | PIN_AD13 | Toggle Switch[5] |

| SW[6] | PIN_AC13 | Toggle Switch[6] |

| SW[7] | PIN_C13 | Toggle Switch[7] |

| SW[8] | PIN_B13 | Toggle Switch[8] |

| SW[9] | PIN_A13 | Toggle Switch[9] |

| SW[10] | PIN_N1 | Toggle Switch[10] |

| SW[11] | PIN_P1 | Toggle Switch[11] |

| SW[12] | PIN_P2 | Toggle Switch[12] |

| SW[13] | PIN_T7 | Toggle Switch[13] |

| SW[14] | PIN_U3 | Toggle Switch[14] |

| SW[15] | PIN_U4 | Toggle Switch[15] |

| SW[16] | PIN_V1 | Toggle Switch[16] |

| SW[17] | PIN_V2 | Toggle Switch[17] |