Устройство генерации адресов (AGU) и режимы адресации.

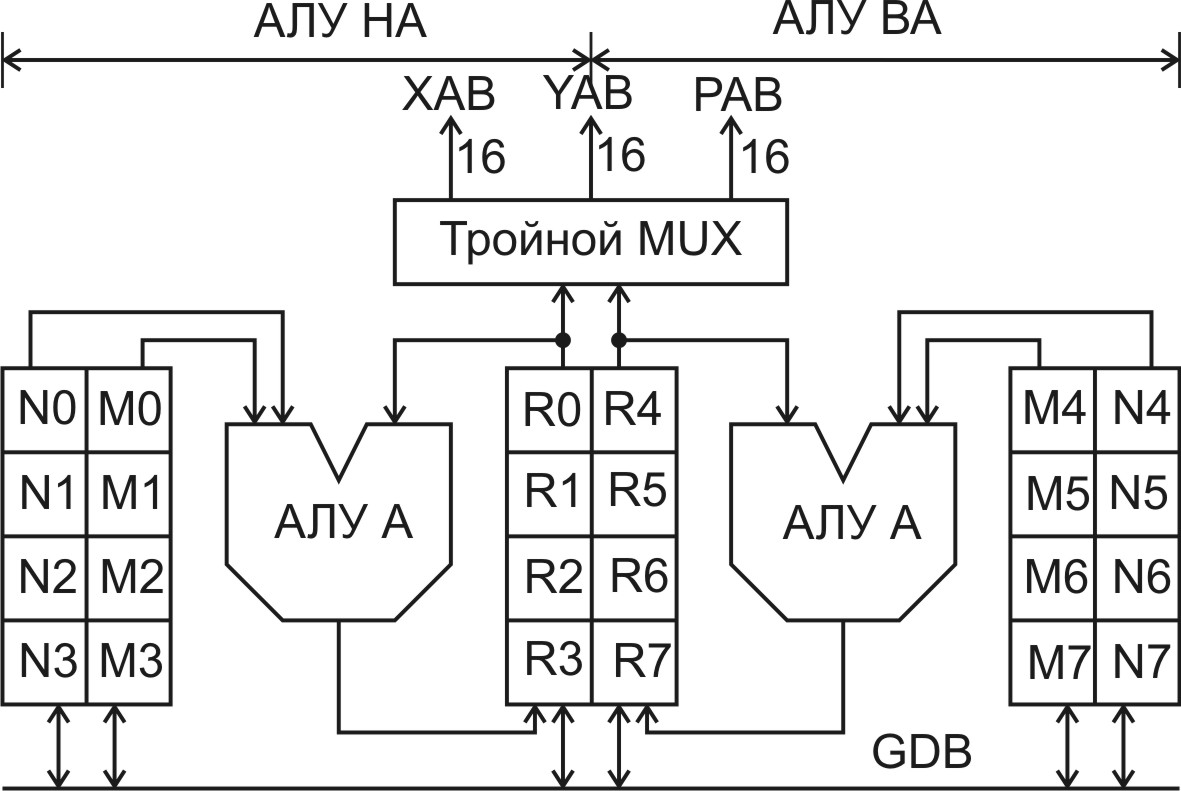

На рисунке 5.7. показаны структура AGU.

Все регистры AGU являются 24 разрядными, в которых 16 младших разрядов являются значащими. Старшие 8 бит всегда равны 0 и при записи не модифицируются.

АЛУ А – АЛУ адреса; АЛУ ВА – АЛУ верхних адресов; АЛУ НА – АЛУ нижних адресов

Рисунок 5.7 – Структура AGU

5.3.2.1 Блок регистров адреса R0-R7

Блок данных регистров состоит из двух подблоков регистров адреса, каждый из которых содержит четыре 16-ти битных регистра, которые содержат адреса для обращения к памяти. Каждый регистр может быть записан или прочитан через глобальную шину данных. Каждый адресный регистр может использоваться как вход АЛУ адресов для модификации регистров. Если параллельно осуществляется пересылка данных из памяти Х и из памяти У, то адресные регистры разделяются на два блока R0 – R3 и R4 – R7 соответственно.

5.3.2.2 Блок регистров смещения N0-N7

Данные регистры жестко привязаны к регистрам R в соответствии с номерами и так же разбиваются на два подблока. Регистры хранят смещение, которое используется для модификации адреса. Любой из регистров смещения может быть записан или прочитан через глобальную шину данных.

5.3.2.3 Блок регистров модификации М0-М7

Каждый из двух подблоков регистров модификации содержит четыре 16-ти битных регистра, которые определяют тип адресной арифметики для вычисления модификации регистров адреса R. Имеется так же жесткая привязка к регистрам R по номерам. Каждый из регистров М может быть прочитан или записан через глобальную шину данных. После сброса процессора все регистры модификации хранят число FFFF, что определяет линейный режим модификации адреса.

5.3.2.4 АЛУ адресов

Два идентичных АЛУ адресов рассчитывают 16-ти битный полный адрес, который может быть инкрементирован, декрементирован или выполнены сложные вычисления с использованием регистра смещения в соответствии с выбранным режимом адресации. DSP данного семейства обеспечивает 3 различных типа адресации:

прямую регистровую

косвенную регистровую

специальную регистровую.

При косвенной адресации возможны следующие модификации:

без модификации - адрес операнда содержится в регистре адреса Rn и не изменяется после выполнения команды;

постинкремент - адрес операнда содержится в регистре адреса Rn и после выполнения команды инкрементируется;

постдекремент - адрес операнда содержится в регистре адреса Rn и после выполнения команды декрементируется;

постинкремент со смещением Nn; после использования содержимое регистра R суммируется с содержимым регистра N и сохраняется в регистре R. Содержимое регистра N при этом не изменяется; Rn=Rn+Nn ;

постдекремент со смещением Nn; Rn= Rn - Nn ;

индексный со смещением Nn – адрес операнда находится как сумма регистров R и N; содержимое регистров R и N не изменяется;

предекремент; адрес, хранящийся в R, декрементируется до начала выполнения команды и сохраняется в нем же;

специальные типы модификации адреса АЛУ, которые позволяют существенно упростить создание структур данных в памяти для очередей, линий задержки, циклических буферов, стеков.

5.3.2.5 Линейный модификатор

Включается если в регистр М загружено число FFFF. В этом случае используется нормальная, 16-ти битная линейная арифметика. При вычислении адреса используется 16-ти битное смещение N инкремент и декремент. Диапазон смещения для знаковых чисел от – 32768 до 32767 и от 0 до 65535 для без знаковых чисел. Поддерживается переполнение, как через верхнюю границу, так и через нижнюю. Для верхней границы из суммы вычитается 65536, для нижней границы к разнице надо прибавить 65536.

5.3.2.6 Модульный модификатор

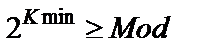

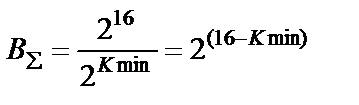

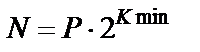

Включается, если в регистр М загружено число от 1 до 32767. Модуль рассчитывается как число из регистра М+1. При включении модульного модификатора в памяти данных создается множество буферов размером равным модулю. Причем модуль однозначно определяет нижнюю и верхнюю границу всех буферов. Нижняя граница или базовый адрес буфера определяется из неравенства

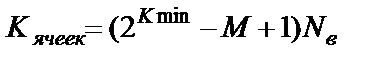

,

,

где Mod – модуль;

К – количество младших разрядов, которые всегда будут равны 0 у всех базовых адресов.

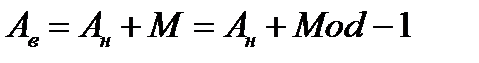

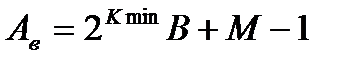

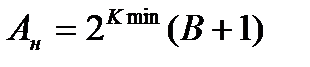

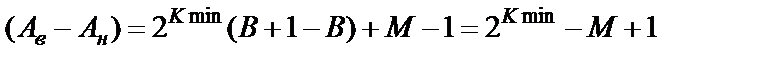

Верхняя граница рассчитывается как

,

,

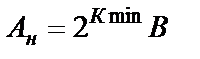

где  ;

;

В – номер буфера.

Количество буферов

.

.

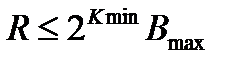

Процессор из всего множества созданных в памяти буферов работает только с одним из них, а именно с тем, в который попадает регистр R. Если регистр R попадает между буферами, то процессор попадает в сбойный режим. При выборе конкретного буфера регистр R может модифицироваться только в пределах этого буфера, за исключением специального случая, когда имеет место постинкремент или постдекремент со смещением, и регистр N равен

,

,

где P-целое число.

В этом случае регистр R переходит из одного циклического буфера в другой, отстоящий от первого на P буферов. Для определения номера активного буфера используются следующие соображения

.

.

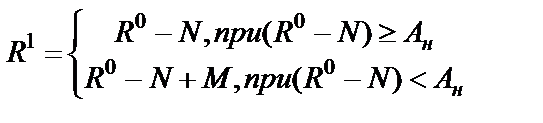

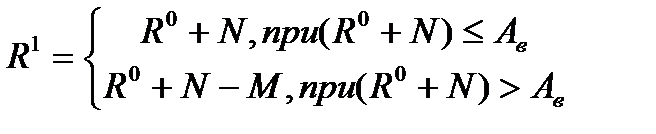

Ввиду того, что за исключением специального случая регистр R модифицируется внутри активного буфера, происходит переполнение, как через верхнюю, так и через нижнюю границу буфера. При постдекременте со смещением новое значение R рассчитывается по формулам

.

.

При постинкременте:

;

;

;

;

.

.

Количество брошенных ячеек

;

;

.

.

5.3.2.7 Модификатор реверсивного переноса

Данный режим включается, если в регистр М загружено число 0. Модификация адреса в этом режиме осуществляется путем реализации на аппаратном уровне переноса на арифметических операциях в обратном направлении от старших битов к младшим.

Для ручного вычисления адреса применяют следующий алгоритм. Выполняется реверсия обоих операндов, затем выполняется сложение или вычитание по обычным правилам, после чего выполняется реверсия результата. Под реверсией понимают разворот числа таким образом, что младший бит становится старшим, а старший - младшим.

Модификатор реверсивного переноса используется для эффективного вычисления адресов при реализации алгоритма БПФ с прореживанием по времени.

Программный контроллер

Программный контроллер обеспечивает предварительную выборку инструкций, декодирование инструкций, управление аппаратными циклами и обработку исключений. Контроллер содержит 15-уровневый 32-разрядный системный стек и шесть непосредственно адресуемых регистров:

- программный счетчик PC (Program Counter);

- регистр адреса цикла LA (Loop Address);

- счетчик петли LC (Loop Counter);

- регистр статуса SR (Status Register);

- регистр режима операций OMR (Operating Mode Register);

- указатель стека SP (Stack Pointer).

Системный стек представляет собой отдельный блок внутренней памяти, используемый для хранения регистра статуса и программного счетчика при вызовах подпрограмм и длительных прерываниях. В стеке также хранятся LA и LC при организации аппаратных циклов. Все эти регистры могут быть прочитаны или записаны через внутрисхемный эмулятор для упрощения отладки системы. Конвейер программного контроллера имеет три уровня, каждый из которых выполняет параллельно одно действие. Первый уровень отвечает за считывание следующей команды, второй уровень за декодирование, третий за выполнение. Таким образом, за один машинный цикл виртуально команда считывается, декодируется и выполняется одновременно. Нарушение работы конвейера происходит, если в программе встречается команда условного ветвления. Процессор всегда в конвейер считывает команду следующую при условии верности условия.

5.3.3.1 Структура программного контроллера

Программный контроллер состоит из трех аппаратных блоков:

- контроллера декодирования программ (PDC);

- генератора адресов программ (PAG);

- контроллера прерываний (PIC).

Контроллер декодирования программ включает в себя программную логику для декодирования команд, генератор адреса регистра, механизм выполнения циклов, механизм выполнения повторений, генератор кодов условий, механизм выполнения прерываний, регистр-защелку инструкций и его копию.

Генератор адресов программ содержит все регистры программного контроллера и системный стек. Циклы, являющиеся основной конструкцией алгоритмов цифровой обработки сигналов, поддерживаются аппаратно. С точки зрения программиста достаточно указать количество повторений цикла и его границы. После чего выполнить соответствующую команду начала цикла. На аппаратном уровне в регистр LC загружается количество повторений цикла, в регистр LA адрес последней команды цикла, а в регистре статуса автоматически устанавливается флаг инициализации цикла. После этого цикл автоматически повторяется LC раз. Механизм повторений позволяет ускорить процессы пересылки большого объема информации путем автоматического, аппаратного повторения LC раз одной и той же команды. При этом экономится время на считывание и декодирование команды. Из-за особенностей механизма повторений в процессе его реализации отключается механизм прерываний.

Контроллер прерываний принимает все запросы прерываний, осуществляет арбитраж в каждом цикле и генерирует адрес вектора прерывания. Прерывания могут вызывать четыре внешних и шестнадцать внутренних источников прерываний.

Используется структура гибкого приоритета прерываний. Каждое прерывание получает свой уровень приоритета (IPL), от 0 до 3. Уровни 1 и 2 могут маскироваться. При арбитраже к исполнению выбирается прерывание с максимальным уровнем приоритета. В таблице 5.1 указаны источники прерываний и их уровни приоритета.

Таблица 5.1 - Источники прерываний и их уровни приоритета

| Стартовый адрес | IPL | Источник |

| P:$0000/P:$E000 | Аппаратный внешний сброс | |

| P:$0002 | Ошибка стека | |

| P:$0004 | Трассировка | |

| P:$0006 | Программное прерывание SWI | |

| P:$0008 | 0-2 | Внешнее прерывание IRQA |

| P:$000A | 0-2 | Внешнее прерывание IRQB |

| P:$000C | 0-2 | Приемник данных SSI |

| P:$000E | 0-2 | Приемник данных в состоянии исключения SSI |

| P:$0010 | 0-2 | Передатчик данных SSI |

| P:$0012 | 0-2 | Передатчик данных в состоянии исключения SSI |

| P:$0014 | 0-2 | Приемник данных SCI |

| P:$0016 | 0-2 | Приемник данных в состоянии исключения SCI |

| P:$0018 | 0-2 | Передатчик данных SCI |

| P:$001A | 0-2 | Простой линии SCI |

| P:$001C | 0-2 | Таймер SCI |

| P:$001E | NMI, зарезервировано для разработок | |

| P:$0020 | 0-2 | Приемник данных Host |

| P:$0022 | 0-2 | Передатчик данных Host |

| P:$0024 | 0-2 | Команда Host |

| P:$0026 | 0-2 | Доступно для команд Host |

| P:$0028 | 0-2 | Доступно для команд Host |

| P:$002A | 0-2 | Доступно для команд Host |

| P:$002C | 0-2 | Доступно для команд Host |

| P:$002E | 0-2 | Доступно для команд Host |

| P:$0030 | 0-2 | Доступно для команд Host |

| P:$0032 | 0-2 | Доступно для команд Host |

| P:$0034 | 0-2 | Доступно для команд Host |

| P:$0036 | 0-2 | Доступно для команд Host |

| P:$0038 | 0-2 | Доступно для команд Host |

| P:$003A | 0-2 | Доступно для команд Host |

| P:$003C | 0-2 | Доступно для команд Host |

| P:$003E | 0-2 | Неправильная инструкция |

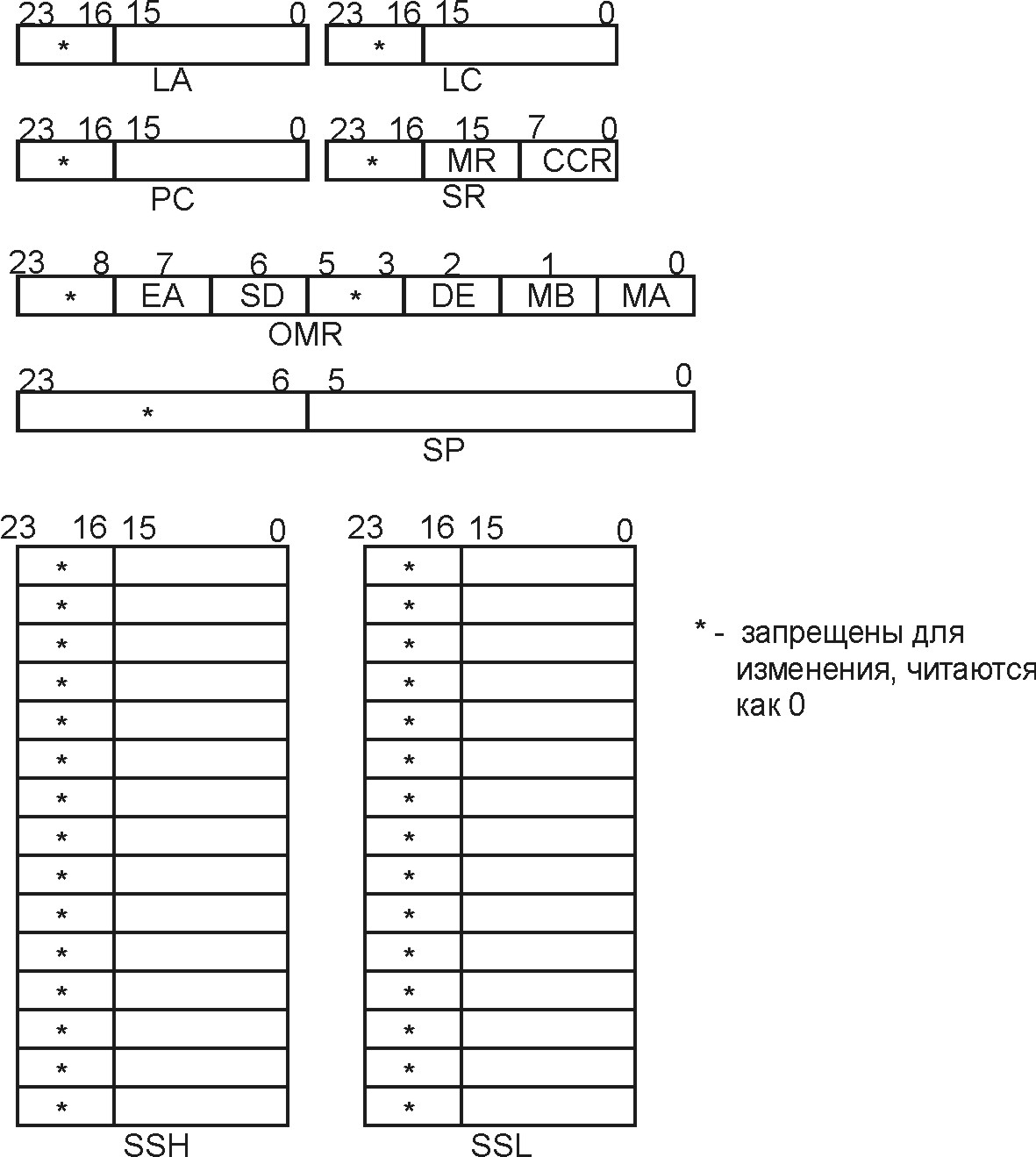

При наступлении прерывания процессор делает переход по указанному адресу для каждого прерывания. Если по этому адресу стоит однословная команда, то она выполняется, и прерывание автоматически завершается. Если команда двухсловная, то процессор входит в режим длинного прерывания и в этом случае в стек дополнительно к адресу возврата сохраняется регистр статуса. Программная модель программного контроллера показана на рисунке 5.8.

Рисунок 5.8 – Программная модель программного контроллера

Стек состоит из пятнадцати парных ячеек, т.к. в стек обычно сохраняется адрес и регистр статуса. Ввиду того, что стек ограничен по размерам, необходимо тщательно отслеживать, чтобы не произошло переполнение стека.

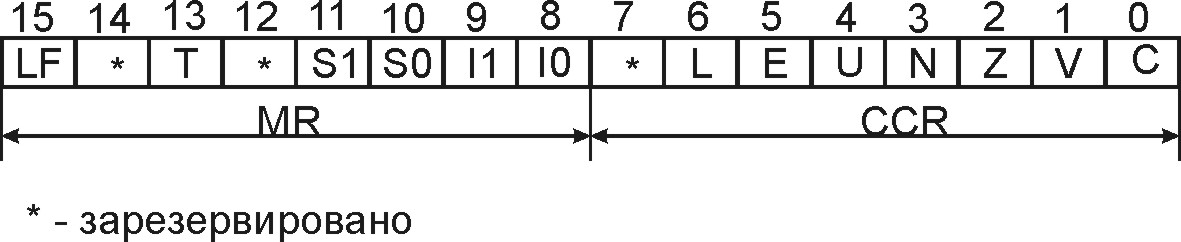

SP - указатель стека. Ввиду ограниченного объема стека (всего 30 ячеек памяти) значащими являются только 6 младших бит (0-5). SR- регистр статуса, состоит из двух частей (рисунок 5.9): регистра режима MR и регистра кодов условий CCR.

Рисунок 5.9 – Структура регистра статуса

Регистр кодов условий CCR определяет текущее состояние процессора для пользователя. После сброса все его биты равны 0.

Бит 0 – С, флаг переноса.

Бит 1 – V, флаг переполнения. Устанавливается при переполнении 56-разрядного результата.

Бит 2 – Z, флаг 0.

Бит 3 – N, флаг минуса, если результат отрицательный, то флаг равен - 1.

Бит 4 – U, флаг денормализации, устанавливается в 1, если 2 старших бита равны.

Бит 5 – E, флаг расширения, обращается в 0, если 8 битов старшей части аккумулятора все равны 0 или 1.

Бит 6 – L, флаг ограничения, устанавливается при выполнении сдвига ограничения в АЛУ данных.

S1 – S0, данные биты определяют режим масштабирования для устройства сдвига ограничения данных АЛУ и позиции округления для MAC.

Бит 13 – Т, бит трассировки, если бит равен 1, то после выполнения каждой команды процессор останавливается и ждет разрешения на выполнение следующей команды от внутрисхемного эмулятора.

Бит 15 – флаг LF, бит становится равным 1 при выполнении цикла, после завершения цикла сам сбрасывается в 0.

5.3.3.2 Регистр операционного режима (OMR)

В данном регистре используется только 5 битов из 24. Биты МА и МБ, нулевой и первый, определяют, какая карта памяти будет использоваться в процессоре. Изменяя их содержимое по ходу можно переключаться между внутренним и внешним ПЗУ и т.п. После сброса данные биты копируют состояние со специальных входов процессора.

Бит 2 – DE, разрешение ПЗУ данных. Если бит установлен, то становится активным внутреннее ПЗУ данных в областях памяти X и Y.

Бит 6 – SD, при выходе из состояния останова, если этот бит равен 0, генерируется задержка длительностью 31072 периода тактовой частоты, если бит установлен в 1, задержка составляет 16 периодов. Длительная задержка в некоторых случаях необходима для стабилизации синхронизации.

Бит 7 – EA, бит определяет функции 2-х линий порта А, что влияет на режим обращения к внешней памяти.

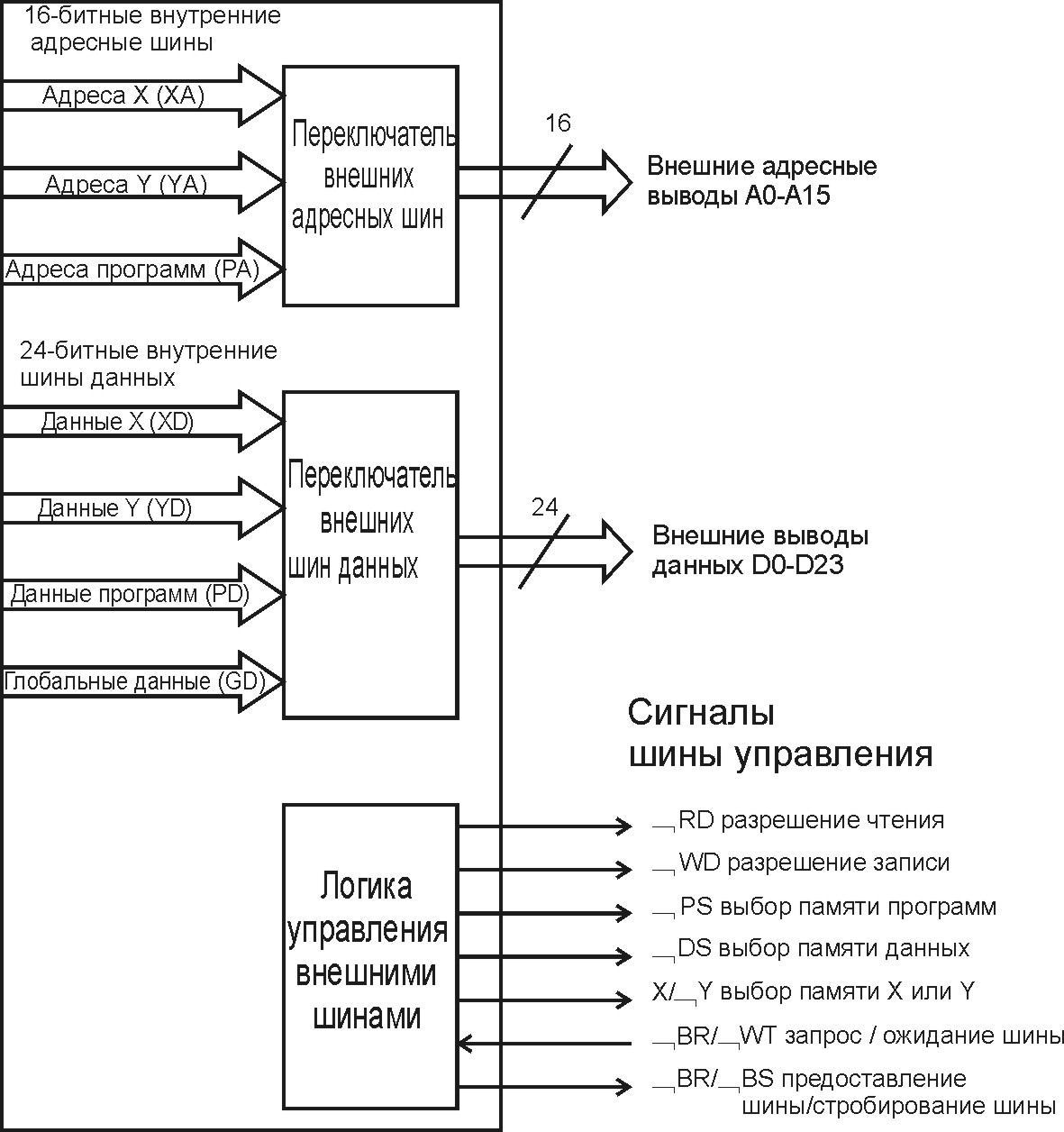

Порт А

На рисунке 5.10 приведена структура Порта А.

Рисунок 5.10 – Структура Порта А

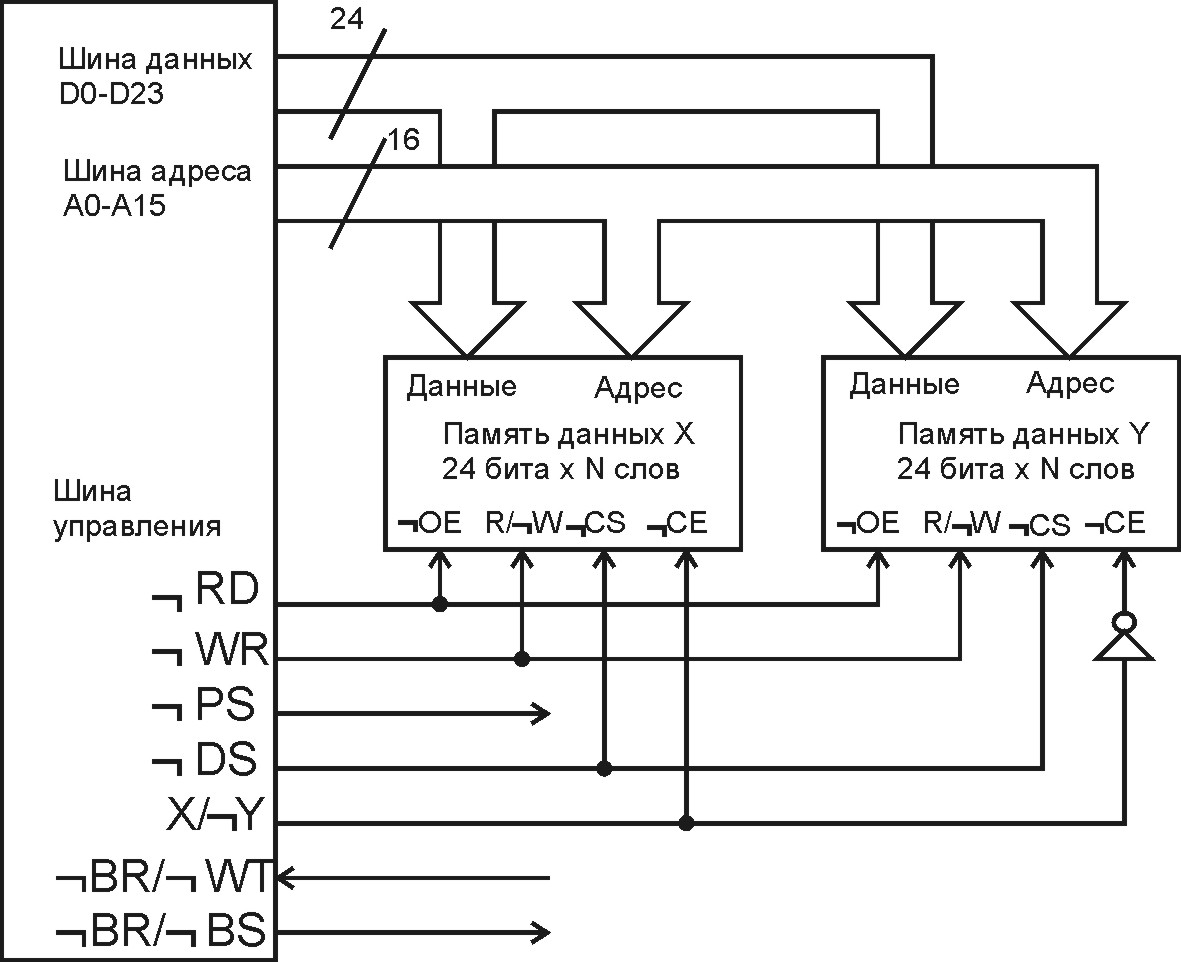

Порт А используется для подключения к DSP процессору внешних блоков памяти и различных периферийных устройств. Типичная схема подключения внешних блоков памяти Х и Y приведена на рисунке 5.11.

Рисунок 5.11 – Типичная схема подключения внешних блоков памяти Х и Y через порт А

Таймер DSP56002

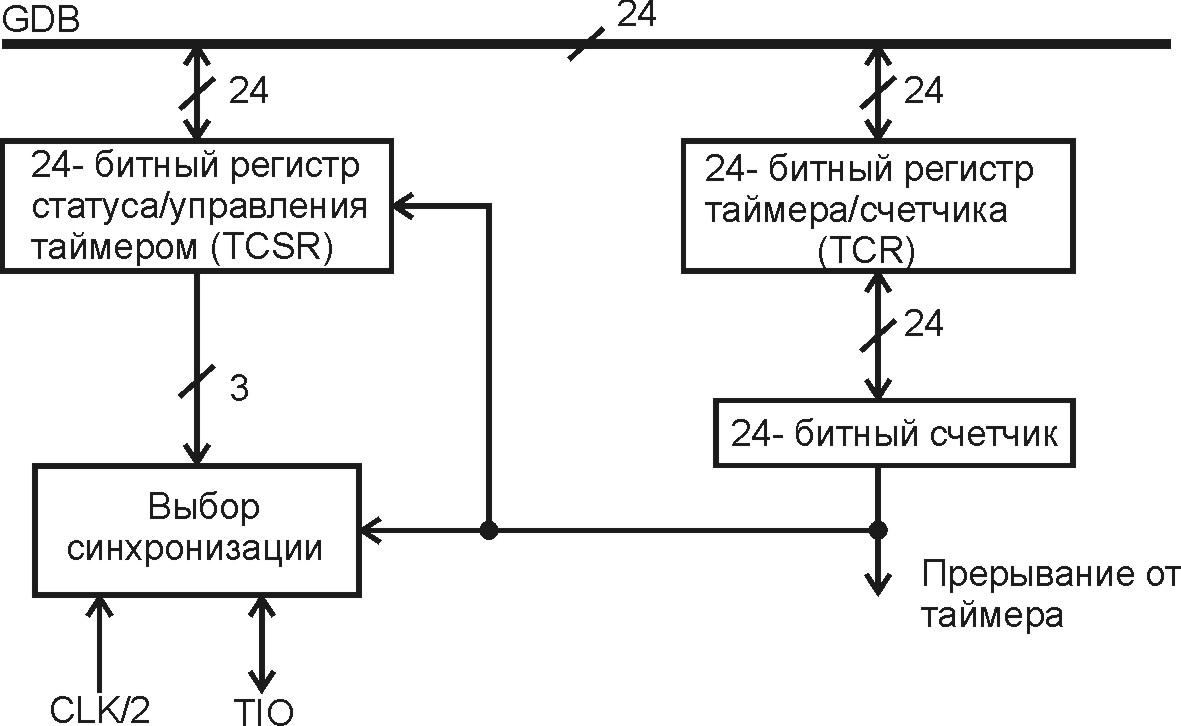

Таймер DSP процессора может использовать внутреннюю или внешнюю синхронизацию и может прерывать работу процессора по наступлению переполнения или выдавать сигнал внешним устройствам после подсчёта внутренних событий.

Важную роль в работе таймера играет двунаправленная линия TIO. Данная линия может выполнять три функции:

1. ввод/вывод общего назначения;

2. вход таймерного модуля, в этом случае таймер работает как счётчик внешних событий на входе TIO;

3. выход таймерного модуля, на который выдаются пульсации таймера.

На рисунке 5.12 приведена структурная схема таймерного модуля. Таймерный модуль включает в себя 24-битный регистр статуса/управления таймером, 24-битный регистр таймера/счётчика, логику выбора синхронизации и генерации прерывания.

Рисунок 5.12 – Структура таймера