Обзор архитектуры и шинной организации DSP 560xx

5.3.1.1 Общая характеристика

Высокая производительность DSP данного семейства позволяет использовать их в области коммуникации, высокоскоростного управления, компьютерных приложениях и аудиоприложениях. Для всех DSP основной операцией является умножение и суммирование двух многоразрядных чисел с плавающей точкой. Данная операция получила название МАС. Эта операция внутри DSP выполнятся за 1 машинный цикл при расположении операндов в разных областях памяти.

Основу процессора составляют три параллельно работающих устройства:

- Арифметико-логическое устройство;

- устройство генерации адреса;

- программный контролер.

В DSP данного семейства имеется трехступенчатый аппаратный конвейер инструкций.

Структура шин

Шины данных являются 24-х разрядными. Шины данных X и Y могут объединяться в 48 разрядную шину. Дополнительно может использоваться глобальная шина данных, например, при обращении к периферийным модулям. Структура шин поддерживает пересылку данных 3-х типов: регистр - регистр; регистр - память; память - регистр.

Всего поддерживается организация данных 24 бита, 48 битов, 56 битов.

Шины адреса являются 16-ти разрядными. Пространство внешней памяти адресуется с помощью однонаправленной 16-ти разрядной шины адреса с 3-мя состояниями, к которой может подключаться одна из 3-х внутренних шин адреса.

В одном машинном цикле может быть произведен только один доступ к внешней шине данных.

5.3.1.2 Арифметико-логическое устройство данных

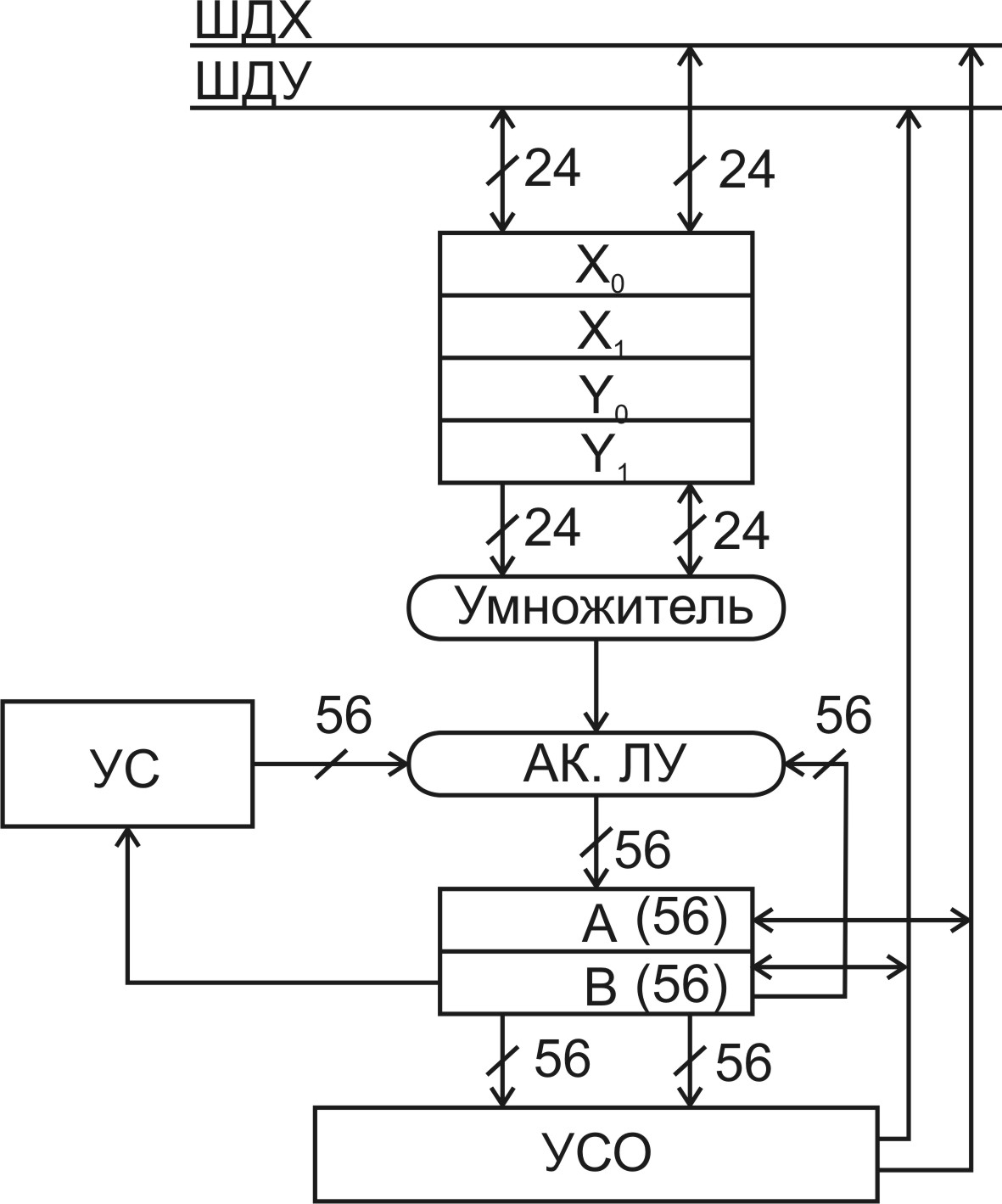

На рисунке 5.3 показана структурная схема АЛУ данных.

X0, X1, Y0, Y1 - буферные регистры; АК. ЛУ – аккумулятор логического устройства; УС – устройство сдвига; А, В – аккумуляторы процессора; ШДХ - шина данных Х; УСО – устройство сдвига-ограничения

Рисунок 5.3 – Структура АЛУ данных

АЛУ данных позволяет выполнять в одном машинном цикле следующие действия: умножение, итерационное деление, нормализация, сдвиги, поразрядные логические операции.

Регистры АЛУ данных могут быть прочитаны или записаны 24-х или 48-ми разрядными операндами. Операнды источники могут быть 24-х, 48 и 56 – разрядные. Результаты любой операции всегда сохраняются в аккумуляторе.

Буферные регистры X0, X1, Y0, Y1 могут использоваться как независимые 24-х битные регистры или как два 48-ми разрядных регистра X и Y, образованные объединением X0 с X1 и Y0 с Y1 соответственно.

Умножитель способен обрабатывать до 3-х операндов одновременно, и выдает 56-ти разрядный результат в следующем формате: 8-ми битное расширение, 24-х битная старшая значащая часть, 24-х битная младшая значащая часть.

Каждый из аккумуляторов А и В образуется из 3-х регистров. Регистры А2 и В2 – 8-ми битное расширение, А1 и В1 – старшая значащая часть, А0 и В0 – младшая значащая часть. Восьми битные регистры расширения предназначены для защиты от переполнения. В DSP 560хх диапазон значений операндов составляет от –1 до 0,9999998. В случае выхода результата за границы диапазона возникает переполнение, которое позволяет учесть регистр расширения. Самый старший бит регистра расширения является знаковым.

Асинхронное параллельное устройство сдвига может выполнять следующие операции: обнуление всех битов, ротация вправо и влево, арифметические и логические сдвиги вправо и влево, нет сдвига. Устройство сдвига-ограничения используется для того, чтобы иметь возможность полученный 56-ти разрядный результат сохранить во внешней памяти через 24-х или 48-ми разрядную шину данных.

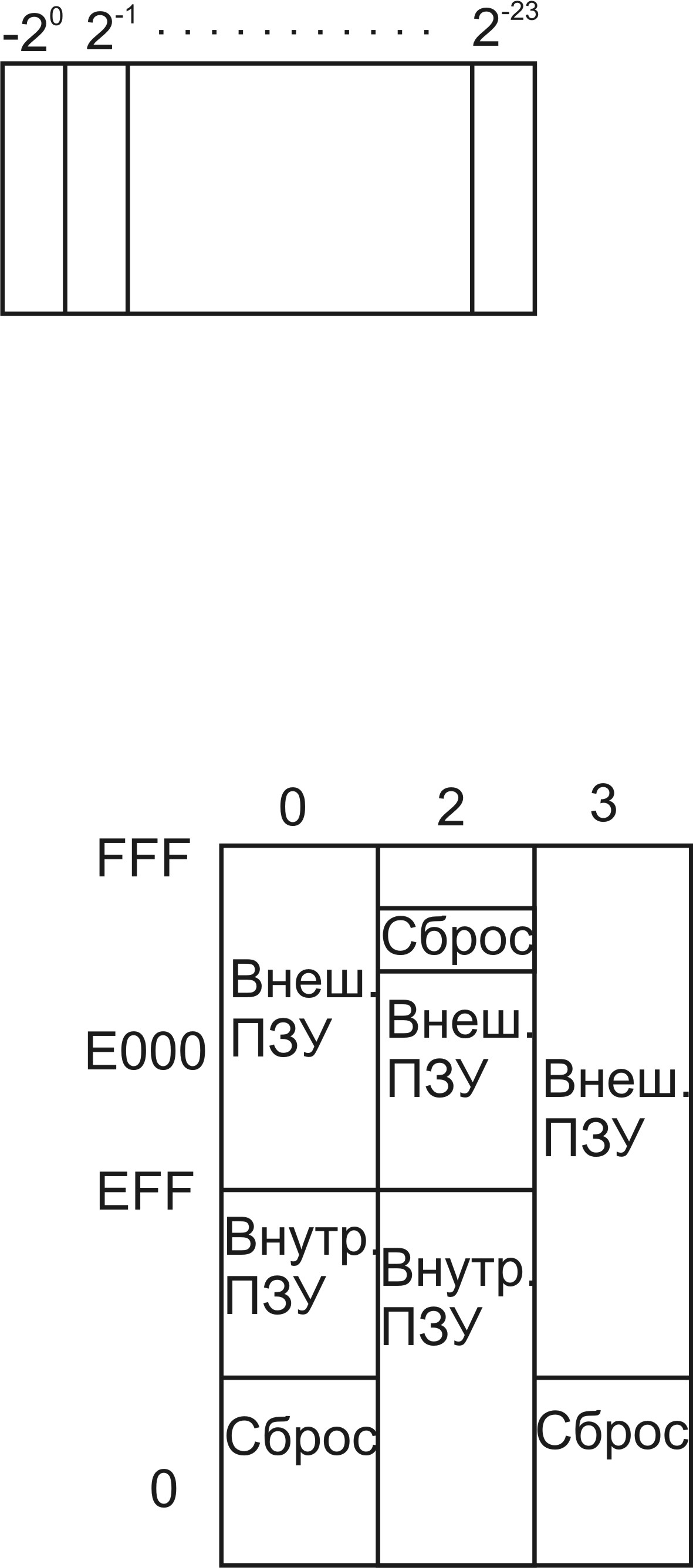

24-разрядные числа в DSP данного семейства представляются следующим образом (рисунок 5.4):

Рисунок 5.4 – Представление 24-разрядных чисел с плавающей точкой

Для 48-ми битного представления используется аналогичный принцип.

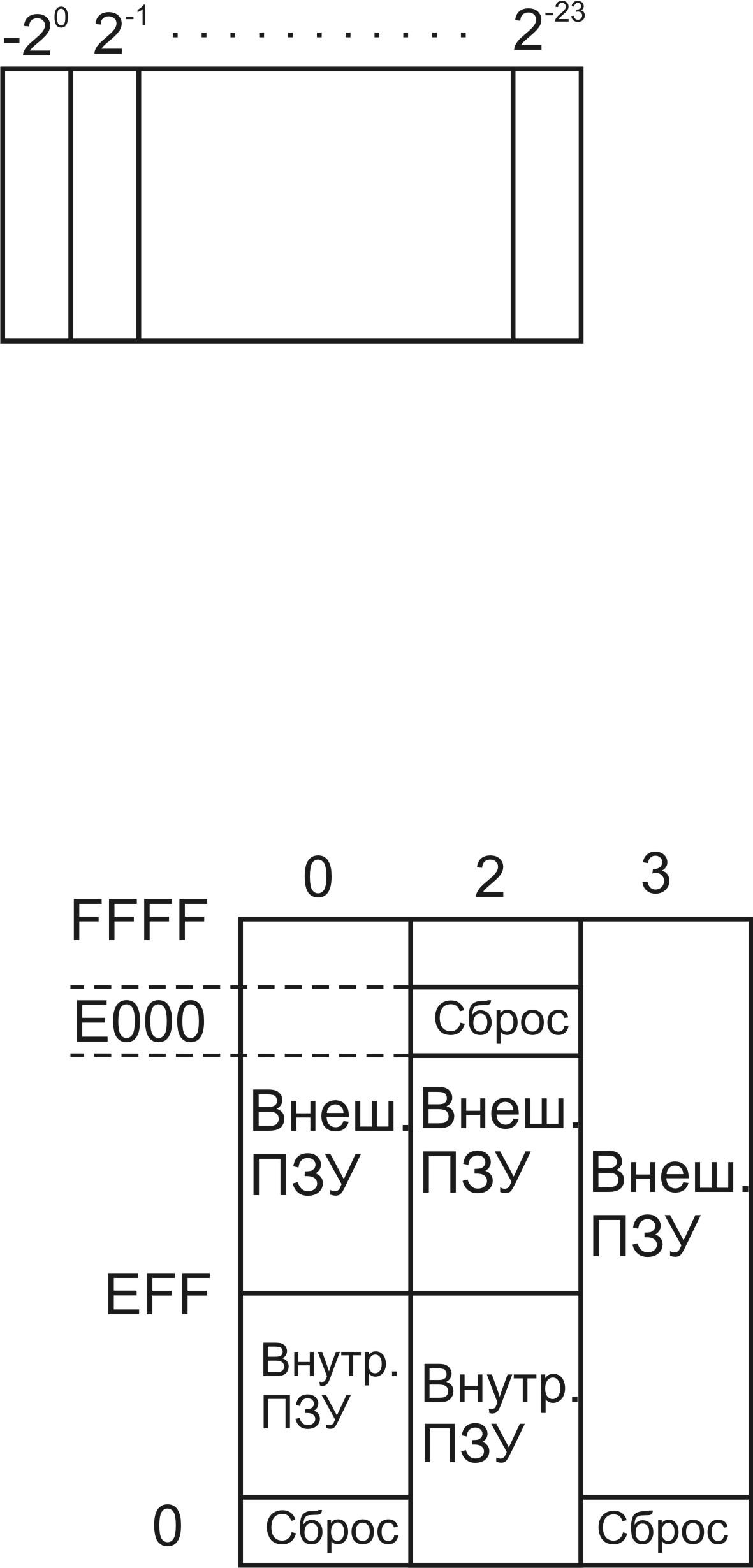

DSP имеет три независимых пространства памяти. Эти пространства конфигурируются битами управления в регистре режима операции. Два бита в данном регистре управляют картой памяти программ, и выбирают адрес вектора сброса. Один бит управляет картами памяти X и Y. Возможные варианты карт памяти программ и памяти данных приведены на рисунках 5.5 и 5.6.

Рисунок 5.5 – Карты памяти программ

Рисунок 5.6 – Карты памяти данных

В некоторых представителях семейства в пространстве памяти X и Y могут размещаться ПЗУ, в котором фирма Motorolla размещает при изготовлении таблицы некоторых часто используемых для вычислений при DSP функций (например, sin, cos и др.). Периферийные модули на кристалле адресуются как обычные ячейки памяти X и Y соответственно.