Программируемые связные адаптеры.

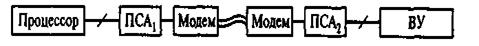

При увеличении расстояний, на которые передаются данные, параллельные связи уже не применяют. Передачу данных осуществляют в последовательном коде по одной сигнальной линии. Для аппаратной реализации этого способа передачи данных используют контроллеры последовательного ввода/вывода, называемые программируемыми связными адаптерами (ПСА). Тракт передачи последовательных данных в общем случае включает в себя источник и приемник данных, программируемые связные адаптеры и модемы (рис.6.5). Адаптер, подключенный к системной шине данных, осуществляет преобразование данных из параллельной формы в последовательную или наоборот.

Модем (модулятор-демодулятор) преобразует двоичные импульсные сигналы в некоторый аналоговый модулированный сигнал, приспособленный к передаче по узкополосным (=3 кГц) телефонным линиям.

Рис.6.5. Структура последовательного тракта передачи данных

Если по такой линии передавать простую последовательность импульсов, соответствующих единицам и нулям, скорость передачи информации будет очень низкой. С помощью различных видов модуляции получают сигнал с более высокой информационной емкостью. Так, современные модемы обеспечивают передачу не менее 38,4 кбит/с. Если расстояние между источником и приемником не настолько велико, чтобы использовать телефонный канал, то передача последовательных данных осуществляется непосредственно от одного адаптера до другого.

Различают два основных режима последовательной передачи данных: синхронный и асинхронный. В обоих режимах работа приемника и передатчика синхронизируется тактовыми сигналами синхронизации одной частоты. В синхронном режиме поток передаваемых символов непрерывный. Для того чтобы приемник мог выделить из потока символов полезную информацию (данные), передатчик в поток информации вводит специально закодированные слова — определенную последовательность единиц и нулей. Такие слова называют синхросимволами. Скорость передачи информации определяется частотой синхронизации. Если между словами данных имеются временные промежутки (данные для передачи еще не готовы), они заполняются синхросимволами до тех пор, пока не возобновится передача данных. При синхронной передаче данных приемник находится в состоянии активного ожидания. Он сравнивает каждое принятое слово с символом синхронизации. Как только такое слово будет выделено, приемник продолжает сравнение принимаемых слов с синхросимволом, при этом все слова, отличающиеся от него, считаются полезной информацией и считываются.

В асинхронном режиме информационный поток делится на отдельные посылки, соответствующие словам данных. При отсутствии посылок на линии устанавливается единичный уровень. Каждая посылка начинается с нулевого старт-бита, затем следуют биты слова данных (информационные биты), за ними — бит четности. Заканчивается посылка 1; 1,5 или 2 единичными стоп-битами (рис.6.6).

В зависимости от числа единиц в передаваемом слове в бите четности передают «0» или «1» таким образом, чтобы общее число единиц, передаваемых в посылке (не считая старт- и стоп-битов), было четным. Это обеспечивает приемнику возможность проверки достоверности передаваемых данных. Приемник подсчитывает количество единиц в слове, и если оно четно, значит, информация в тракте передачи не исказилась. Аналогичным образом может осуществляться контроль достоверности и на нечетность количества единичных битов в посылке.

Рис.6.6. Структура посылки в асинхронном режиме передачи данных

Выделение информации в посылке осуществляется следующим образом. Тактовая частота, которой синхронизируется работа источника и приемника, в 16 раз выше частоты передачи данных, так что на один бит приходится 16 тактовых импульсов. При поступлении нулевого старт-бита приемник запускает счетчик импульсов и с его помощью определяет моменты, соответствующие серединам информационных битов. В эти моменты определяются значения передаваемых битов. Так как число битов в слове данных известно заранее, после приема всех битов проверяется наличие и длительность единичного стоп-бита. Затем принятое слово записывается в параллельный регистр и проверяется на четность/нечетность. После этого параллельное слово данных готово для дальнейшей работы.

Программируемые связные адаптеры выполняются в виде БИС. Такая БИС есть и в семействе интерфейсных ИС Intel — 8251А (российский аналог — К580 ВВ51А). Этот адаптер обеспечивает прием от МП 8-разрядного параллельного кода и преобразование его в последовательный, а также обратное преобразование последовательного потока символов в параллельный код.

Работа адаптера начинается с его программирования. При этом в него заносится следующая информация:

· прием или передача данных;

· режим обмена (синхронный или асинхронный);

· наличие контроля достоверности и его вид (четность или нечетность);

· длина слова данных (5,6, 7 или 8 бит);

· вид синхросимвола и длина стоп-бита (для асинхронного обмена).

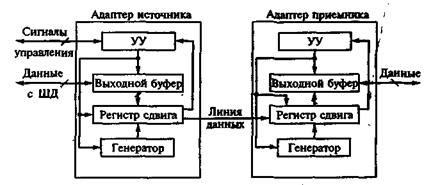

На рис.6.7 показана функциональная схема взаимодействия при асинхронной передаче двух адаптеров, один из которых является передатчиком последовательных данных, а другой — приемником. По системной ШД адаптер-передатчик принимает слово данных и формирует посылку, присоединяя старт-бит, бит четности и стоп-бит. Готовая к отправке посылка помещается в регистр сдвига. Как только от приемника приходит сигнал о его готовности к приему данных, устройство управления УУ запускает генератор, который «выталкивает» биты передаваемого слова в линию передачи. После передачи стоп-бита УУ останавливает генератор.

Устройство управления адаптера-приемника по старт-биту запускает генератор и начинается прием слова данных в регистр сдвига. Определение значения очередного принимаемого бита осуществляется по его середине. Когда время, отведенное на прием одного бита, истекает, происходит сдвиг регистра. После приема всех битов принятое слово помещается в выходной буферный регистр, откуда оно может быть считано внешним устройством или другим микропроцессором. Для этого адаптер должен сообщить приемнику информации о своей готовности к выдаче слова данных. Теперь адаптер-приемник может приступать к приему следующего слова данных, о чем он должен сообщить адаптеру-передатчику.

Рис.6.7. Функциональная схема работы двух адаптеров в режиме

асинхронной передачи последовательных данных

На рис.6.7 показаны упрощенные структурные схемы адаптеров. В действительности каждый адаптер имеет раздельные линии приема и выдачи последовательных данных, причем каждая линия обслуживается своей схемой. Кроме того, для работы с модемами адаптеры имеют соответствующие схемы управления и линии, по которым передаются сигналы квитирования.

Вопросы для самоконтроля

1. Приведите определение микропроцессора.

2. Расскажите о микропроцессорных системах. Назовите их отличие от микропроцессоров.

3. Приведите состав микропроцессорной системы.

4. Расскажите о структуре микропроцессорной системы.

5. Расскажите о принципах работы микропроцессорной системы.

6. Расскажите о режимах обмена в микропроцессорной системе.

7. Расскажите о принципах построения и работе микроконтроллера.

8. Расскажите о принципах построения и работе интерфейсов и интерфейсных БИС.

9. Расскажите о принципах построения и работе шинных формирователей и буферных регистрах.

10. Расскажите о принципах построения и работе адаптеров: параллельных периферийных и программируемых связных.

Список литературы

1. Капустин И.М. и др. Автоматизация машиностроения. Учебник для втузов. Под ред Капустина И.М. – М.: Высш. шк., 2003. – 477 с.

2. Станки с числовым программным управлением (специализированные)/ В.А. Лещенко, Н.А. Богданов, И.В. Вайнштейн и др. Под общ. ред. В.А. Лещенко. – 2-е изд. – М.: Машиностроение, 1988. - 457 с.

3. Миловзоров О.В., Панков И.Г. Электроника. – М.: Высш. шк., 2004. - 288 с.: ил.

4. Браммер Ю.А., Пащук И.Н. Цифровые устройства: Учебное пособие для вузов. – М.: Высш.шк., 2004. - 298с.

Учебное издание

Романов Петр Сергеевич

доктор технических наук, профессор