Процесс передачи сообщения 5 страница

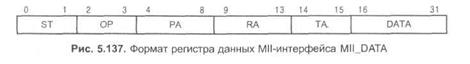

Содержимое регистра данных MII_DATA представляет собой кадр управления МП-интерфейса. В битах ST (Start of Frame Delimiter) указывается начальный ограничитель кадра управления (для корректного кадра указывается формат заполнителя ST := 01). В битах OP (Operation Code) указывается направление передачи данных (ОР = 10 чтение, ОР = 01 запись).Биты РА содержат адрес внешнего PHY-устройства, с которым производится обмен данными.

Контроллер МРС860Т может поддерживать до 32 внешних подключенных PHY-устройств. Биты RA определяют один из 32 регистров внутри PHY-устройства, с содержимым которого будут производиться действия. Биты ТА (Turn Around) задают режим инвертирования информации, для нормальной работы требуется записать в эти биты ТА := 10. Поле DATA содержит сами данные, которые необходимо записать или прочитать в/из указанного регистра. Все рекомендованные значения полей ST, ОР и ТА соответствуют требованиям стандарта 802.3.

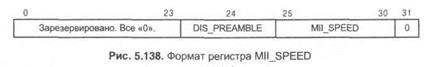

Регистр MII_SPEED (рис. 5.138) используется для контроля тактовой частоты, которая поступает на вывод MDC (МИ Clock). Появление тактовой частоты на этом выводе позволяет начать передачу/прием преамбулы и остального кадра данных.

Стандарт МИ позволяет «опускать» передачу преамбулы, если PHY-устройство этого не требует. Если установлен бит DIS_PREAMBLE = 1, то при обмене будет выдаваться преамбула из 32 «единиц». Если бит равен нулю, то преамбула не выдается.

Содержимое поля MII_SPEED определяет частоту тактового сигнала на контакте MDC. MDC-частота вычисляется как [(системная 4acTOTa)/(MII_SPEEDx2)]. Если в поле MII_SPEED = 0, то на контакте MDC будет «логический нуль». Программируемая частота должна быть не более 2,5 МГц, как определено Mil-спецификацией IEEE.

Формат буферного дескриптора FEC-контроллера. Для обеспечения более гибкого управления буферы данных FEC-контроллера и связанные с ними буферные дескрипторы расположены во внешней памяти. Буферные дескрипторы FEC-контроллера так же, как и буферные дескрипторы других коммуникационных каналов, организованы в таблицу и имеют аналогичный формат, который состоит из четырех слов. Последний дескриптор в таблице имеет в слове состояния установленный бит W = 1 (Wrap).

Готовность буфера передачи и приема к обмену контролируется по состоянию бита готовности R = 1 (Ready) и бита незанятости Е = 1 (Empty) в слове состояния дескриптора. Дополнительно программное обеспечение устанавливает биты X_DES_ACTIVE и R_DES_ACTIVE в одноименных регистрах, чтобы уведомить FEC-контроллер, что данные для передачи в буферах подготовлены или буферы для приема освобождены. После окончания работы с буфером аппаратное обеспечение сбрасывает биты R и Е, чтобы пользователь мог начать обработку их содержимого.

Буферный дескриптор приема. Формат слова состояния дескриптора приема приведен на рис. 5.139.

Бит пустого буфера Е (Empty) устанавливается в «1» пользователем после того, как он обработал данные из этого буфера, и буфер можно использовать для приема новых данных. Бит Е := 0 записывает слово состояния FEC-контроллера после заполнения буфера данными из сети.

Биты RO1 и RO2 (Receive Software Ownership) предназначены только для программного обеспечения пользователя и не взаимодействуют с аппаратурой.

Бит последнего буфера W (Wrap), равный единице, сообщает FEC-контроллеру, что текущий буфер - это последний буфер в таблице и после его обработки необходимо переходить для работы к первому буферу BD в таблице буферных дескрипторов

Бит последнего буфера L (Last) используется в протоколах, где кадр данных может занимать несколько буферов, для указания последнего буфера кадра (если бит L = 1). Указание последнего буфера в кадре обычно применяется для организации прерываний в конце обработки всего кадра данных.

Бит М (Miss) устанавливается в «1» FEC-контроллером, если кадр данных был принят без проверки совпадения адреса (режим promiscuous). Если бит М = 0, то кадр принят, так как адресован именно этой станции.

Бит ВС устанавливается в «1», если принятый кадр данных имеет широковещательный адрес получателя (broadcast).

Бит МС устанавливается в «1», если принятый кадр данных имеет групповой (но не широковещательный) адрес получателя (multicast).

Если бит LG (Lenght Violation) равен «1», то принят кадр данных, длина которого превышает максимально допустимую, запрограммированную для FEC-контроллера длину принимаемых кадров. При этом в буфер будет записана только часть кадра, размер которой не превышает 2047 байт.

Бит TR устанавливается, если длина принятого кадра больше 2047 байт, и кадр был обрезан при приеме.

Если бит NO (Nonoctet Aligned Frame) равен «1», то принят кадр данных, длина которого не кратна 8 битам, и обнаружена ошибка проверки контрольной суммы CRC.

Если бит SH (Short Frame) равен «1», то принят кадр данных, длина которого меньше минимально допустимой для FEC-контроллера длины принимаемых кадров.

Бит CR (CRC Error) устанавливается, если обнаружена ошибка при проверке контрольной суммы, но длина кадра кратна 8 битам.

Бит переполнения буфера OV (Overrun), равный «1», регистрирует ошибку, связанную с переполнением буфера FIFO приемника. Если установлен бит OV = 1, другие ошибки приема не регистрируются.

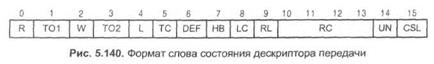

Буферный дескриптор передачи. Формат слова состояния дескриптора передачи приведен на рис. 5.140.

Бит заполненного буфера R (Ready) устанавливается пользователем после того, как он закончит подготовку в буфере данных для передачи по сети. Этот бит постоянно анализируется FEC-контроллером для начала передачи новых данных и сбрасывается (R := 0) после передачи всех данных из этого буфера.

Биты ТО1 и ТО2 (Transmit Software Ownership) предназначены только для программного обеспечения пользователя и не взаимодействуют с аппаратурой.

Бит последнего буфера W (Wrap), равный «1», сообщает FEC-контроллеру, что текущий буфер -это последний буфер в таблице и после его обработки необходимо переходить для работы к первому буферу BD в таблице буферных дескрипторов.

Бит последнего буфера L (Last) используется в протоколах, где кадр данных может занимать несколько буферов, для указания последнего буфера кадра (если бит L = 1).

Если в слове состояния последнего буфера кадра (бит L = 1) установлен бит ТС=1 (Тх CRC), то при передаче вычисляется контрольная сумма содержимого кадра и она передается после последнего байта кадра. Если бит ТС = 0, то передача заканчивается сразу после передачи последнего байта кадра.

Если в слове состояния последнего буфера кадра (бит L = 1) установлен бит DEF = 1 (Defer Indication), то контроллер должен задержаться перед передачей кадра. Этот бит не устанавливается, если при передаче обнаружена коллизия.

Если в слове состояния последнего буфера кадра (бит L = 1) установлен бит НВ = 1 (Heartbeat Error), то при процедуре тестирования аппаратура не выставила активный сигнал на линию «коллизия», т. е. произошел сбой в работе аппаратуры. Этот бит устанавливается, только если в регистре состояния X_CNTRL установлен бит НВС = 1.

Если в слове состояния последнего буфера кадра (бит L = 1) установлен бит LC = 1 (Lata Collision), то обнаружена ошибка «поздняя коллизия», которая регистрируется после корректной передачи более чем 56 байт кадра (размер окна коллизий), и контроллер прервал передачу.

Если в слове состояния последнего буфера кадра (бит L = 1) установлен бит RL = 1 (Retransmission Limit), то контроллер превысил установленный предел числа повторных попыток выхода в сеть из-за коллизий. Текущее число повторных попыток выхода в сеть регистрируется в битах RC (Retry Count).

Если в слове состояния последнего буфера кадра (бит L = 1) установлен бит незаполнения буфера UN (Underrun), равный «1», то регистрируется ошибка, которая возникает при передаче кадра данных, занимающего несколько буферов, когда передатчик передал всю информацию из буфера FIFO, а новые данные для передачи еще не поступили по каналамSDMA. Передача кадра останавливается, и к нему добавляется некорректная контрольная сумма.

Если в слове состояния последнего буфера кадра (бит L = 1) установлен бит CSL (Carrier Sence Lost), то при передаче кадра была обнаружена потеря несущей частоты, т. е. нарушена кодировка данных (например, манчестерское кодирование), но коллизия не обнаружена.