Процесс передачи сообщения 4 страница

После завершения приема полного кадра и заполнения слова состояния последнего: буферного дескриптора регистрируется прерывание и устанавливается бит RFINT := 1 (Receive Frame Interrupt). После приема каждого отдельного буфера текущего кадра регистрируется прерывание и устанавливается бит RXB := 1 (Receive Buffer Interrupt), но только если в слове состояния этого дескриптора установлен бит разрешения прерывания при приеме данных I = 1 (Interrupt).

После завершения МП-интерфейсом очередной порции обмена данными регистрируется прерывание Mil Interrupt и устанавливается бит МΙ Ι := 1.

Если при обмене FEC-контроллером по системной шине произошла ошибка, то регистрируется прерывание Ethernet Bus Error и устанавливается бит EBERR := 1.

В регистре IVEC (Interrupt Vector Register, рис. 5.126) хранится информация об уровне прерывания 0-7 (биты 1LEVEL), который будет связан с FEC-контроллером, и вектор прерывания (биты IVEC). Установка битов IVEC назначает для блоков FEC-контроллера на»«-высший уровень приоритета прерываний (IVEC = 00 - не рассматривать FEC-прерывания, 01 -для некритичных ко времени прерываний, 10-для передатчика, 11 -для приемника

Внутренний буфер FIFO модуля Fast Ethernet, который имеет размер 448 байт (размер одной ячейки 32 бита), может динамически распределяться между приемником и передатчиком, например 32x56 RX и 32x56 ТХ. Увеличенный размер буфера позволяет контроллеру иметь переменное время доступа к внутренней шине для передачи данны» в память. В случае коллизии в сети повторная передача кадра начинается автоматически из внутренних FIFO-буферов контроллера и не требует повторного чтения данных из памяти по системной шине. Для хранения буферов принятых данных и данных для передачи всегда требуется внешняя память. Буферы данных во внешней памяти организованы по кольцевой структуре (аналогично всем другим коммуникационным контроллерам фирмы «Motorola»), и их общее количество зависит только от размера памяти и требований к быстродействию канала связи.

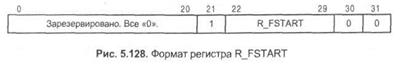

Восьмибитный, только для чтения, регистр R_BOUND (рис. 5.127) определяет вери-ний адрес блока буфера FIFO приема в памяти. Содержимое регистров R_BOUND, R_FSTART, и X_START используется RISC-процессором, чтобы рассчитать доступное пространство между областями памяти для приема и передачи. В поле R_BOUND указан самый большой доступный для FIFO адрес в памяти.

|

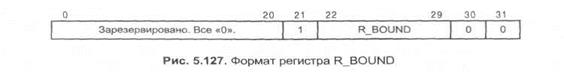

Восьмибитный регистр R_FSTART (рис. 5.128) программируется пользователем и определяет адрес начала блока FIFO приема в памяти контроллера. Блок FIFO приема занимает область от R_FSTART до R_BOUND.

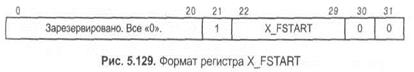

Восьмибитный регистр X_FSTART (рис. 5.129) программируется пользователем и определяет адрес начала блока FIFO передачи в памяти контроллера Блох FJFO передачи занимает область от X_FSTART до R_FSTART-4. Значение по умолчанию (значение, которое будет записано в регистр при сбросе) запрограммировано в микрокоде, и пользователю нет необходимости самостоятельно программировать этот регистр

Обработка коллизий. При передаче станция постоянно контролирует состояние коллизии, которое возникает, если еще одна станция начала вести передачу и произошло наложение кадров данных. При обнаружении коллизии станция начинает передавать в сеть сигнал «мусор» (jam signal), состоящий из одних «единиц», и прекращает передачу своего кадра данных. Далее станция замолкает на интервал (backoff), а затем автоматически делает попытку повторного доступа к сети. В контроллере поддерживаются два алгоритма вычисления интервала backoff. Число повторных попыток доступа к сети из-за коллизии ограничено 15, далее будет генерироваться ошибка.

При обнаружении коллизии FEC-контроллер продолжает передавать в сеть в течение 32 битовых интервалов специальные символы «мусор» (JAM pattern), в результате в сеть передается 32 «единицы». Если коллизия обнаружена во время передачи преамбулы, то контроллер заканчивает передачу преамбулы, а затем начинает передавать JAM-символы.

Если коллизия обнаружена во время передачи первых 64 байт (это размер окна коллизии и длина минимального пакета), то контроллер запускает процедуру повторной передачи. Для этого он замолкает на N х 512 битовых интервалов (512 бит = 64 байта, а N -:лучайное число). Поскольку N - случайное число, то две станции, вышедшие одновременно в сеть и создавшие коллизию, повторят процедуру выхода в сеть через разное зремя. Теоретически окно коллизии определяет время, необходимое для доставки сигнала по сети до всех станций, т. е. если одна станция выйдет в сеть, то все другие станции увидят, что канал занят в течение 512 битовых интервалов.

Если же коллизия произошла после передачи 64 байт пакета (поздняя коллизия, обычно регистрируется в протяженных сетях и сетях с несколькими повторителями), то повторная передача не производится, и после передачи последнего буфера данных кадра s его слове состояния устанавливается бит ошибки передачи LC := 1 (Late Collision).

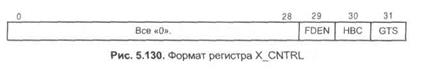

Передача кадров FEC-контроллером. Пользователь может также настраивать режимы работы и блока передатчика FEC-контроллера при программировании регистра X_CNTRL (рис. 5.130). Пользователь может изменять значение бит в регистре только при выключенном контроллере (бит ETHER_EN = 0).

Бит FDEN (Full Duplex Enable) определяет включение режима полнодуплексной передачи для передатчика. Если бит равен 1, то передача начнется независимо от наличия сигналов «наличие несущей частоты в канале» и «коллизия».

При установленном бите НВС = 1 (Heartbeat) будет включен режим тестирования аппаратуры. В этом режиме в течение некоторого интервала (heartbeat window) после завершения корректной передачи кадра аппаратура дает сигнал о коллизии, которой на

|

самом деле в сети нет, и смотрит, как схемы контроллера отработают процедуру регистрации и обработки этой ситуации. Если коллизия не обнаружена (на контакте MII_COL не появился активный сигнал), то будет установлен бит НВ в регистре статуса и выработано соответствующее прерывание.

С помощью программирования бита GTS (Graceful Transmit Stop) пользователь может управлять порядком передачи кадров данных в сеть. Если установить этот бит в «1», то после окончания передачи текущего кадра или если при его передаче обнаружена коллизия, передатчик остановится. Продолжение передачи возможно только после сброса бита GTS = 0.

Когда у станции есть данные для передачи, она проверяет, свободен канал или нет. Если канал свободен, то станция сразу же начинает вести передачу. Если канал занят, то станция после его освобождения ожидает дополнительно некоторый интервал времени, равный интервалу между кадрами данных (interframe gap), а затем начинает передавать свои данные.

Минимальный интервал между пакетами по стандарту Ethernet составляет 96 битовых интервалов. Этот тайм-аут запускается передатчиком, после того как в канале исчезнет несущая частота от предыдущей передачи. Для новой передачи достаточно, чтобы несущая частота отсутствовала в канале не менее 60 битовых интервалов. Если несущая появится в течение 36 битовых интервалов, она будет игнорироваться передатчиком, но будет зафиксирована коллизия.

Регистр X_DES_ACTIVE (рис. 5.131) используется для индикации состояния обработки таблицы дескрипторов передачи. Этот регистр сбрасывается при системном сбросе и при сбросе бита готовности FEC-контроллера ETHER_EN = 0. После того как программное обеспечение пользователя обработало очередной буферный дескриптор, т. е. записало в него данные для передачи и установило бит R := 1 (Ready) в его слове состояния, необходимо записать в данный регистр любое значение. Бит X_DES_ACTIVE будет установлен в «1», когда в этот регистр было записано какое-либо значение. Если биты X_DES_ACTIVE = 1 и ETHER_EN = 1, то контроллер будет искать в таблице дескрипторов передачи заполненный буфер, чтобы передать его по сети. Этот бит сбрасывается контроллером, когда в таблице буферов приема нет готовых к передаче буферов.

Окно коллизий для всех протоколов Ethernet составляет 512 бит, поэтому передача начнется только тогда, когда FEC-контроллер загрузит в буфер FIFO передатчика не менее 512 байт данных. Затем контроллер анализирует незанятость канала связи. Для этого он проверяет наличие несущей частоты (carrier sense) в канале. Передача начнется, когда несущая частота будет оставаться неактивной в течение 60 битовых интервалов. Дополнительно контроллер ожидает еще 36 битовых интервалов, и только после этого, если канал никто не займет, блок MAC выставляет сигнал TX_EN, и контроллер начинает передавать в сеть преамбулу, начальный ограничитель кадра и затем сам кадр данных. При передаче первым в сеть поступает LSB-бит байта.

Первые 64 байта данных контроллер сохраняет в своей внутренней памяти, поэтому если при передаче кадра обнаруживается коллизия, то FEC-контроллер начинает процедуру повторного доступа в сеть независимо от других схем и каналов сетевого контроллера и не требуя дополнительной подкачки данных в буферы FIFO из внешней памяти системы.

Стартовый адрес таблицы буферных дескрипторов передачи, которые расположены во внешней памяти, должен быть предварительно записан пользователем в регистре X_DES_START памяти параметров. Младшие 31-й и 30-й биты регистра должны быть равны нулю, так как адрес должен быть кратен четырем.

Если при завершении передачи очередного буфера данных контроллер обнаружит в слове состояния буферного дескриптора установленный бит L = 1 (Last) и установленный бит ТС = 1 (Тх CRC), то контроллер добавит к переданному кадру данных поле контрольной суммы FCS (32-битовое поле CRC) и сбросит сигнал TX_EN в пассивное состояние. После завершения передачи поля контрольной суммы контроллер заполняет в слове состояния дескриптора переданного кадра данных биты статуса переданного кадра и сбрасывает бит R := 0 (Ready). Если переданный буфер был не последним в кадре (бит L = 0), то контроллер сбрасывает только бит R:=0 в слове состояния переданного буфера.

Если длина передаваемого кадра меньше минимально допустимой длины Ethernet-кадра (64 байта), то кадр данных дополняется до необходимой длины специальными символами-заполнителями (padds). Если же длина передаваемого кадра больше максимально допустимой длины Ethernet-кадра (1518 байт), то длинный кадр данных будет передан целиком, но будет выработано прерывание ВАВТ.

При необходимости пользователь, программируя регистр I_MASK, может определять нужны ли ему прерывания после передачи отдельных буферов данных или кадра данных целиком.

Пользователь может вмешиваться в процесс передачи Ethernet-кадров. Если установить бит GTS := 1 (Graceful Transmit Stop) в регистре X_CNTRL, то FEC-контроллер завершит передачу текущего кадра данных (или прервет его передачу из-за коллизии) ^ остановится. После остановки передатчика будет выработано GRA-прерывание и установлен бит GRA := 1 в регистре прерываний I_EVENT. Передача следующих кадров бу дет продолжена только после сброса бита CTS := 0.

Основные ошибки, возникающие при работе передатчика Ethernet-контроллера, регис трируются в слове состояния буферных дескрипторов и в регистре прерываний IJEVENT

•Переполнение передатчика (Transmitter Underrun, UN). При возникновении этой ошибки FEC-контроллер передает в сеть 32 символа «единицы», которые создадут ситуа цию ошибки при проверке CRC суммы у приемника, и приемник удалит принять» кадр. Передача текущего кадра прерывается, в слове состояния всех не переданны: буферов устанавливается бит ошибки UN := 1, и они закрываются. Далее контроллер переходит к передаче следующего кадра.

• Потеря несущей при передаче кадра (Carrier Sense Lost, CSL). Если при передач!

кадра не обнаружено коллизий, но исчезла несущая частота в канале, то кадр пере

дается до конца, повторных передач не будет, но в слове состояния последнего бу

ферного дескриптора кадра устанавливается бит ошибки CSL := 1.

• Превышен предел повторных попыток передач (Retransmission Limits, RL). При возникновении коллизии FEC-контроллер делает попытку автоматического повторного дос тупа к сети. Число таких попыток ограничено. При превышении установленного числ, попыток передача текущего кадра прерывается, все не переданные буферы закрыва ются, в слове состояния последнего не переданного буфера устанавливается би ошибки RL := 1. Далее контроллер переходит к передаче следующего кадра.

• Поздняя коллизия (Late Collision, LC). Передача текущего кадра прерывается, все н

переданные буферы закрываются, в слове состояния последнего не переданног

буфера устанавливается бит ошибки LC:=1. Далее контроллер переходит к передач

следующего кадра.

• Ошибка из-за самотестирования аппаратуры (Heartbeat, HBC). Через 20 битовых интервалов после успешного завершения передачи кадра передатчик для проверки системы

регистрирует коллизию (которой на самом деле нет). Этот режим проверки включается установкой бита НВС := 1 в регистре X_CNTRL. При возникновении этой ошибки FEC закрывает буферы текущего передаваемого кадра (на самом деле, если 20 интервалов назад был успешно передан кадр, то в данный момент передатчик должен ожидать 96 интервалов до начала передачи следующего кадра, и открытых буферов не должно быть), в слове состояния текущего буферного дескриптора устанавливается бит ошибки НВ := 1 и генерируется прерывание HBEER, если оно разрешено.

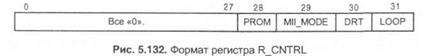

Прием кадра FEC-контроллером. Пользователь может настраивать режимы работы блока приемника FEC-контроллера при программировании регистра R_CNTRL (рис. 5.132).

Если установлен бит PROM = 1 (Promiscuous), то сетевой контроллер будет принимать все кадры, не проверяя совпадения адреса станции и адреса в поле «получатель».

Бит MII_MODE определяет используемый режим внешнего интерфейса как для приемника, так и для передатчика (0 - «7-проводной» режим, используется только для режима 10 Мбит/с; 1 -режим МП-интерфейса).

FEC-контроллер поддерживает тестовые режимы внутренней и внешней петли. Эти режимы программируются битами LOOP и DRT в регистре R_CNTRL (LOOP = 1, DRT = 0 -внутренняя петля, LOOP = 0 и DRT = 0 - внешняя петля). В режимах петли FEC-контроллер работает в полнодуплексном режиме.

Бит DRT (Disable Receive on Transmit) определяет включение режима полнодуплексной передачи. Если бит DRT = 0, то приемник и передатчик работают независимо (полнодуплексный режим). Если же бит DRT = 1, то во время передачи кадров приемник временно отключается (полудуплексный режим).

Бит LOOP используется для тестирования аппаратуры. Если бит равен единице, то будет включен режим внутренней петли и выход передатчика внутри будет замкнут на вход приемника. Сигналы на внешние контакты передатчика не поступают. Обратите внимание, что в режиме внутренней петли бит DRT должен быть равен нулю.

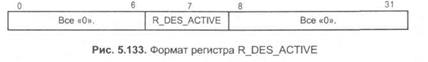

Регистр R_DES_ACTIVE используется для индикации состояния обработки таблицы дескрипторов приема. Регистр R_DES_ACTIVE (рис. 5.133) сбрасывается при системном сбросе и при сбросе бита готовности FEC-контроллера ETHER_EN = 0. После того как программное обеспечение пользователя обработало очередной буферный дескриптор, т. е. считало из него данные и установило бит Е := 1 (Empty) в его слове состояния, необходимо записать в этот регистр любое значение. Бит R_DES_ACTIVE будет установлен в «1», когда в этот регистр было записано какое-либо значение. Если биты R_DES_ACTIVE = 1 и ETHER_EN = 1, то контроллер будет искать в таблице дескрипторов приема незанятый буфер, чтобы принять в него данные из сети. Этот бит сбрасывается контроллером, когда в таблице буферов приема нет готовых свободных буферов.

Первым в байте принимаемых последовательных данных принимается LSB-бит. Когда выставлен активный сигнал RX_DV, приемник вначале проверяет корректность РА/ SFD-заголовка. Если заголовок правильный, то он будет удален, а последующие данные

будут обрабатываться приемником. Если же заголовок некорректный, то следующий за ним кадр данных будет игнорирован.

При приеме кадры, которые не удовлетворяют по формату требованиям стандарта 802.3, автоматически удаляются, но при этом регистрируются соответствующие ошибки, например прием слишком длинного кадра.

При работе в последовательном режиме (данные поступают по линии RX_D0) после появления активного сигнала RX_DV приемник первые 16 битовых интервалов игнорирует поступающие данные. Следующие 16 битовых интервалов приемник анализирует принимаемые данные на 1/0, подстраиваясь под частоту передаваемого сигнала. Поскольку формат преамбулы и начального ограничителя кадра состоит из повторяющихся комбинаций «1» и «0», то при появлении комбинаций «11» или «00» на участке от 17-го до 21-го битовых интервалов будет зафиксирована ошибка, и кадр будет игнорирован. После 21-го битового интервала приемник контролирует наличие в канале связи комбинации «11» (конец приема поля начального ограничителя PA/SFD и начало полей кадра). Если после 21-го битового интервала до приема комбинации «11» обнаружена комбинация «00», то кадр будет отброшен.

При работе в режиме М ΙΙприемник побайтно контролирует совпадение формата преамбулы и начального ограничителя. Но если в байте обнаруживается комбинация «00», то кадр будет отброшен.

После завершения приема первых 8 байт преамбулы и начального ограничителя следующие принятые данные начинают записываться в буфер FIFO и приемник начинает процедуру распознавания адреса принятого кадра. Если при приеме произошла коллизия, то проверка адреса прекращается и принятые данные отбрасываются. Если успешно принято 64 байта кадра (64 байта - это размер окна коллизий для сетей Ethernet) и адрес получателя в пакете совпал с адресом станции приемника, то FEC-контроллер начинает перезаписывать принятые кадры в буферы во внешней памяти, адреса которых указаны в дескрипторах RxBD. Таким образом, контроллер автоматически отслеживает и обрабатывает все коллизии в сети без вмешательства пользователя (единственное, что следует отслеживать пользователю, - это поздние коллизии).

Стартовый адрес таблицы буферных дескрипторов приема, которые расположены во внешней памяти, должен быть предварительно записан пользователем в регистре R_DES_START памяти параметров (см. табл. 5.82). Младшие 31-й и 30-й биты регистра должны быть равны нулю, так как адрес должен быть кратен четырем.

После заполнения очередного буфера данных в памяти FEC-контроллер сбрасывает бит Е := 0 (Empty) и генерирует RXB-прерывание (если, конечно, установлен бит разрешения прерывания RBIEN в регистре IJVIASK). Если длина принимаемого кадра превышает длину буфера данных, то контроллер выбирает следующий буфер из таблицы дескрипторов, и если он пустой, то продолжает записывать в него последующие данные.

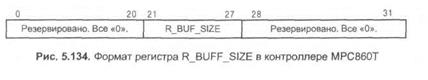

Максимальная длина буфера приема указывается пользователем в регистре R_BUFF_SIZE (рис. 5.134) в памяти параметров FEC-контроллера и должна быть кратна 16 байтам и не меньше 128 байт (R_BUFF_SIZE = 0x000005F0). Поскольку максимальная длина кадра не должна превышать 1518 байт, то в регистре R_BUFF_SIZE используются только биты 21-27. Обычно максимальную длину буфера приема устанавливают равной максимальной длине кадра.

При приеме кадра контроллер контролирует длину принятого кадра на максимальное и минимальное значения. Кадры длиной меньше 64 байт автоматически отбрасываются. Кадры длиной больше 1518 байт сохраняются полностью, но генерируется прерывание BABR и устанавливается бит LG := 1 в слове состояния буферного дескриптора последнего буфера кадра (на практике длинный кадр все-таки усекается, если его длина больше 2047 байт, так как это связано с ограничением разрядности внутренних контрольных счетчиков). После завершения приема кадра (несущая частота в канале становится пассивной) производится проверка контрольной суммы принятого кадра, и она тоже записывается в буфер. Длина реально принятого кадра также записывается в буфер данных в памяти.

После завершения приема всего кадра FEC-контроллер устанавливает бит L := 1 (Last) в слове состояния последнего буферного дескриптора. Также устанавливаются биты статуса принятого кадра и сбрасывается бит Е := 0 (Empty). Затем FEC-контроллер генерирует прерывание (если, конечно, установлен бит разрешения прерывания RFINT в регистре I_EVENT и бит разрешения прерывания RFIEN в регистре I_MASK).

Ошибки, возникающие при работе приемника Ethernet-контроллера, регистрируются в слове состояния буферных дескрипторов и в регистре прерываний I_EVENT и перечислены ниже.

• Переполнение приемника (Overrun, OV). Ошибка регистрируется при переполнении внутреннего буфера FIFO приемника. Текущий буфер приема закрывается, и в его слове состояния устанавливается бит ошибки OV := 1.

• Кадр, не кратный 8 битам (Non-Octet, NO). Кадр с длиной, не кратной 8 битам, обычно обнаруживается по нарушению CRC контрольной суммы. В слове состояния последнего буферного дескриптора принятого кадра устанавливается бит ошибки N0 := 1.Обратите внимание, что если кадр имеет длину, не кратную 8 битам, но проверка кон

трольной суммы не выявила ошибку, то ошибка N0 не регистрируется.

• Ошибка проверки контрольной суммы (CRC Error, CR). При обнаружении ошибки при проверке контрольной суммы принятого кадра FEC-контроллер закрывает все буферы данного кадра и устанавливает в слове состояния последнего буферного дескриптора приема бит ошибки CR := 1. При необходимости пользователь может игнорировать результаты проверки контрольной суммы.

• Нарушение длины кадра (Frame Length Violation, LG). Если длина принятого кадра превышает 1518 байт, то генерируется прерывание BABR и в слове состояния последнего буферного дескриптора принятого кадра устанавливается бит ошибки LG := 1.

Алгоритмы распознавания адреса. FEC-контроллер в каждом принятом пакете производит анализ поля «адрес получателям фильтрует пакеты по индивидуальному (unicast), групповому (multicast) и широковещательному (broadcast) адресам. Отличие между индивидуальным и групповым адресом заключается в значении бита I/G (individual/ group 0/1) в соответствующей позиции поля «адрес получателя».

Если принят пакет с индивидуальным адресом, то контроллер сравнивает его значение с 48-битным значением, которое пользователь определил в ячейках ADDR_LOW и ADDRJHIGH памяти параметров FEC-контроллера. В регистр ADDRJ-OW пользователь должен предварительно записать младшие 32 бита 48-битного адреса станции, в регистр ADDRJH1GH - старшие 3 байта адреса. Байт 0 (биты 0-7 регистра ADDRJ-OW) передается по сети первым.

Если принят пакет с групповым адресом (бит I/G = 1), то контроллер проверяет, не является ли этот адрес широковещательным. Если это широковещательный адрес, то пакет принимается без всяких условий. Если же это просто групповой адрес, то для его проверки будет использована 64-битная хэш-таблица, содержимое которой заполняется пользователем в ячейках HASH_TABLE_LOW и HASH_TABLE_HIGH памяти параметров.

Если же пользователь установил режим прозрачного приема пакетов (бит PROM = 1 в регистре R_CNTRL), то все пакеты принимаются независимо от их адреса, но в слове состояния буферного дескриптора принятого пакета в бите MISS отмечается, произошло ли совпадение адреса в принятом пакете с адресом станции. Если бит MISS = 1, то пакет принят без совпадения адресов.

При работе с хэш-таблицей 48-битный адрес приемника из пакета преобразуется в код, который определяет адрес некоторой ячейки в хэш-таблице. Для этого 48-битный адрес пропускается через 32-битный CRC-генератор (используется полином Х^32+ Х^26+ + Х^23+ Х^22+ Х^16+ Х^12+ Х^11+ +Х^10+ Х^8+ Х^7+ Х^5+ Х^4+ Х^2+ Х+1). 31-й бит результата определяет выбор ячейки таблицы HASH_TABLE_LOW (бит 31 = 0) или HASH_TABLE_HIGH (бит 31 = 1). Биты с 30-го по 26-й определяют номер бита внутри выбранной ячейки. Если этот бит равен 1, то кадр принимается. Если бит равен 0 - игнорируется. Бит О HASH_TABLE_LOW содержит бит индекса 31, а бит 31 регистра HASH_TABLE_LOW соответствует индексному биту 0.

Настройка SDMA-каналов. В контроллере МРС80Т при доступе к внутренним источникам реализованы два уровня арбитража среди коммуникационных модулей. Первый уровень - это доступ к SDMA-каналам, а второй - доступ к PowerPC-ядру. При одновременном доступе к SDMA-каналам от СРМ-модуля и модуля 100BaseT, первым получит доступ коммуникационный СРМ-процессор и все его коммуникационные каналы (SCC,

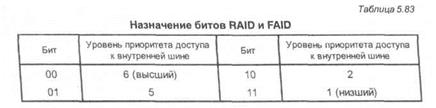

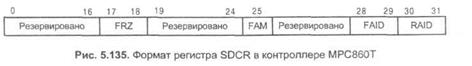

SMC и др.). Далее, при доступе от SDMA-каналов к ядру, уже не рассматривается отдельно, кто запрашивает доступ: СРМ или модуль 100BaseT, и приоритет доступа SDMA к шине PowerPC определяется битами RAID и FAID в регистре SDCR (табл. 5.83). Все SDMA-каналы имеют одно значение ID приоритета, которое устанавливается пользователем в регистре конфигурации SDMA-канала (SDCR, рис. 5.135) и которое позволяет SDMA-каналам соперничать за право передачи по внутренней шине данных с другими источниками внутренних и внешних запросов на арбитраж.

Биты FRZ определяют реакцию SDMA-канапов на выставление сигналов контроля: 00 - SDMA-канал игнорирует FREEZE-сигнал, 10 - SDMA-канал сбрасывает сигнал BR и останавливает (замораживает) передачу, пока выставлен сигнал FREEZE или пока не произойдет сброс системы.

Биты RAID устанавливают уровень приоритета запросов SDMA-каналов по доступу к внутренней шине среди других внутренних источников запросов. Арбитраж запросов от внутренних источников выполняет RISC-контроллер. Обычно устанавливается значение «5» (код 01).

Биты FAID определяют значение ID приоритета арбитража для FEC-контроллера. Обычно устанавливается значение «0».

Программируя биты FAM (FEC Aggressive Mode), пользователь может устанавливать для FEC-контроллера наивысший приоритет доступа к внутренней шине. Если бит FAM = 1, то агрессивный режим доступа разрешен, и биты FAID и RAID должны быть равны нулю (наивысший приоритет). Если же бит FAM = 0, то агрессивный режим выключен и приоритет доступа определяется битами FAID.

В регистре FUN_CODE (рис. 5.136) содержится информация, которая используется при обменах между системным DMA-контроллером и SDMA-контроллером коммуникационных каналов. В битах FC1-FC3 хранятся функциональные коды, которые используются при обменах по системной шине во всех контроллерах «Motorola» и которые будут выдаваться при обмене на одноименные контакты.

В битах DATA_BO[0-1] определяется порядок передачи байт (byte-ordering), который будет использовать SDMA-интерфейс при DMA-обмене (00 - резервировано; 01 - PowerPC Little-endian byte-ordering (64-разрядное слово передается побайтно, начиная с адреса байта 0b111 и до адреса 0b000); 1X - Big-endian byte-ordering (64-разрядное слово передается частями по 16 бит, начиная с ячейки с адресом 0b00 и до 0b 11)).

В битах DESC_BO[0-1] определяется порядок передачи байт (byte-ordering), который будет использовать SDMA-интерфейс при DMA-обмене для открытия и закрытия буферных дескрипторов (00 - резервировано; 01 - PowerPC Little-endian, 1X - Big-endian).

Настройка режимов работы МП-интерфейса FEC-контроллера. Для взаимодействия с внешним PHY-устройством, которое совместимо с MΙΙ-интерфейсом, используются специальные регистры MII_DATA и MII_SPEED. Запись информации в регистр MII_DATA вызывает передачу кадра управления от одного устройства к другому, но только если в регистр MII_SPEED занесено число, отличное от нуля. Логика управления начинает передавать преамбулу, а затем сразу же содержимое регистра MII_DATA при выдаче данных во внешнее устройство и принимать данные в регистр при чтении данных. Поэтому рекомендуется записывать данные в регистр MII_DATA при MII_SPEED = 0.

В ходе обмена данными регистр MII_DATA представляет собой последовательный сдвиговый регистр, поэтому чтение его содержимого до завершения процесса обмена не рекомендуется. При завершении передачи или приема данных будет выработано прерывание MII_DATAIO_COMPL. Если во время обмена записать в регистр MII_DATA новое число, то его содержимое изменится, и станут возможными сбои в алгоритмах работы PHY-устройств.

При выдаче данных из регистра MII_DATA (рис. 5.137) в сеть в битах MII_DATAIO_STATE в регистре MII_STATUS отображается текущее состояние процесса обмена кадрами управления.