Мультиплексор: определение и область применения. Функциональная схема, логическое уравнение и синтез мультиплексора с двумя управляющими входами

Правила сложения чисел в двоичном коде. Одноразрядный и многоразрядный сумматоры.

В двоичной системе счисления информация представляется последовательностью сигналов из 0 и 1, при этом число представляет собой многочлен по степеням числа 2.

n – число разрядов до запятой

а = 0 или а = 1

Отдельные цифры в записи представляет двоичный код который называется битами, а кодовое слово длинной 8 бит – байтом.

Пример: 13.75

Целая часть: последовательно делим на 2, и остаток записывается в обратном порядке.

Целая часть: последовательно делим на 2, и остаток записывается в обратном порядке.

Дробная часть: старшая цифра дробной части находится умножением на 2, если это произведение меньше 1,

то a-1=0, и если оно больше, либо равно 1, то a-1=1, т.е. равна целой части произведения. Следующая цифра a-2 определяется умножением дробной части полученного ранее произведения на 2 и выделение его целой части и т.д.

0.75*2=1.5 > 1 0.75Þ11

a-1=1

0.5*2=1 = 1

a-2=1

13.75Þ1101.11

Комбинированные цифровые устройства – устройства, логическое состояния выходов которых определяются только комбинацией логических сигналов на входах.

Сумматор – комбинированное цифровое устройство, выполняющее арифметическую операцию сложения двух многоразрядных двоичных чисел, кодовые комбинации которых присутствуют на его информационных входах. Результат сложения отображается параллельным двоичным кодом на выходе сумматора.

Поскольку сложение двух многоразрядных чисел всегда начинается с суммирования их младших разрядов, рассмотрим простейшее цифровое устройство, выполняющее сложение двух одноразрядных чисел и называемое полусумматором.

Поскольку сложение двух многоразрядных чисел всегда начинается с суммирования их младших разрядов, рассмотрим простейшее цифровое устройство, выполняющее сложение двух одноразрядных чисел и называемое полусумматором.

Он имеет два информационных входа, куда поступает содержимое суммируемых разрядов, а так же два выхода. Первый из них представляет младший разряд результата и описывается суммой по модулю 2, а второй – обеспечивает сигнал переноса.

Дешифратор: определение и область применения. Функциональная схема и таблицы истинности дешифратора с тремя выходами. Синтез дешифратора.

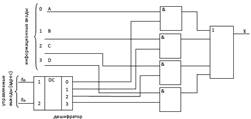

Дешифратор – логическое устройство с несколькими входами и выходами, преобразующее двоичный код, подаваемый на выходы, в сигнал на одном из выходов.

В общем случае дешифратор с n входами имеет 2n выходов, так как n-разрядный код входного слова может принимать 2n различных значений, и каждому из этих значений соответствует сигнал «1» на одном из выходов дешифратора, на остальных выходах сохраняются сигналы «0».

Условное обозначение:

Условное обозначение:

Дешифраторы используют для преобразования двоичного кода в десятичный, в системах цифровой индикации, в устройствах управления последовательностью операций в системах ЭВМ.

Мультиплексор: определение и область применения. Функциональная схема, логическое уравнение и синтез мультиплексора с двумя управляющими входами.

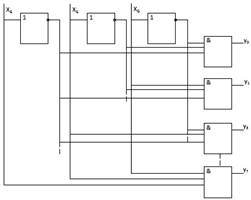

Мультиплексор – логическое устройство с n-управляющими входами, 2n – информационными входами и одним выходом, который соединяется с тем информационным входом, номер которого совпадает с адресом (двоичным управляющим числом).

Используется в устройствах отображения информации в микропроцессорных устройствах управления.

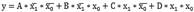

Рассмотрим синтез мультиплексора.

При каждой комбинации управляемых сигналов x0 , x1 (адрес) сигнал «1» появляется на одном из выходов дешифратора, на выходе мультиплексора появляется информация того входа, который совпадает с этой единицей.

Работу мультиплексора можно записать логическим уравнением: