Процесс передачи сообщения 2 страница

Сброс сигнала  = 1 при передаче может служить признаком конца передачи текущего кадра. Но при передаче может сложиться ситуация, когда в буфере FIFO находятся данные от нескольких HDLC-кадров и тогда анализ состояния CTS-сигнала может быть проведен некорректно. Для исключения возможных ошибок в состав регистра режима СРМ введен бит MFF. Если этот бит равен нулю, то в буфере FIFO могут быть данные только одного кадра, и появление сигнала

= 1 при передаче может служить признаком конца передачи текущего кадра. Но при передаче может сложиться ситуация, когда в буфере FIFO находятся данные от нескольких HDLC-кадров и тогда анализ состояния CTS-сигнала может быть проведен некорректно. Для исключения возможных ошибок в состав регистра режима СРМ введен бит MFF. Если этот бит равен нулю, то в буфере FIFO могут быть данные только одного кадра, и появление сигнала  = 1 свидетельствует о завершении передачи текущего кадра. Если бит MFF = 1, то в буфере могут находиться данные от нескольких кадров, и для обнаружения конца передачи кадра производить анализ сигнала CTS бесполезно. Такой режим работы может быть удобен для случая, когда передаются небольшие кадры back-to-back (кадры, требующие немедленного возврата), или пользователь жестко фиксировал число флагов, передаваемых между кадрами. В этих случаях конец передачи кадра может быть проанализирован или вычислен на основе имеющейся информации.

= 1 свидетельствует о завершении передачи текущего кадра. Если бит MFF = 1, то в буфере могут находиться данные от нескольких кадров, и для обнаружения конца передачи кадра производить анализ сигнала CTS бесполезно. Такой режим работы может быть удобен для случая, когда передаются небольшие кадры back-to-back (кадры, требующие немедленного возврата), или пользователь жестко фиксировал число флагов, передаваемых между кадрами. В этих случаях конец передачи кадра может быть проанализирован или вычислен на основе имеющейся информации.

Контроллер HDLC bus. Контроллер HDLC bus - это расширение HDLC-протокола, позволяющее применять его в сетях с конфигураций point-to-point и point-to-multipoint. Протокол HDLC bus используется на канальном уровне управления как вариант HDLC-протокола, часто называемый LAPD, для работы в point-to-multipoint конфигурациях, так как контроллер HDLC может работать только в конфигурациях point-to-point. На физическом уровне управления протокол позволяет восьми терминалам получить доступ к S/T bus для передачи кадров. Контроль доступа к каналу связи производится через D-канал.

Контроллер HDLC bus позволяет создавать сеть небольшого размера, при этом выходы TxD станции должны быть сконфигурированы как выходы open-drain, чтобы было возможно объединять их в общую шину. Контроллер HDLC bus может работать с внешними контактами или в режиме NMSI, или в режиме TDM bus.

Устройства S/T-интерфейса проверяют незанятость канала передачи, просматривая состояние «эхо»-бита на линии. В «эхо»-бите отражаются все биты, которые недавно передавались по D-каналу. В зависимости от класса терминала устройства могут ожидать получение от 7 до 10 единичных битов на «эхо»-бите канала, перед тем как начать передачу LAPD-кадра. Наличие 7-10 последовательных «1» в канале свидетельствует о том, что в канале нет передачи данных и идет передача IDLE-последовательностей. Контроллер HDLC bus поддерживает формат кадра HDLC, а значит максимальное число последовательных «1» в кадре не может превышать шести, так как после каждых пяти последовательных «1» в кадре происходит вставка «0» (операция bit-stuffing).

После начала передачи станция постоянно контролирует, что она передала, читая «эхо»-бит. В контроллере HDLC bus механизм «эхо»-бита реализован через внешние контакты. Вывод TxD соединен с контактом  .Контроллер передает данные на контакт TxD и контролирует их с контакта

.Контроллер передает данные на контакт TxD и контролирует их с контакта  . Передача продолжается, пока бит, который станция передала, совпадает с битом, который станция прочитала («эхо»-бит). Если эти биты не совпадают, возникает состояние коллизии между терминалами. При этом станции, которые передавали нулевой бит, прекращают передачу, а станции, которые передавали единичный бит, продолжают передачу. Для того чтобы уменьшить вероятность возникновения коллизии и захвата шины одной станцией, после завершения передачи станции понижают свой приоритет, чтобы разрешить другим станциям доступ к шине.

. Передача продолжается, пока бит, который станция передала, совпадает с битом, который станция прочитала («эхо»-бит). Если эти биты не совпадают, возникает состояние коллизии между терминалами. При этом станции, которые передавали нулевой бит, прекращают передачу, а станции, которые передавали единичный бит, продолжают передачу. Для того чтобы уменьшить вероятность возникновения коллизии и захвата шины одной станцией, после завершения передачи станции понижают свой приоритет, чтобы разрешить другим станциям доступ к шине.

Основные отличия протокола HDLC bus:

• протокол HDLC bus поддерживает все другие протоколы, которые базируются на HDLC-кадре; таким образом, в сети могут одновременно работать несколько станций, которые используют различные варианты HDLC-протокола;

• станции HDLC bus могут объединяться в сеть с HDLC-станциями для совместной работы;

• перед началом передачи контроллер HDLC bus ожидает получение или 8, или 10 единичных битов, чтобы убедиться, что канал передачи свободен;

• HDLC bus позволяет строить более короткие по размерам сети; это ограничение связано с типом выхода контакта TxD, так как выход open-drain требует дополнительного со

противления, подключенного к источнику питания, и ориентирован на небольшие сети;

• карта памяти параметров контроллера HDLC bus полностью совпадает с картой памяти обычного HDLC-контроллера; таким образом, основные режимы функционирова

ния контроллеров HDLC и HDLC bus совпадают.

|

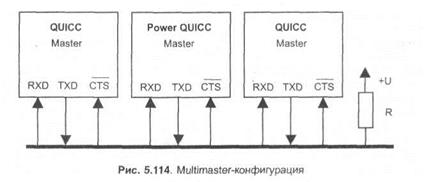

На рис. 5.114 приведена схема подключения HDLC bus-контроллеров в сети с конфигурацией multimaster. При этой конфигурации все станции могут передавать/принимать данные от любой станции и все передачи идут в режиме полудуплекса.

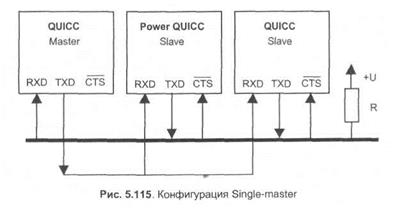

В режиме одиночного мастера (single-master) master-станция может передавать данные любой slave-станции без коллизии, так как все управление передачей возложено на master-станцию. Slave-станции могут взаимодействовать только через master-станцию. Если slave-станция желает передать данные другой slave-станции, то она пересылает их master-станции, которая принимает их в свой буфер, а затем передает их другой slave-станции. Достоинство этой конфигурации заключается в том, что может быть реализована полнодуплексная передача. Конфигурация single master (рис. 5.115) наиболее предпочтительна для сетей с конфигурацией соединений point-to-multipoint.

Доступ к HDLC bus. Для доступа к шине контроллер HDLC bus подсчитывает число единичных битов, полученных по линии контакта  . Если на этом контакте обнаружен «0», то счетчик единиц сбрасывается. Наличие «0» на линии данных может свидетельствовать о том, что кто-то уже начал передачу, послав открывающий флаг кадра формата 01111110. Если два и более передатчиков пытаются получить доступ к шине, то возникает состояние коллизии. В этом случае только один передатчик продолжит передачу, а остальные ее прервут. В дальнейшем контроллер HDLC bus обеспечит автоматическую повторную передачу для передатчиков, работа которых была прервана во время коллизии.

. Если на этом контакте обнаружен «0», то счетчик единиц сбрасывается. Наличие «0» на линии данных может свидетельствовать о том, что кто-то уже начал передачу, послав открывающий флаг кадра формата 01111110. Если два и более передатчиков пытаются получить доступ к шине, то возникает состояние коллизии. В этом случае только один передатчик продолжит передачу, а остальные ее прервут. В дальнейшем контроллер HDLC bus обеспечит автоматическую повторную передачу для передатчиков, работа которых была прервана во время коллизии.

Если с линии  получено восемь последовательных единичных бит, то передатчик считает канал свободным и начинает свою передачу. При передаче данные на контакт TxD выставляются по отрицательному перепаду сигнала TCLK, а сигнал

получено восемь последовательных единичных бит, то передатчик считает канал свободным и начинает свою передачу. При передаче данные на контакт TxD выставляются по отрицательному перепаду сигнала TCLK, а сигнал  читается по следующему положительному перепаду тактового сигнала. Если значение бита, переданного на линию TxD, совпадает со значением бита, полученного по линии

читается по следующему положительному перепаду тактового сигнала. Если значение бита, переданного на линию TxD, совпадает со значением бита, полученного по линии  , то передача бита прошла успешно. Поскольку контроллер HDLC bus использует схему «монтажное ИЛИ» для соединения выходов TxD, то передача «0» всегда имеет больший приоритет, чем передача «1», поэтому коллизия обнаруживается, только если TxD = 1, a

, то передача бита прошла успешно. Поскольку контроллер HDLC bus использует схему «монтажное ИЛИ» для соединения выходов TxD, то передача «0» всегда имеет больший приоритет, чем передача «1», поэтому коллизия обнаруживается, только если TxD = 1, a  = 0 и в этом случае контроллер прекращает текущую передачу. Если в формат HDLC-кадра включен адрес отправителя, то коллизия будет обнаружена не позднее конца передачи адреса источника.

= 0 и в этом случае контроллер прекращает текущую передачу. Если в формат HDLC-кадра включен адрес отправителя, то коллизия будет обнаружена не позднее конца передачи адреса источника.

Для того чтобы избежать захвата канала передачи одной станцией, введен приоритетный механизм. Станция, которая только что закончила передачу, ожидает не 8, а 10 последовательных «1» из канала перед тем, как начать новую передачу. Это задержка в два дополнительных бита дает другим станциям возможность выйти в сеть для передачи. Если станция обнаружила в сети 10 последовательных «1», то она повторно выходит в сеть для передачи новой информации, снижая обратно свое время ожидания до 8 единичных битов, так как никакая другая станция за этот интервал времени не начала свою передачу.

Протяженность сети HDLC bus зависит от метода подключения станции в сети. Так как выходы TXD объединены в «монтажное ИЛИ», и на них данные выставляются по отрицательному переходу сигнала TCLK, а сигнал  считывается по положительному переходу тактового сигнала, то протяженность сети зависит от длительности нулевого полупериода тактового сигнала, поскольку за это время сигнал с линии TXD должен успеть дойти до самой удаленной станции в сети, иначе при анализе сигнала на линии

считывается по положительному переходу тактового сигнала, то протяженность сети зависит от длительности нулевого полупериода тактового сигнала, поскольку за это время сигнал с линии TXD должен успеть дойти до самой удаленной станции в сети, иначе при анализе сигнала на линии  может произойти ошибка, и возникшая коллизия не будет обнаружена. Для увеличения протяженности сети рекомендуется использовать несимметричный тактовый сигнал, у которого длительность «1» короче длительности «О» полупериода.

может произойти ошибка, и возникшая коллизия не будет обнаружена. Для увеличения протяженности сети рекомендуется использовать несимметричный тактовый сигнал, у которого длительность «1» короче длительности «О» полупериода.

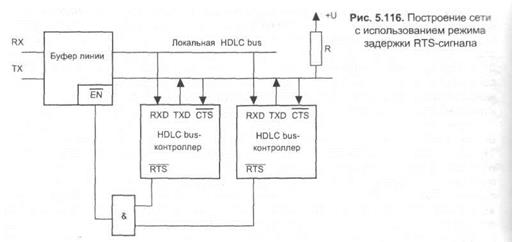

Для того чтобы обеспечить доступ локальной сети HDLC bus к сетям, которые не являются сетью HDLC bus, в контроллере реализован режим работы «задержки RTS-сигнала». Обычно сигнал  = 0 выставляется при начале передачи первого бита открывающего флага, и этот сигнал не используется для построения сети HDLS bus. Но в контроллере МРС860 введен дополнительный режим работы «задержки RTS-сигнала» на 1 бит, если установлен бит BRM = 1 в регистре PSMR. В этом режиме данные на линию передаются как обычно, но сигнал

= 0 выставляется при начале передачи первого бита открывающего флага, и этот сигнал не используется для построения сети HDLS bus. Но в контроллере МРС860 введен дополнительный режим работы «задержки RTS-сигнала» на 1 бит, если установлен бит BRM = 1 в регистре PSMR. В этом режиме данные на линию передаются как обычно, но сигнал  = 0 выставляется с задержкой на один период тактовой частоты. Наличие сигнала RTS = 0 можно использовать для открытия буфера (рис. 5.116). Введение режима задержки

= 0 выставляется с задержкой на один период тактовой частоты. Наличие сигнала RTS = 0 можно использовать для открытия буфера (рис. 5.116). Введение режима задержки  -сигнала позволяет не пропускать во внешнюю сеть первый бит кадра, который используется для обнаружения коллизий и не является битом данных. В этой схеме контроллеры HDLC bus не взаимодействуют друг с другом, но могут передавать информацию во внешнюю сеть. При этом выходы TXD всех контроллеров должны быть объединены и настроены на режим open-drain. А все RTS-выводы должны быть настроены на режим работы с задержкой.

-сигнала позволяет не пропускать во внешнюю сеть первый бит кадра, который используется для обнаружения коллизий и не является битом данных. В этой схеме контроллеры HDLC bus не взаимодействуют друг с другом, но могут передавать информацию во внешнюю сеть. При этом выходы TXD всех контроллеров должны быть объединены и настроены на режим open-drain. А все RTS-выводы должны быть настроены на режим работы с задержкой.

|

Если включен режим задержки RTS, то этот сигнал появляется активным (  = 0) с задержкой на 1 бит относительно момента выставления битов данных. Таким образом, за этот такт задержки контроллеры HDLC bus определяют, есть коллизия или нет. Если коллизия возникла, то сигнал

= 0) с задержкой на 1 бит относительно момента выставления битов данных. Таким образом, за этот такт задержки контроллеры HDLC bus определяют, есть коллизия или нет. Если коллизия возникла, то сигнал  = 1 и выхода на внешнюю сеть нет. Если коллизии нет, то данные передаются во внешнюю сеть, так как сигнал

= 1 и выхода на внешнюю сеть нет. Если коллизии нет, то данные передаются во внешнюю сеть, так как сигнал  = 0 откроет буфер.

= 0 откроет буфер.

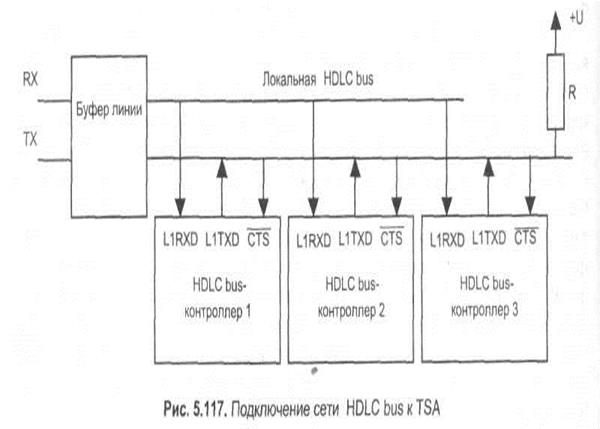

Если необходимо организовать доступ из локальной сети HDLS bus к сети, которая работает с TDM-каналами передачи, то можно применить схему, похожую на схему рис. 5.117. Отличие заключается в том, что нет необходимости использовать сигнал RTS. Просто в каждом контроллере HDLC bus производится настройка его TSA-блока в последовательном интерфейсе SI на работу с определенным временным слотом. К каждому временному слоту может быть подключено произвольное число контроллеров HDLC bus. Локальные контроллеры HDLC bus не смогут общаться друг с другом, но смогут передавать информацию на внешний TDM-канал. Данные будут передаваться по контакту L1TXD и приниматься по линии L1RXD. Коллизия будет обнаруживаться через линию  , но этот сигнал следует анализировать только во время наступления выбранного временного слота (см. рис 5.117).

, но этот сигнал следует анализировать только во время наступления выбранного временного слота (см. рис 5.117).

|

ДОСТУП К СЕТЯМ ETHERNET

Ethernet-контроллер. Протокол Ethernet/IEEE 802.3 широко распространен в современных локальных сетях. Протокол предлагает множественный доступ станций к сети с обнаружением сигнала несущей частоты (метод CSMA/CD). Ethernet-версии - это расширение базовых версий контроллера МРС860, в которых к имеющимся коммуникационным протоколам добавлена поддержка Ethernet-протокола и реализованы функции МАС-уровня в соответствии с требованиями стандарта IEEE 802.3. Настройка SCC-канала на работу с Ethernet-протоколом (10 Мбит/с) производится в битах MODE (MODE = 1100) регистра GSMR. Рекомендуется для работы с Ethernet-протоколом использовать SCC1-контроллер, так как он имеет буферы FIFO, размер которых больше в два раза аналогичных буферов FIFO других SCC-каналов.

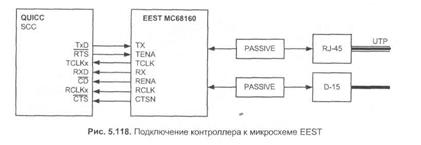

Для подключения Ethernet-контроллера к сети Ethernet требуется дополнительный внешний передатчик. Фирма «Motorola» выпускает специализированный модуль МС68160 EEST (Enhanced Ethernet Serial Transceiver) для подключения к реальной сети. QUICC-контроллер подготавливает кадры данных, а EEST-передатчик выполняет манчестерское кодирование/декодирование сигналов, автоматическое определение типа разъема и типа сетевого кабеля (AUI или 10Base-T) и выполняет преобразование логических сигналов в электрические импульсы, которые используются при передаче сигналов по выбранному кабелю. Следует обратить внимание, что встроенный блок DPLL не используется для манчестерского кодирования/декодирования сигналов, так как не обеспечивает требуемой скорости передачи данных в 10 Мбит/с. Поэтому при работе с Ethernet-протоколом DPLL-блок должен быть выключен, а все функции кодирования и декодирования данных возлагаются на внешний передатчик EEST. Подключение контроллера к микросхеме EEST показано на рис. 5.118.

Перечислим правила подключения PowerQUICC-контроллера к микросхеме EEST.

1. Тактовая частота приемника RCLK и передатчика TCLK поступает на QUICC через внешние контакты CLK1, CLK2, CLK3, CLK4 от выводов RCLK и TCLK микросхемы EEST.

2. Для передачи данных вывод TXD контроллера соединяется со входом ТХ передатчи-

ка, а для приема данных вход RXD контроллера соединен с выходом RX передатчика.

3. При работе с Ethernet-протоколом вывод  контроллера становится выводом сиг-

контроллера становится выводом сиг-

нала разрешения передачи TENA (Transmit Enable), который поступает на вход ТЕМА пе-

редатчика. Активное состояние сигнала - «1».

|

4. При работе с Ethernet-протоколом вход  контроллера становится входом сигнала

контроллера становится входом сигнала

разрешения приема RENA (Receive Enable), который поступает с выхода RENA передат-

чика. Активное состояние сигнала - «1».

5. При работе с Ethernet-протоколом вход CTS контроллера становится входом сигнала обнаружения коллизий CLSN (Collision), который поступает с выхода CLSN передатчика. Активное состояние сигнала - «1».

Сигнал обнаружения несущей частоты формируется как комбинация сигналов RENA или CLSN. Дополнительно передатчик EEST имеет вход LOOP, на который пользователь может программно подать сигнал с выхода параллельного порта ввода/вывода для циклического тестирования работы передатчика.

Коммуникационный контроллер сохраняет в буферах памяти каждый принятый байт кадра данных после получения начального ограничителя, используя каналы SDMA. При передаче пользователь должен подготовить в памяти данные, адрес приемника и передатчика и данные поля «тип кадра». При передаче этих данных в сеть QUICC-контроллер автоматически добавит поле контрольной суммы и заполнит поле данных, если его длина меньше 46 байт, специальными символами-заполнителями до заданного минимума.

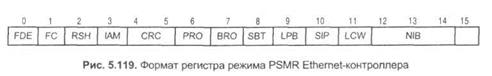

Для тестирования работы аппаратуры приемника, передатчика и буферов FIFO Ethernet-контроллера пользователь может включить петлевой (loopback) тестовый режим. Этот режим включается при установке бита LPB := 1 в регистре режима PSMR Ethernet-контроллера. Если используется режим внешнего loopback, то биты DIAG в регистре общих режимов работы должны быть настроены для работы в нормальном режиме. Если установлен режим внутреннего loopback, то биты DIAG в регистре GSMR должны быть настроены для работы в петлевом режиме (loopback). В режиме внутренней петли схемы SCC-контроллера отключаются от схем последовательного интерфейса, выход передатчика внутри подключается ко входу приемника SCC-контроллера, тактирование приемника и передатчика производится от одного источника. В режиме внешней петли Ethernet-контроллер одновременно передает и принимает данные от микросхемы EEST.

В контроллере МРС860 пользователь имеет дополнительную возможность для настройки работы Ethernet-контроллера в полнодуплексном режиме обмена. Для этого требуется установить бит FDE := 1 в регистре режима PSMR (см. рис. 5.119).

|

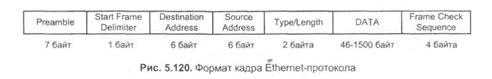

Формат Ethernet-кадра. Кадр начинается с 7-байтного поля преамбулы, которое состоит из повторяющихся «1» и «О» и которое необходимо для подстройки генераторов станции приемника на частоту передатчика. Формат поля преамбулы фиксирован и известен всем станциям в сети, поэтому данное поле может быть использовано для регистрации начала нового кадра данных и обнаружения состояния коллизии, которое возникает, когда две или более станций пытаются одновременно выйти в сеть. Контроллер обеспечивает автоматическую вставку преамбулы при передаче кадра и ее удаление при приеме кадра. Далее следует поле «начального ограничителя», которое извещает приемник о начале нового кадра данных. Формат кадра представлен на рис. 5.120.

|

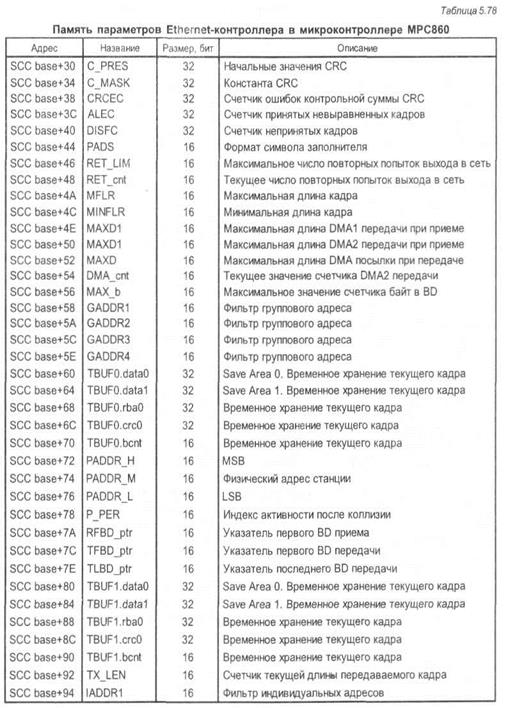

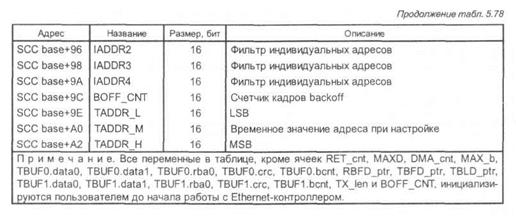

Два 48-битных поля адресов предназначкны для указания адреса станции отправителя и адреса станции получателя информации.Адрес станции отправителя(48 бит) пользователь может задать в ячейках памяти параметров PADDR1_H,PADDR1_M,PADDR1_L(табл.5.78).Двухбайтное поле «тип/длина» предназначено для задания длины поля данных или,в некоторых версиях протокола Ethernet,для задания типа кадра.

|

Два 48-битных поля адресов предназначены для указания адреса станции отправителя и адреса станции получателя информации. Адрес станции отправителя (48 бит) пользователь может задать в ячейках памяти параметров PADDR1_H, PADDR1_M, PADDR1J. (табл. 5.78). Двухбайтное поле «тип/длина» предназначено для задания длины поля данных или, в некоторых версиях протокола Ethernet, для задания типа кадра.

|

Поле данных может иметь размер от 46 до 1500 байт. В ячейке MINFLR пользователь должен задать минимальный размер кадра (>64 байт), а в ячейке MFLR - максимальный размер кадра (<1518 байт). Если длина кадра меньше установленного минимума, то при передаче поле данных кадра будет дополнено специальными символами-заполнителями, формат которых указывается в ячейке PADS памяти параметров, но только если в слове состояния буферного дескриптора установлен бит PAD = 1. Если же бит PAD = О, то символы PAD не добавляются к короткому кадру.

Для контроля правильности передачи данных в состав кадра данных введено поле контрольной суммы, в которое записывается 32-разрядная контрольная сумма кадра данных. Для настройки режима работы с 32-битной CCITT-CRC контрольной суммой с образующим полиномом Х^32+Х^26+Х^23+Х^22+Х^16+Х^12+Х^11+Х^10+Х^8+Х^7+Х^5++Х^4+Х^2+Х^1+1 в биты CRC регистра режима PSMR требуется записать код 10. В ячейке C_MASK пользователь перед началом работы с Ethernet-контроллером должен задать константу образующего полинома 0xDEBB20E3, а в ячейке C_PRES - начальное значение счетчика контрольной суммы 0xFFFFFFFF.

Передача данных. После включения передатчика канала в работу Ethernet-контроллер начинает периодически раз в 128 тактов опрашивать готовность первого буфера в таблице буферов для передачи TxBD. Если пользователь подготовил данные для передачи и не желает ждать 128 тактов, то он может установить бит TOD := 1 в регистре TODR, чтобы вызвать принудительное начало опроса буферов для передачи данных.

Если данные для передачи подготовлены, то контроллер начинает загружать кадр по SDMA-каналам из буфера данных в буфер FIFO, выставляет сигнал ТЕМА к микросхеме EEST и начинает передавать преамбулу, начальный ограничитель и далее сам кадр данных. При передаче Ethernet-контроллер передает LSB-бит первым. Перед началом передачи контроллер проверяет наличие сигнала несущей частоты в канале; после того как в канале будет обнаружен пассивный сигнал несущей частоты, контроллер проверяет, чтобы этот сигнал был пассивным в течение 6,4 мкс. Далее передача будет начата после ожидания 3,2 мкс. Таким образом, сигнал несущей должен быть пассивным в течение 9,6 мкс, перед началом передачи кадра. Поэтому минимальный межкадровый интервал (interpacket gap) для передачи кадров back-to-back установлен равным 9,6 мкс, и при возникновении коллизии повторная передача начинается через 9,6 мкс после того, как сигнал несущей в канале станет пассивным, при условии что он оставался пассивным в течение 6,4 мкс.

После окончания передачи кадра данных, когда в слове состояния последнего буфера кадра обнаружен бит L = 1 (Last) и установлен бит ТС = 1, контроллер начинает передавать кон-трольную сумму кадра и по окончании передачи сбрасывает сигнал ТЕМА в пассивное состояние. Сброс этого сигнала заставляет микросхему EEST начать передачу специального некорректного символа, закодированного манчестерским кодом, уведомляющего о конце Ethernet-кадра.

Далее контроллер заполняет биты статуса переданного кадра в слове состояния последнего буфера и сбрасывает бит готовности буфера к передаче (бит R := 0). Если же текущий буфер кадра передан, но бит L = 0, то для данного буфера только сбрасывается бит R := 0, и контроллер переходит к обработке следующего буфера в таблице TxBD. Если в слове состояния переданного буфера установлен бит прерывания I = 1, то будет выработан запрос на прерывание.

Если во время передачи кадра данных обнаруживается коллизия, то контроллер выполняет специальную процедуру остановки, возвращается к первому буферу кадра и через некоторый интервал времени делает попытку повторной передачи. Для каждого переданного кадра данных в слове состояния последнего буфера кадра устанавливаются биты RC, значения которых определяют, сколько повторных попыток потребовалось, чтобы успешно закончить передачу текущего кадра. Общее число повторных попыток передачи задается в ячейке RET_LIM (стандартное значение 15). При начале передачи контроллер сохраняет первые 5-8 байт передаваемого кадра во внутренней памяти в ячейках TBUFx_xxx, поэтому при повторной передаче не требуется дополнительная загрузка этих данных из буферов данных. Единственное ограничение состоит в том, что первый буфер кадра должен иметь длину не менее 9 байт. Текущее значение числа повторных передач подсчитывается в ячейке RET_CNT, и если число повторов превысило значение RETJJM, то генерируется ТХЕ-запрос на прерывание в регистре событий, устанавливается бит ошибки RL := 1 в слове состояния буферного дескриптора, передача данных из буфера останавливается и буфер закрывается. Продолжение передачи возможно после получения контроллером команды RESTART TRANSMIT.

Ячейка Р_Рег памяти параметров предназначена для определения «степени активности» станции после обнаружения состояния коллизии. В нормальном режиме в эту ячейку заносится код 0x0000 и выполняется стандартный алгоритм расчета следующего момента выхода станции в сеть для повторной передачи. Если же в эту ячейку записан код от 1 до 9, то данный код будет добавлен к счетчику тайм-аута ожидания, и станция выйдет в сеть через большее время. Таким образом, значение «9» предназначено для менее активных станций. Пользователю также предоставляется возможность управлять временем выхода станции в сеть для повторной передачи через бит STB (Stop Backoff Timer) в регистре режима Ethernet-контроллера. Если бит STB = 0, то счетчик времени работает в обычном режиме. Если же бит STB = 1, то счетчик будет останавливаться всякий раз, когда в канале будет активным сигнал несущей частоты.

Если во время передачи обнаруживается ошибка незаполнения буфера underrun, которая возникает, если при передаче мультибуферных кадров данный центральный процессор не успел подготовить для передачи новые буферы, содержащие данные текущего кадра, а данные из последнего подготовленного буфера уже переданы в сеть, то Ethernet-контроллер прерывает текущую передачу, передает 32 «1» бита, которые позволят определить другим станциям CRC ошибку, закрывает буфер, устанавливает бит ошибки UN := 1 в слове состояния BD и генерирует, если разрешено, ТХЕ-прерывание через регистр событий SCC-канала. После получения команды возобновления передачи RESTART TRANSMIT контроллер продолжает дальнейшую передачу.

При передаче Ethernet-контроллер постоянно контролирует наличие сигнала несущей частоты. Если этот сигнал будет сброшен, но состояние коллизии не будет зафиксировано, то генерируется ошибка потери несущей частоты. Признаком этой ошибки будет установка бита CSL = 1 в слове состояния текущего BD. Передача кадра будет продолжена в нормальном режиме.

Для тестирования своей работоспособности некоторые передатчики могут регистрировать ошибку Heartbeat. Если установлен бит НВС = 1 в регистре режима PSMR, то передатчик через 20 битовых интервалов (2 мкс) после завершения передачи кадра данных зарегистрирует внутреннее возникновение коллизии, которая не связана с реальной коллизией в сети и предназначена для проверки работы передатчика. Если бит НВС = 1, но через 2 мкс состояние heartbeat не зарегистрировано, то это значит, что контроллер работает некорректно, поэтому регистрируется ошибка, текущий буфер данных закрывается, в слове состояния буфера устанавливается бит ошибки НВ := 1 и генерируется запрос на прерывание ТХЕ через регистр событий канала, конечно, если это прерывание не замаскировано.

Пользователь может управлять передачей при помощи команд STOP TRANSMIT, RESTART TRANSMIT, INIT TX PARAMETERS. Специальная команда GRACEFUL STOP TRANSMIT позволяет изменить порядок передачи содержимого буферов или кадров или при возникновении ошибки. При получении этой команды Ethernet-контроллер немедленно останавливается, если не было передачи, или если была передача кадра, то продолжает передачу текущего кадра либо до ее успешного завершения, либо до возникновения ошибки коллизии.

Прием данных. При приеме кадров Ethernet-контроллер работает независимо и автономно от центрального процессора и выполняет распознавание адреса станции, проверку контрольной суммы кадра, контроль длины кадра на предельное максимальное и минимальное значение, контролирует максимальное значение размера данных, передаваемых по DMA-каналам.

После включения приемника в работу, если нет коллизий в канале и выставлен активный сигнал RENA, контроллер переходит в режим «охоты» или поиска кадра данных во входном потоке, ожидая получения символа SYN1, формат которого задан в регистре синхронизации DSR. Для Ethernet-контроллера в этот регистр записываются стандартные значения SYN1 = 0x55 и SYN2 = 0x05. Биты NIB в регистре режима PSMR определяют, через сколько битов после установки активного сигнала RENA контроллер будет искать стартовый ограничитель во входном потоке. Обычно устанавливается значение задержки, равное 22 битам. Начальный ограничитель имеет размер 1 байт фиксированного формата OxD5. Значения задержек при приеме кадра приведены в табл. 5.79.

Формат начального ограничителя и преамбулы включает повторяющиеся комбинации 1 и 0. Если при начале приема кадра между 14-м и 21-м битами обнаруживается комбинация 11 или 00, то текущий кадр отвергается. Если комбинация 11 или 00 встречается после приема 21-го бита, но до начала приема начального ограничителя, то кадр тоже отбрасывается. Если принятый набор битов совпадает с содержимым регистра синхронизации, то режим «охоты» выключается и начинается прием кадра данных. При приеме кадра первым принимается LSB-бит.