Тема 5.3 компараторы сумматоры

Компараторы( цифровые комбинационные устройства сравнения)ю

Утройство сравнения или компаратор это операционный узел ЭВМ предназначенный для сравнения 2х чисел А и В .

Результатом сравнения является обнаружение состояний А>B A=B A<B составим таблицу истинности для одноразрядного компаратора.

| A | B | yA>B | yA=B | yA<B |

Сумматор это электронный узел выполняющий операцию суммирования цифровых кодов 2х чисел .При сложении 2х чисел в каждом разряде производится сложение 3х цифр : цифры данного разряда 1го слагаемого (Хi) цифры данного разряда второго слагаемого (Yi) и цифры (1 или 0) переноса из соседнего младшего разряда.

Результат сложения для каждого разряда состоит из 2х цифр : цифры суммы для этого разряда (Si) и цифры (1 или 0) переноса в следующий старший разряд. Pi.

Полу сумматор служит для сложения двух двоичных цифр Xi ИYi. И не учитывая 3й входной величины – переноса из соседнего младшего разряда в данный

| Xi | Yi | Si | Pi |

Si=XiYivXiYi

Pi=XiYi

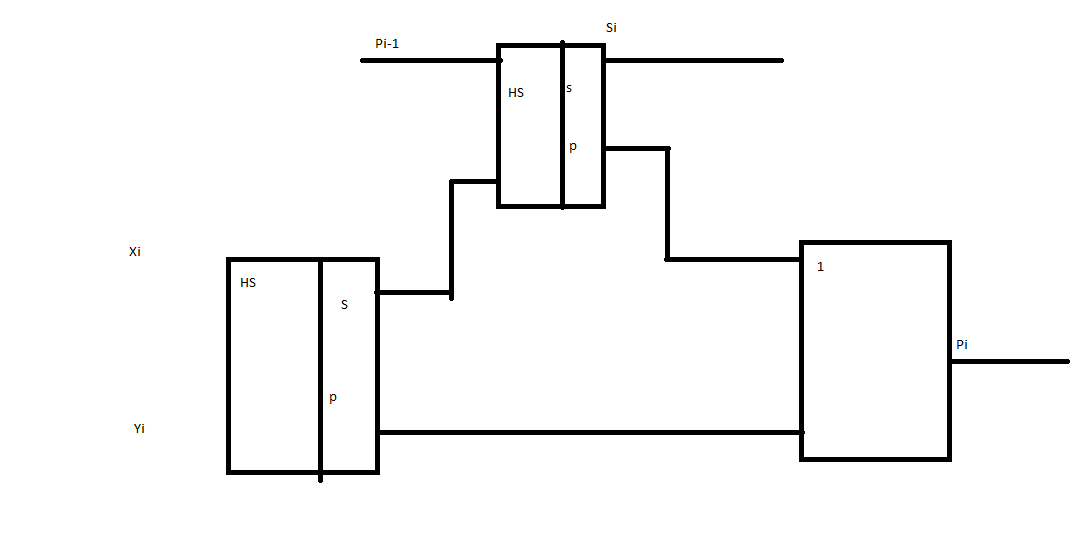

Полный комбинационный разрядный сумматор на 3 входа

На вход подаются Xi Yi Pi -1 ; имеет 2 выхода Xi иPi такой сумматор можно построить из 2х полусумматоров второй полусумматор будет прибавлять к полученной сумме 1ницу переноса из предыдущего разряда которая поступает на дополнительный вход Pi-1.

Уго полного сумматора.

Синтезируем полный одноразрядный сумматор.

Тпблица истинности

| Xi | Yi | Pi-1 | Si | Pi | |

Si=XiYiPi-1vXiYiPi-1v=XiYiPi-1vXiYiPi-1

Pi=XiYiPi-1vXiYiPi-1vXiYiPi-1vXiYiPi-1=YiPi+vXiPi-1vXiYi

| & |

| & |

| & |

| & |

| & |

| & |

| & |

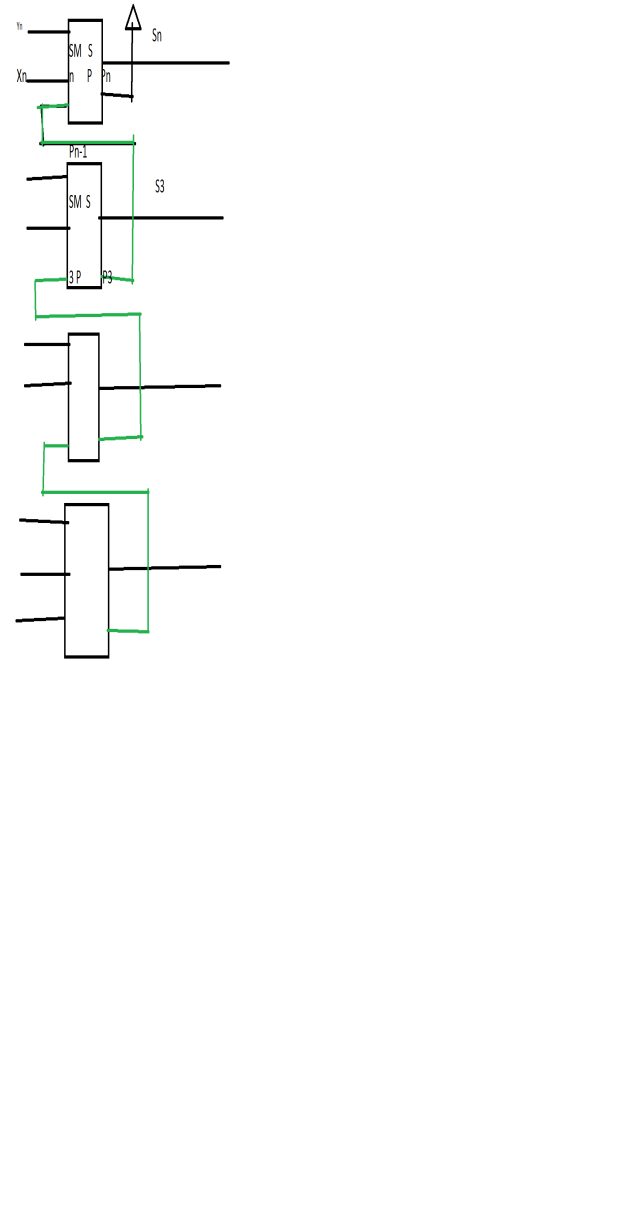

Последовательный сумматор преобразует последовательные коды слагаемых в последовательный код их суммы сложение двух много разрядных двоичных чисел начинается с младшего разряда и выполняется последовательно за столько тактов сколько разрядов содержится в двоичном числе.

Xi 1

Yi 2

Pi-1 3

Перед началом отсчёта схема задержки устанавлевается в 0. Цифра переноса в каждом такте сложения запоминается в схеме задержки с выхода которой снимается бит переноса последущем и поступае на вход три сумматора.

Достоинства малое количества оборудования , недостаток низкое быстродействие .

Параллельный сумматор

В параллельных сумматорых имеется отдельная схема суммирования для каждого разряда . в этом сумматоре N разрядные числа подаются одновременно на его входы а перенос каждого отдельного предыдущего одноразрядного сумматора подаётся на вход переноса последующего одноразрядного сумматора

р

Раздел 6 последовастные устройства

6.1 тригеры – устройства которые имеют элементы памяти.

Назначение и классификация тригерров.Тригерр электронное устройстро