Арифметико-логические устройства

Основными арифметическими операциями являются сложение и вычитание. Разработаны коды дополнительный и обратный, которые позволяют выполнять операцию вычитания методом суммирования. Для выполнения операции вычитания, при использовании дополнительного кода, вычитаемое следует перевести в дополнительный код и просуммировать с первым слагаемым. Полученный результат (разность) будет представлен в дополнительном коде. Затем его следует перевести в прямой код.

Прямой и дополнительный код положительных чисел совпадают. При преобразовании отрицательного числа в дополнительный код все разряды прямого кода следует проинвертировать и к младшему разряду добавить единицу. При обратном преобразовании дополнительного кода в прямой результат следует также проинвертировать и к младшему разряду добавить единицу.

Таким образом, выполнение операции вычитания методом суммирования требует дополнительных затрат времени и снижает быстродействие вычислительных средств.

Для повышения быстродействия ЭВМ разработаны и используются комбинированные арифметико-логические устройства, которые обеспечивают выполнение ряда арифметических и логических операций над прямыми кодами чисел без их преобразования.

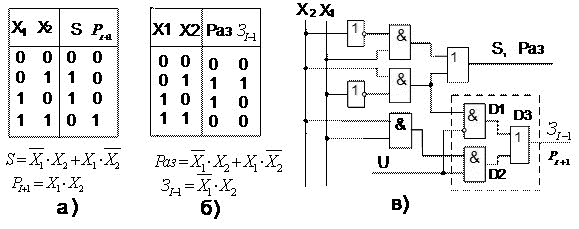

Методика построения одноразрядного арифметического устройства для выполнения операций суммирования и вычитания показана на рисунке 3. Из сравнения логических выражений операций суммирования (рисунок 3, а) и вычитания (рисунок 3, б) следует, что выражения для суммы и разности совпадают, а выражение для заёма является частью операции суммирования или вычитания.

Рисунок 3 Таблицы истинности и структурные формулы операции суммирования а), вычитания б) и схема одноразрядного АЛУ в).

Таким образом, для выполнения операции вычитания не требуется получение дополнительных сигналов, поэтому и не требуются дополнительные аппаратные затраты. Необходимо лишь обеспечить коммутацию сигналов переноса и заёма в соответствии с кодом операции.

| Изм. |

| Лист |

| № докум. |

| Подпись |

| Дата |

| Лист |

| 67 |

| КР 15.02.07 09 00 00 ПЗ |

Многоразрядные АЛУ выпускаются в виде интегральных микросхем или входят в состав процессоров, являясь их основой.

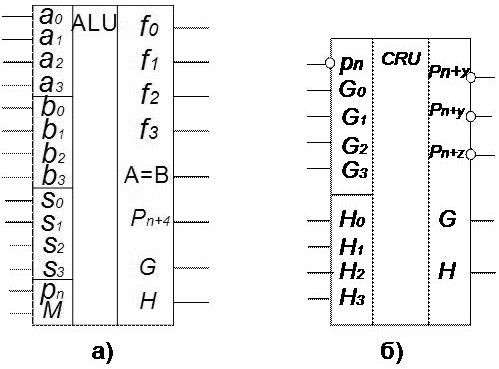

МС 564ИП3 (Рисунок 4,а) — это 4-разрядное параллельное АЛУ, выполняющая 16 арифметических и 16 логических операций.

Рисунок 4

а) Схема 4-разрядного АЛУ 564ИП3 и б). схема ускоренного переноса 564ИП4

A(а0–а3) — первый операнд,

B(b0–b3) — второй операнд,

S(s0–s3) — код операции — 4 разряда.

Если M=0, то выполняются арифметические операции: 24=16, при M=1 выполняются логические операции: 24=16. Итого 16+16=32 операции.

F(f0–f3) — результат операции. На выходе A=B появляется «1», если при выполнении операции вычитания результат операции будет равен «0», то есть A=B. Поскольку АЛУ параллельного типа, то имеются выходы генерации G и распространения переноса H. Pn и Рn+4 — входной и выходной переносы.

Для увеличения разрядности обрабатываемых слов МС АЛУ можно соединять последовательно, как и в параллельных сумматорах с последовательным переносом. При этом, конечно, увеличивается время выполнения операций.

Уменьшить это время и, следовательно, увеличить быстродействие АЛУ можно применением схемы ускоренного переноса 564ИП4, рисунок 4, б). Используя четыре МС АЛУ и одну МС ускоренного переноса можно получить 16-разрядное полностью параллельное АЛУ, время суммирования которого равно времени суммирования одной микросхемы.