Контроллеры управления smc

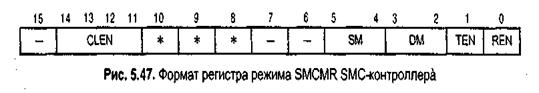

Каждый коммуникационный контроллер содержит два SMC-контроллера (Serial Management Controllers). SMC-контроллер в МРС860 - это полнодуплексный порт, поддерживающий протоколы UART, Transparent, GCI. Настройка режимов работы SMC-контроллера производится в регистре SMCMR (рис. 5.47). Биты 10,9,8 задают параметры, которые определяют работу выбранного коммуникационного протокола.

Включение передатчика SMC-контроллера в работу производится при установке бита TEN, а включение приемника выполняется при записи «1» в бит REN. В SMC-контроллерах реализован режим пониженного энергопотребления, в который он переходит, когда биты разрешения работы TEN и REN некоторого SMC-контроллера равны 0.

Длина передаваемых символов, с которыми работает SMC-контроллер, задается в битах CLEN.

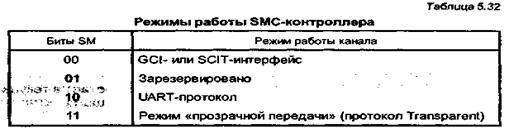

Выбор протокола, с которым будет работать SMC-канал, производится в битах SM (табл. 5.32).

SMC-контроллер поддерживает упрощенную версию UART-протокола, который может быть использован для целей управления и отладки работы контроллера, позволяя освободить от этих задач основные SCC-каналы. Каждый SMC-контроллер поддерживает UART-протокол только в режиме NMSI, используя для его реализации свои собственные внешние контакты. Функционирование контроллера в этом режиме аналогично работе UART-контроллера для SCC-каналов. Тактирование работы SMC UART-кон-троллера выполняется от одного из четырех внутренних BRG-генераторов или от внешнего источника. Но поддерживается только коэффициент внутреннего увеличения частоты, равный 16х.

Протокол Transparent может быть реализован, используя или NMSI-режим работы последовательного интерфейса или мультиплексируемый режим работы TSA совместно с другими каналами ввода/вывода. Функционирование контроллера в этом режиме аналогично работе Transparent-контроллера для SCC-каналов. При подключении SMC Transparent-контроллера к TDM-каналам (например, к линиям Т1) тактирование работы контроллера выполняется от одного из четырех внутренних BRG-генераторов или от внешнего источника (в этом случае поддерживается только коэффициент внутреннего увеличения частоты 1х). SMC Transparent-контроллер может также использовать для синхронизации приемника и передатчика внешние сигналы через специальные внешние контакты.

Каждый SMC-контроллер поддерживает в полном объеме работу с C/I- и Monitor-каналами GCI-интерфейса для сетей ISDN. Для работы в этом режиме контроллер должен быть подключен к TDM-каналу последовательного интерфейса. При работе в SCIT-режи-ме SMC-контроллеры могут управлять работой каналов C/I и Monitor для временных каналов Channel 0 и Channel 1. В контроллере МС68302 канал SMC дополнительно поддерживает работу и с IDL-интерфейсом, но в МРС860 встроенная поддержка этого интерфейса не предусмотрена, и при желании пользователь при настройке работы памяти маршрутизации TDM-канала может программным путем выбрать режим работы с IDL-интерфейсом. В этом случае SMC-контроллер может работать только с Transparent-протоколом.

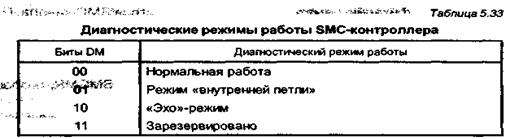

Для тестирования работы своих схем приемника и передатчика SMC-контроллер может быть настроен для работы в режимах «внутренней петли» или «автоматического эха» (табл. 5.33). В этих тестовых режимах функционирование SMC- и SCC-контроллеров аналогично.

При работе SMC-контроллера в режиме NMSI внешний стробирующий сигнал начала обмена поступает и анализируется на контакте SMSYN , внешние тактовые сигналы поступают на вход SMCLK, данные читаются с линии SMRXD и передаются на линию SMTXD. Но для работы SMC UART контроллера внешний стробирующий сигнал SMSYN не используется. При работе в мультиплексируемом режиме данные передаются на контакт L1TXD в выбранном временном слоте и читаются из временного слота с контакта L1RXD. Частота тактовых сигналов для работы приемника и передатчика должна быть одинаковой, и она поступает с контакта L1CLK, строб начала TDM-кадра поступает с контакта L1SYNC.

Память параметров SMC-контроллера. Когда контроллер работает с протоколами UART и Transparent, структура распределения и организация его памяти параметров и буферных дескрипторов аналогичны способам распределения памяти для SCC-контрол-леров. Данные для передачи и данные, которые приняты из сети, хранятся в буфере памяти. В буферах хранится только содержимое поля данных. Старт-бит, стоп-бит и бит контроля при передаче вставляются автоматически и при приеме удаляются самим SMC-кана-лом и в памяти не хранятся. Все буферные дескрипторы для приема и передачи организованы в виде таблицы, опрос которой ведется по круговой системе. Буферы могут быть расположены или во внутренней, или во внешней памяти. При необходимости буферы могут быть расположены в неиспользуемых областях памяти параметров других SCC- или SMC-каналов. Но, если SMC-контроллер работает с протоколом GCI, для передачи и приема данных заранее выделены буферы фиксированного размера по 16 бит каждый, которые располагаются в протокол-независимой части памяти параметров SMC-контроллера.

Память параметров SMC-каналов располагается во внутренней памяти параметров коммуникационного контроллера для МРС860 на страницах 3 и 4. Память параметров SMC-канала состоит из двух частей: протокол-независимой части, в которой определены общие параметры работы SMC-контроллера, и протокол-ориентированной части, в которой содержатся параметры, определяющие работу выбранных коммуникационных протоколов. Назначение переменных в протокол-независимой памяти параметров SMC-контроллера и структура распределения протокол-независимой памяти совпадает с назначением аналогичных ячеек в протокол-независимой памяти параметров SCC-контроллера.

При работе с SMC-каналами пользователь может в любой момент времени произвести модификацию параметров канала, например, настроить его на работу с другим коммуникационным протоколом. Для этого канал должен быть выключен из работы, а затем снова включен. Большинство параметров настройки контроллера рекомендуется производить только при выключенных приемнике (бит REN = 0) и передатчике (бит TEN = 0). При этом текущие буферы данных, с которыми работает канал, закрываются, и после возобновления работы канал будет работать с другими буферами. Рекомендованная последовательность инициализации приемника SMC-канала следующая.

1. Сбросить бит работоспособности (разрешения работы) приемника REN=0 в регистре SMCMR. Прием будет немедленно прерван, и приемник будет установлен в нормальное состояние.

2.Произвести модификацию памяти параметров и регистров SMC-канала. При желании пользователь может просто сбросить все параметры в исходное состояние не изменяя режимов работы, передав контроллеру команду INIT RX PARAMETERS. Если команда INIT RX PARAMETERS не используется, то необходимо передать команду CLOSE RX BD или ENTER HUNT MODE.

3.Установить бит разрешения приема REN := 1 в регистре SMCMR, разрешив контроллеру начать прием информации из канала связи.

Рекомендованная последовательность инициализации передатчика SMC-канала приводится ниже.

1.Если контроллер в текущий момент времени выполняет передачу кадра данных, то предварительно требуется передать ему команду STOP TRANSMIT для прерывания процесса передачи.

2.Сбросить бит работоспособности (разрешения работы) передатчика TEN := 0

в регистре SMCMR. Передатчик будет установлен в начальное состояние.

3.Произвести модификацию памяти параметров и регистров SMC-канала. При желании пользователь может просто сбросить все параметры в исходное состояние, передав контроллеру команду INIT TX PARAMETERS. Если команда INIT TX PARAMETERS не используется, то необходимо передать команду RESTART TRANSMIT.

4.Установить бит разрешения передачи TEN:= 1 в регистре SMCMR, разрешив контроллеру начать передачу в сеть информации из буфера данных, адрес которого указан в ячейке TBPTR.

Работа SMC-контроллера с протоколом UART. Работа SMC-контроллера с UART-протоколом производится аналогично работе с этим протоколом основных коммуникационных SCC-каналов. Но SMC-контроллер поддерживает упрощенную версию UART-протокола, которая имеет следующие отличия:

•контроллер работает с символами, длина которых может быть от 5 до 14 бит (в SCC-контроллерах длина данных может быть от 5 до 8 бит); для хранения данных в памяти используются 16-битные слова;

•контроллер не поддерживает работу с дробными стоп-битами; число стоп-битов задается в разрядах SL; если SL = 0, то один стоп-бит, если SL = 1, то два стоп-бита;

•контроллер не может работать в multidrop-конфигурациях, поэтому из формата кадра исключен бит адреса;

•не поддерживается режим изохронной передачи с коэффициентом внутреннего увеличения частоты 1х;

•при обмене не анализируются сигналы на контактах  и

и  ;

;

•приемник и передатчик могут тактироваться с разной частотой;

•не поддерживается режим распознавания специальных контрольных символов при приеме;

•не поддерживается режим передачи более приоритетного кадра, использующий механизм регистра TODR;

•в регистре статуса не регистрируется IDLE-состояние на линии приемника;

•при передаче данных SMC-контроллер не регистрирует никаких ошибок состояния канала связи и процесса передачи.

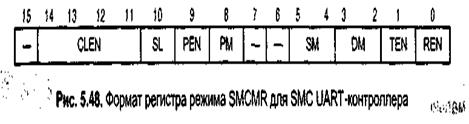

Общая длина кадра данных задается в битах CLEN (рис. 5.48) и равна (CLEN+1). Если в этих битах задан код меньше четырех, то будет зарегистрирована ошибка.

В битах PEN и РМ задается правило использования бита контроля. Если бит PEN = 0, то бит контроля исключен из формата кадра. Если PEN = 1 и РМ = 0, то используется контроль по нечетности. Если PEN = 1 и РМ = 1, то используется контроль по четности.

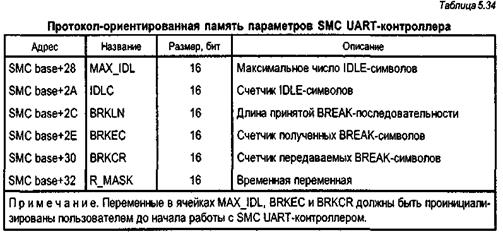

Прием данных SMC UART-контроллером. Если SMC-канал настроен на работу с протоколом UART, то параметры конкретного протокола хранятся в протокол-ориентированной области parameter RAM (табл. 5.34).

После включения приемника в работу контроллер переходит в режим поиска нового кадра данных. После приема первого кадра во временный регистр сдвига контроллер проверяет бит незанятости первого буферного дескриптора в таблице RxBD. Если этот бит Е = 1, то контроллер сохраняет принятый символ в буфере. Если буфер данных заполнен или переполнился счетчик принятых IDLE-символов, SMC-контроллер сбрасывает бит Е:=0 в слове состояния буфера и, если в слове состояния установлен бит I = 1, то генерируется прерывание. Далее контроллер проверяет готовность к приему данных следующего буфера в таблице и, если он пустой, продолжает прием в новый буфер. Если в слове состояния буфера установлен бит СМ = 1, то бит Е при заполнении буфера не очищается, и при следующем обращении контроллера к этому буферу новые данные будут записываться поверх старых

В UART-протоколе, если в сети нет передачи, то по ней передаются IDLE-символы, которые состоят из определенного числа «1» битов. Размер IDLE-символа зависит от размера кадра данных, на работу с которым настроен канал, и равен: 1 старт-бит + 5-14 битов данных + 1 бит контроля (если он используется) + 1-2 стоп-бита. Приемник канала постоянно подсчитывает число полученных. Таким образом, счетчик IDLC подсчитывает число IDLE-символов, полученных между приемом двух кадров данных, в счетчике IDLC. Если начинается прием нового кадра данных, то содержимое счетчика IDLC сбрасывается. IDLC -это вычитающий счетчик, и при сбросе в него записывается содержимое ячейки MAXJD.

Пользователь может определить максимально допустимое число IDLE-символов между кадрами данных. Это число записывается в ячейку MAXJDL. Если счетчик IDLC досчитал до 0, то возникает ошибка приема «IDLE sequence». Текущий буфер закрывается, в нем устанавливается бит ошибки ID := 1 (закрыто из-за IOLE-переполнения) и генерируется RX-прерывание в регистре событий, если оно разрешено. Если не был открыт буфер для приема, то прерывание не генерируется.

Если при приеме кадра данных обнаружена ошибка контроля по четности/нечетности (parity error), то канал записывает принятый байт в буфер, закрывает буфер, устанавливает бит ошибки PR := 1 в слове состояния BD и генерирует RX-прерывание через регистр событий (если оно разрешено). Но далее прием продолжается в нормальном режиме.

При приеме UART-контроллер выделяет кадр данных из битового потока по старт-биту в начале и стоп-битам в конце кадра. Если в кадре не обнаружены «1» стоп-биты, то возникает ошибка формата (frame error). Канал записывает принятый символ в буфер, закрывает буфер, устанавливает в его слове состояния бит FR := 1 и генерирует прерывание RX через регистр событий (если оно разрешено). Если произошла ошибка формата, контроль по четности не производится.

При приеме данные записываются в FIFO выбранного канала, далее они под управлением RISC-контроллера по SDMA-каналам пересылаются в память. Размер буфера FIFO приемника равен двум символам (регистр сдвига и регистр данных). Если скорость работы SDMA-каналов и сети не согласована, возможно возникновение ошибки переполнения (overrun), когда ячейки FIFO все заняты, а из сети получены новые данные. В этом случае новые данные пишутся поверх старых, символ записывается в буфер, буфер закрывается и устанавливается бит переполнения OV: = 1 в слове состояния BD, и генерируется прерывание RX через регистр событий (если оно разрешено). Далее прием продолжается в нормальном режиме.

При приеме UART-контроллер может использовать вход  для автоматического контроля наличия передачи в сети. Если сигнал

для автоматического контроля наличия передачи в сети. Если сигнал  равен 1 при приеме символа, то возникает ошибка (CD lost) потери CD-сигнала. Прием символа прекращается, буфер закрывается, устанавливается бит CD: = 1 в слове состояния BD и генерируется прерывание RX через регистр событий (если оно разрешено).

равен 1 при приеме символа, то возникает ошибка (CD lost) потери CD-сигнала. Прием символа прекращается, буфер закрывается, устанавливается бит CD: = 1 в слове состояния BD и генерируется прерывание RX через регистр событий (если оно разрешено).

При приеме SMC UART-контроллер может контролировать прием символов BREAK. BREAK - это символ, состоящий из «0» битов и не содержащий стоп-биты. Если контроллер получил последовательность BREAK-символов, то он увеличивает счетчик BRKEC и закрывает текущий буфер приема, устанавливает в его слове состояния бит BR := 1, генерирует прерывание BRK через регистр событий, если оно разрешено. Если контроллер получил последовательность BREAK-символов в середине обработки текущего буфера, то он увеличивает счетчик BRKEC и закрывает текущий буфер приема, устанавливает в его слове состояния бит BR := 1 и генерирует RX-прерывание через регистр событий, если оно разрешено. Контроллер также контролирует длину BREAK-последовательности и записывает измеренное значение в ячейку BRKLN памяти параметров.

Пользователь может управлять работой приемника при помощи команд ENTER HUNT MODE, CLOSE RX BD, INIT RX PARAMETERS.

Передача символов SMC UART-контроллером. При передаче UART-контроллер получает из буфера FIFO только сам символ, который будет передан в поле данных. Остальные поля кадра заполняются внутри SCC-контроллера. Во-первых, контроллер анализирует, какой тип контроля будет применен, и вычисляет контрольную сумму, которая записывается в бит контроля в кадре данных. Во-вторых, в формат кадра вводится необходимое число стоп-битов.

После включения передатчика в работу (бит TEN = 1 на рис. 5.48) контроллер начинает передавать в сеть символы IDLE. Далее контроллер опрашивает готовность первого буфера BD к передаче. Если буфер готов (бит R = 1 в его слове состояния), то данные по SDMA-каналу загружаются в буфер FIFO канала и начинают передаваться в сеть. Если первый буфер не готов, т. е. бит R = 0, то контроллер передает IDLE-символ и обращается к буферу повторно через 7-16 периодов тактового сигнала передатчика. Где задержка обращения к таблице буферов, определяется длиной кадра данных, на работу с которой запрограммирован контроллер.

Когда все данные из буфера загружены в буфер FIFO, SMC-контроллер устанавливает в слове состояния текущего буфера биты статуса переданного кадра и сбрасывает бит готовности R := 0. Если в слове состояния был установлен бит СМ = 1, то бит R не сбрасывается и содержимое буфера будет повторно передаваться в сеть при следующем обращении контроллера к этому буферу при новом цикле опроса таблицы буферов передачи, и так будет продолжаться, пока пользователь не сбросит бит R. Если в слове состояния был установлен бит прерывания I = 1, то генерируется прерывание к центральному процессору. Далее контроллер проверяет готовность следующего буфера передачи в таблице TxBD. Если этот буфер готов, то данные из него начинают без перерыва передаваться в сеть сразу же за данными предыдущего буфера. Если же следующий буфер не готов (бит R = 0), то контроллер начинает передавать IDLE-символы, пока данные не будут подготовлены

Если передается первый символ из нового буфера данных, то в слове состояния буферного дескриптора анализируется бит Р. Если этот бит равен 1 (Р = 1), то перед передачей содержимого буфера передается символ преамбулы (все биты 1) и на другом конце канала обнаруживают IDLE-состояние линии связи перед получением данных. Преамбула передается, даже если длина буфера в BD установлена равной нулю. Преамбула представляет собой символ такой же длины, что и передаваемые данные, только все биты в символе равны 1. Если бит Р = 0, то при передаче данных содержимое двух соседних буферов может передаваться без задержек между буферами

Если UART-контроллер получил от CPU ядра команду STOP TRANSMIT, то он передает в сеть содержимое буфера FIFO передачи, затем передает определенное число символов BREAK, далее он переходит к передаче IDLE-символов, пока не получит команду RESTART TRANSMIT. BREAK-символ представляет собой символ установленной длины, у которого все биты равны 0 и отсутствуют стоп-биты. Количество BREAK-символов, которые UART-контроллер передаст в сеть, указывается пользователем в регистре BRKCR. После передачи заданного числа BREAK-символов контроллер обязательно передаст в сеть хотя бы один символ IDLE перед началом передачи следующего кадра данных. Это необходимо, чтобы приемник смог нормально распознать старт-бит нового кадра.

Контроллер SMC Transparent. SMC-канап, работающий с протоколом Transparent, поддерживает более простые режимы работы и меньшие скорости обмена, чем SCC-канал, работающий с аналогичным протоколом «прозрачной передачи».

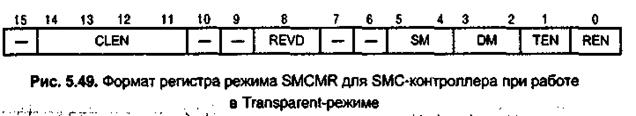

В отличие от SCC-каналов, которые могут работать в прозрачном режиме только с 8-или 32-битными символами (это определяется при программировании бита RWF в регистре GSMR), SMC-канал в режиме прозрачной передачи поддерживает символы длиной от 4 до 16 бит. Биты CLEN в регистре SMCMR (рис. 5.49) задают длину символа, которая равна (CLEN+1) байт и должна быть больше четырех.

Если длина символа больше 8 бит, то бит BS в регистре SMCMR определяет, какой байт данных будет передаваться в сеть первым. В нормальном режиме работы, если длина символа меньше 8 бит, то бит BS = 0. Если же длина символа больше 8, и бит BS = 1, то первым будет передаваться байт, расположенный в ячейке памяти с младшим адресом.

В отличие от SCC-каналов SMC-канал не поддерживает подсчет и проверку контрольной суммы CRC при обмене кадрами.

При передаче, так же как в SCC-каналах, в канале SMC поддерживается режим ин вертирования порядка следования битов в символе. Если бит REVD = 0, то используется нормальный порядок битов и LSB-бит передается первым. Если бит REVD = 1, то первым передается MSB-бит.

Как и у SCC-каналов, передатчик и приемник канала SMC в прозрачном режиме для начала работы должны быть синхронизированы. Синхронизация может выполняться двумя способами. Но при любом способе синхронизация производится от внешнего сигнала, а внутренняя синхронизация от SYNC-символов не используется.

Синхронизация SMC-контроллера. Первый способ применяется, когда SMC-контрол-лер подключен к TDM-каналам через блок TSA последовательного интерфейса. При этом синхронизация кадра выполняется выбранным временным слотом. После обнаружения сигнала синхронизации TDM-кадра строб-сигнала TxSYNC при передаче или строб-сигнала RxSYNC при приеме данные будут передаваться/читаться только в те временные слоты, которые закреплены за данным SMC-каналом при программировании памяти маршрутизации SIRAM последовательного интерфейса. Если SMC-контроллер работает с TDM-каналом в режиме полнодуплексного обмена и его приемник и передатчик функционируют независимо со своими стробирующими сигналами TxSYNC и RxSYNC и со своими тактовыми сигналами RxCLK и TxCLK, то синхронизация приемника и передатчика SMC-канала производится отдельно и независимо. Если приемник при чтении данных из TDM временного канала получит команду ENTER HUNT MODE, то синхронизация приемника будет потеряна, текущий буфер закрывается, и канал будет ждать новой синхронизации сигналом RxSYNC.

SMC-канал в режиме прозрачной передачи поддерживает многобуферную структуру хранения кадра данных в памяти. Если текущий буфер данных уже передан во временной канал, то следующий буфер может быть передан в любом временном канале, выделенном для данного SMC-контроллера и новый кадр данных может начаться в том же временном канале, где закончился предыдущий кадр. Если данные из следующего буфера еще не готовы, то во временной канал выдаются символы IDLE, пока не будет подготовлен следующий кадр данных. Таким образом, при передаче данных в первый временной канал TDM-кадра к моменту прихода сигнала строба начала кадра должен быть готов хотя бы один TxBD-буфер данных, и при его передаче не должна возникнуть ошибка незаполнения (underrun), иначе SMC-контроллер будет выключен.

Второй способ синхронизации применяется, когда канал работает со своими собственными выводами в режиме NMSI. Для синхронизации используется отрицательный фронт внешнего сигнала SMSYNx. При этом сигналы  ,

,  ,

,  не используются. После включения передатчика (бит TEN = 1) или приемника (бит REN = 1) в работу по первому положительному перепаду тактового сигнала SMCLK контроллер анализирует значение сигнала на внешнем контакте

не используются. После включения передатчика (бит TEN = 1) или приемника (бит REN = 1) в работу по первому положительному перепаду тактового сигнала SMCLK контроллер анализирует значение сигнала на внешнем контакте  . Если сигнал

. Если сигнал  = 0, то синхронизация считается установленной. Таким образом, в NMSI-режиме работы последовательного интерфейса приемник и передатчик тактируются от одного тактового сигнала SMCLK и синхронизируются одним сигналом

= 0, то синхронизация считается установленной. Таким образом, в NMSI-режиме работы последовательного интерфейса приемник и передатчик тактируются от одного тактового сигнала SMCLK и синхронизируются одним сигналом  . Ресинхронизация производится только при выключении SMC-контроллера.

. Ресинхронизация производится только при выключении SMC-контроллера.

Приемник начинает считывать данные по тому же положительному перепаду тактового сигнала, по которому обнаруживается активный сигнал  = 0 и устанавливается синхронизация. Приемник не производит повторной синхронизации, даже если в дальнейшем сигнал

= 0 и устанавливается синхронизация. Приемник не производит повторной синхронизации, даже если в дальнейшем сигнал  изменит свое состояние, пока пользователь не выключит приемник из работы, т. е. не сбросит бит REN := 0.

изменит свое состояние, пока пользователь не выключит приемник из работы, т. е. не сбросит бит REN := 0.

Передатчик начинает выдавать первый символ данных, состоящих из одних единиц, асинхронно от тактового сигнала SMCLK, как только обнаружит отрицательный перепад сигнала на линии  . Далее, если данные для передачи готовы, то их передача начнется по следующему отрицательному перепаду тактового сигнала SMCLK после окончания передачи первого служебного символа. Если данные для передачи будут подготовлены позднее, то их передача начнется после передачи нескольких символов, состоящих только из единиц. Передатчик не производит повторную синхронизацию, даже если в дальнейшем сигнал

. Далее, если данные для передачи готовы, то их передача начнется по следующему отрицательному перепаду тактового сигнала SMCLK после окончания передачи первого служебного символа. Если данные для передачи будут подготовлены позднее, то их передача начнется после передачи нескольких символов, состоящих только из единиц. Передатчик не производит повторную синхронизацию, даже если в дальнейшем сигнал  изменит свое состояние, пока пользователь не выключит передатчик из работы, т. е. не сбросит TEN := 0, или пока не будет получена команда ENTER HUNT MODE.

изменит свое состояние, пока пользователь не выключит передатчик из работы, т. е. не сбросит TEN := 0, или пока не будет получена команда ENTER HUNT MODE.

Передача данных. После включения SMC-передатчика в работу (установлен бит TEN = 1) он начинает выдавать в канал IDLE-символы и опрашивает готовность первого буфера данных в таблице TxBD. Когда буфер будет подготовлен, данные по каналам SDMA переписываются в FIFO-буфер и после синхронизации передатчика передаются в сеть. После передачи всех данных из текущего буфера проверяется бит L в его слове состояния. Если это был последний буфер кадра (бит L = 1), то контроллер сбрасывает бит готовности R := 0 в слове состояния буфера и устанавливает биты статуса переданного кадра данных. После этого контроллер начинает передавать в сеть символы IDLE. Если это был не последний буфер данных текущего кадра (бит L = 0), то в слове состояния сбрасывается только бит готовности R := 0, и контроллер начинает передавать данные из следующего буфера передачи в таблице TxBD.

Если при передаче данные из текущего буфера еще не переписаны в буфер FIFO передатчика, то регистрируется ошибка незаполнения underrun, SMC-контроллер прекращает передачу данных из буфера, буфер закрывается, устанавливается бит ошибки UN := 1 в слове состояния текущего буфера и бит ТХЕ := 1 в регистре событий SMC-канала, вызывая прерывание работы центрального процессора. Далее контроллер начинает передавать в сеть символы IDLE. Ошибка незаполнения underrun не регистрируется в интервалах между передачами отдельных кадров данных. При обнаружении этой ошибки SMC-канал возобновит передачу после получения команды RESTART TRANSMIT.

Если в слове состояния переданного буфера установлен бит прерывания I = 1, то по окончании передачи всех данных из этого буфера центральный процессор будет уведомлен об этом маскируемым прерыванием.

Если в слове состояния буфера передачи установлены биты СМ = 1 и R = 1, то этот буфер будет автоматически повторно передаваться в сеть при каждом новом обращении к нему RISC-контроллера, до тех пор пока пользователь не сбросит бит R := 0.

Прием данных. После включения в работу (установлен бит REN = 1) приемник SMC-контроллера проверяет установление синхронизации. Когда синхронизация приемника выполнена, он проверяет незанятость первого буфера приема в таблице RxBD и начинает записывать в него данные. Когда буфер приема будет полностью заполнен, SMC-контроллер сбросит бит незанятости Е := 0 в его слове состояния и, если установлен бит І = 1, сгенерирует маскируемое прерывание к процессору. Если длина принимаемого кадра больше, чем размер текущего буфера приема, то контроллер проверяет незанятость следующего буфера приема в таблице RxBD. Если новый буфер свободен (бит Е = 1), то прием данных продолжается в этот буфер. Если в слове состояния установлены биты Е = СМ = 1, то новые принятые данные будут записываться в этот буфер поверх старых при новом обращении к нему SMC-контроллера.

Если при приеме данных обнаруживается ошибка переполнения буфера FIFO приемника, т. е. RISC-контроллер не успевает освобождать ячейки для приема новых данных, то SMC-контроллер будет вынужден писать новые принятые данные поверх старых, которые будут потеряны. При возникновении этой ошибки SMC-контроллер прекращает прием данных, закрывает текущий буфер приема, устанавливает в слове состояния буфера бит ошибки OV := 1 и бит RX := 1 в регистре событий, уведомляя прерыванием центральный процессор о возникшей ошибке. Прием следующих 'кадров данных будет продолжен в новый буфер приема из таблицы RxBD.

Работа SMC в режиме GCI-контроллера. В МРС860 каждый SMC-контроллер может управлять и C/I- и Monitor-каналами GCI-кадра в сетях ISDN, а при работе в режиме SCIT-конфигурации каждый из SMC-контроллеров может управлять работой любого 0 или 1 SCIT-канала.

При функционировании в режиме GCI-контроллера SMC-канал может быть настроен для работы с соответствующим C/I- и Monitor-каналом при программировании памяти маршрутизации SIRAM. Каждый SMC-канал поддерживает полнодуплексные операции с данными выбранного временного канала и может работать в тестовых режимах внутренней петли и автоматического эха.

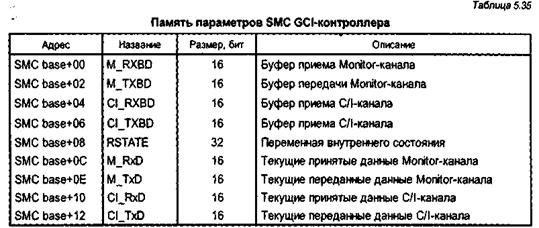

Карта распределения памяти параметров GCI-контроллера значительно отличается от карт распределения памяти нормальных коммуникационных протоколов (табл. 5.35). В режиме SMC GCI протокол-независимая часть памяти параметров содержит буферные дескрипторы приема и передачи для C/I- и Monitor-каналов и, реже, содержит таблицу указателей на место расположения дескрипторов в других областях памяти. Протокол-ориентированная часть памяти параметров для SMC GCI просто отсутствует.

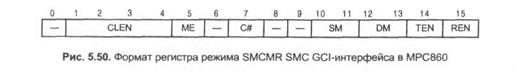

Каждый SMC-контроллер имеет свой собственный регистр настройки режима SMCMR (рис. 5.50), в котором производится настройка параметров работы SMC GCI-контроллера.

Биты CLEN определяют в битах размеры каналов С/І и Monitor для SCIT-каналов О и 1. Длина каналов вычисляется как CLEN = длина канала C/I + бит А + бит Е + длина канала Monitor - 1.

Биты REN и TEN разрешают функционирование приемника и передатчика SMC-кон-троллера. Биты SM и DM определяют режимы работы SMC-контроллера и являются общими для всех режимов работы SMC-контроллера.

Бит С# определяет, с каким из SCIT-каналов будет работать выбранный SMC-контроллер. Если бит равен 0, то используется SCIT-канал 0. Если бит равен 1, то используется SCIT-канал 1.

Бит ME определяет, поддерживает ли выбранный SMC-контроллер работу и управление Monitor-каналом. Если бит ME = 0, то М-канал не используется. Если бит ME = 1, то SMC-контроллер работает с Monitor-каналом по правилам протокола Monitor Channel.

Для управления работой SMC-контроллера в режиме GCI пользователь может применять команды: INIT TX and RX PARAMETERS - для инициализации ячеек памяти параметров в начальное состояние, TRANSMIT ABORT REQUEST и TIMEOUT – для управления процессом обмена данными при работе с М-каналом в режиме Monitor Channel Protocol. При получении команды TRANSMIT ABORT REQUEST контроллер передаст в сеть запрос на прерывание, используя бит А в формате GCI-кадра. Команда TIMEOUT передается контроллеру, если получен запрос на прерывание в А-канале или истек тайм-аут ожидания ответа от сетевого устройства, к которому была передана команда. При получении этой команды контроллер передаст в сеть запрос на прерывание, используя бит Е в формате GCI-кадра.

|

Передача данных по С/І-каналу. Канал С/І с номером 0 в SCIT-режиме используется для передачи управляющей информации между сетевыми устройствами 1-го уровня управления (физический уровень). Сетевые устройства 2-го (канального) уровня управления посылают по нулевому C/ І-каналу команды и получают ответы-индикацию от устройств 1-го уровня. Например, коммуникационный контроллер, работающий в режиме ТЕ (terminal equipment), посылает команды активации/деактивации к S/T-трансиверу и получает ответы, сообщающие о переходе в новый режим работы. С/1-канал 1 в режиме SC1T используется для обмена текущей информации о состоянии между сетевыми устройствами 2-го уровня управления или несетевыми периферийными устройствами, например между АЦП или CODEC.

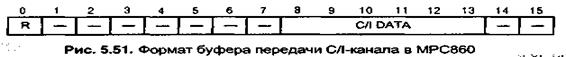

Передача начинается после загрузки данных в буфер передачи C/ І -канала (рис. 5.51), который расположен в ячейке CI_TXBD памяти параметров. Далее SMC-контроллер начинает последовательно выдавать данные через C/l-канал к устройству 1-го уровня управления (физический уровень управления).

Бит R (Ready) устанавливается в «1» центральным процессором по окончании подготовки данных для передачи и записи их в биты C/ І DATA. Сброс этого бита R := 0 RISC-контроллером после завершения передачи показывает, что центральный процессор может записывать в буфер новые данные для передачи.

Если SMC-контроллер работает в SCIT-режиме с 0-м каналом, то по C/l-каналу передаются 4-разрядные данные, и в битах C/ І DATA для хранения этих данных используются только разряды с 10-го по 13-й, а в 8-й и 9-й разряды заносится код 0. Если SMC-контроллер работает в SCIT-режиме с 1-м каналом, то по C/l-каналу передаются 6-разрядные данные, а биты C/l DATA используются для подготовки этих данных к передаче.

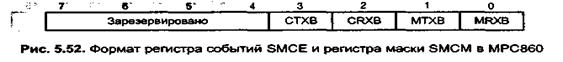

Когда буфер передачи C/ І -канала становится пустым, будет установлен бит СТХВ в регистре событий SMC GCI-контроллера. При установке любого бита в регистре событий SMCE (рис. 5.52) будет выработан запрос на прерывание, если только прерывание от этого события не замаскировано в соответствующем бите регистра маски SMCM, формат которого совпадает с форматом регистра событий. Запрос на прерывание вырабатывается к контроллеру прерывания, и пользователь должен предварительно разрешить прерывание от SMC-контроллера, чтобы нормально зарегистрировать запрос при наступлении некоторого события в SMC-канале. Сброс запроса на прерывание в регистре событий производится записью в этот разряд кода «1». После системного сброса все разряды регистра событий сброшены в «0».

Прием данных по С/ І -каналу. При приеме данных по С/ І -каналу 0 в режиме SCIT SMC-контроллер постоянно контролирует информацию, которую он получает по С/ І каналу. Если одинаковый код получен по С/ І -каналам двух соседних GCI-кадров, то он считается корректным. Дублирование передачи данных введено для повышения надежности передачи информации. Принятую информацию SMC-контроллер сравнивает с предыдущей полученной информацией, и, если они различны, то контроллер реагирует на новую команду или ответ. Такая проверка необходима, поскольку некоторые сетевые устройства при отсутствии новых данных для передачи могут повторно передавать последние данные для поддержания канала в рабочем состоянии. При работе в режиме SCIT с С/ І -каналом 1 метод дублирования данных при передаче не используется. Прием данных из C/l-канала выполняется в буфер приема (рис. 5.53), который расположен в ячейке CI_RXBD. После приема данных генерируется маскируемое прерывание к центральному процессору и устанавливается бит CRXB в регистре событий SMC-контроллера.

Сброс бита Е (Empty) в «0» RISC-контроллером сообщает центральному процессору, что получены новые данные. Центральный процессор после обработки этих данных устанавливает этот бит в «1», разрешая прием в буфер новых данных. Если бит Е = 0 и получены новые данные, то они будут потеряны.

Если SMC-контроллер работает в SCIT-режиме с 0-м каналом, то по С/ І -каналу передаются 4-разрядные данные, в битах С/ І DATA для хранения этих данных используются только разряды с 10-го по 13-й, а в 8-й и 9-й разряды заносится код «0». Если SMC-контроллер работает в SCIT-режиме с 1-м каналом, то по С/1-каналу передаются 6-разрядные данные и биты С/ І DATA используются для хранения этих данных при приеме.

Передача данных по Monitor-каналу. Канал Monitor (М-канал) 0 предназначен для обмена данными между устройствами 1-го уровня управления, например, для обмена содержимым внутренних регистров. М-канал 1 используется для настройки режимов работы (программирования) и для чтения регистров состояния устройств передачи цифровых данных и голоса типа CODEC.

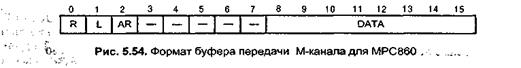

Передача начинается после загрузки данных в буфер передачи М-канала (рис. 5.54), который расположен в ячейке M_TXBD памяти параметров.

Бит R (Ready) устанавливается в «1» центральным процессором по окончании подготовки данных для передачи и после записи их в биты DATA. Сброс этого бита R := 0 RISC-контроллером после завершения передачи показывает, что центральный процессор может записывать в буфер новые данные для передачи. Если SMC-контроллер работает в режиме протокола Monitor Channel, то бит R сбрасывается после получения подтверждения на переданные данные. Далее SMC-контроллер начинает последовательно выдавать данные в сеть через М-канал. Как только буфер М-канала становится пустым, будет установлен бит МТХВ в регистре событий SMC-контроллера.

Биты каналов А и Е используются для управления передачей по М-каналу. Если SMC-контроллер должен передавать данные, поскольку начался закрепленный за ним временной канал, но бит R = 0, то контроллер будет передавать предыдущие данные, и так будет продолжаться, пока не закончится подготовка новых данных.

Бит L (Last) устанавливается в «1» центральным процессором при записи в буфер передачи последнего байта сообщения (End of Message). SMC-контроллер, проанализировав этот бит, вначале дважды передает (дублирует) последний байт данных по М-каналу, а затем дважды в соседних кадрах передает неактивное значение бита в Е-канале. Получив два раза в соседних кадрах неактивный бит в Е-канале, приемник воспринимает эту ситуацию как прием индикации о конце сообщения.

Когда приемник получит запрос на прерывание по А-каналу и центральный процессор обнаружит эту ситуацию, то последний установит бит AR := 1 (Abort Request), и SMC-передатчик передаст команду End of Message в виде двух соседних GCI-кадров с неактивным значением бита в Е-канале.

Пользователь может принудительно вызвать передачу запроса на прерывание по Е-каналу, если передаст SMC-контроллеру команду TRANSMIT ABORT REQUEST.

В биты 3-7 пользователь должен записывать коды «0» при заполнении буфера новыми данными.

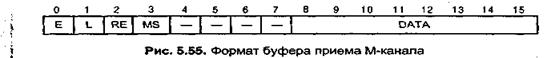

Прием данных по Monitor-каналу. При приеме полученные данные и биты статуса размещаются в буфере приема в ячейке M_RXBD памяти параметров (рис. 5.55).

Биты каналов А и Е используются для управления обменом по М-каналу. Когда принятые данные будут сохранены в буфере приема, центральный процессор уведомляется об этом маскируемым прерыванием. Бит Е (Empty) в ячейке буфера приема сбрасывается в «0» RISC-контроллером, чтобы сообщить центральному процессору, что получены новые данные. Центральный процессор после обработки этих данных устанавливает этот бит в «1», разрешая прием в буфер новых данных. Если бит Е = 0 и получены новые данные, то SMC-контроллер будет ждать установки бита Е = 1 и временно не будет подтверждать прием данных из М-канала. Для подтверждения приема данных от отправителя используется А-канал.

Бит L (Last) устанавливается в «1» SMC-контроллером при приеме по Е-каналу сообщения (End of Message), которое распознается при приеме два раза в соседних кадрах неактивного бит в Е-канале. В этом случае данные, которые были приняты по М-каналу, игнорируются.

Если передатчик SMC-контроллера еще не успел подтвердить по А-каналу прием предыдущего полученного байта данных, а приемник уже принял следующий новый байт данных из М-канала, то регистрируется состояние ошибки и устанавливается бит ER = 1 в ячейке буфера приема M_RXBD.

Для повышения надежности передачи информации передача каждого нового байта данных по М-каналу производится два раза в двух соседних GCI-кадрах. При приеме информации обе копии сравниваются и при их совпадении байт записывается в биты DATA буфера приема и посылается подтверждение о приеме байта по А-каналу. Если же при приеме обнаружено несовпадение двух байтов в соседних кадрах, то они отбрасываются и регистрируется ошибка сравнения с установкой бита ошибки MS = 1.

При заполнении буфера М-канала данными будет установлен бит MRXB в регистре событий SMC-канала.