Параллельные периферийные адаптеры.

Шинные формирователи и порты обеспечивают лишь непосредственную передачу данных между системной шиной и устройством (микропроцессором или ВУ). Более сложные операции выполняют периферийные адаптеры. Эти устройства могут выполнять разнообразные функции обмена данными, причем режим работы устройства задается путем их программирования командами микропроцессора.

Для связи с системной шиной данных внешних устройств, работающих с параллельными кодами, используются контроллеры ввода/вывода параллельной информации — параллельные периферийные адаптеры.

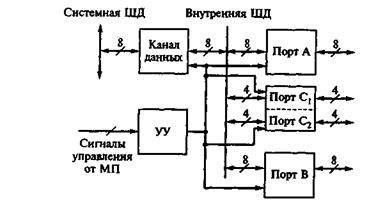

Таким адаптером является БИС Intel 82SSA (российский аналог К580 ВВ55А). Адаптер (рис.6.4) подключается к 8-разрядной системной ШД через канал данных. Этот канал имеет три состояния, благодаря чему адаптер может отключаться от системной ШД. Адаптер содержит три 8-разрядных порта А, В и С, причем порт С может разделяться на два четырехразрядных канала. Каждый порт имеет три состояния и через них осуществляется подключение ВУ к системной ШД.

Рис.6.4. Структура параллельного интерфейсного адаптера

Направление передачи (из МП в ВУ или наоборот) программируется микропроцессором. Управление работой всех узлов адаптера осуществляет устройство управления, которое получает управляющие сигналы от микропроцессора. К ним относятся сигналы «Чтение» (RD), «Запись» (WR), «Выборка кристалла» (CS), «Сброс» (Reset), а также два разряда адреса для выбора порта. Программирование адаптера заключается в том, что МП заносит в устройство управления специальную команду — управляющее слово, которое определяет режим работы портов, а также направление передачи информации.

Адаптер может работать в трех режимах:

· синхронного обмена под управлением МП;

· асинхронного однонаправленного обмена, сопровождаемого сигналами квитирования;

· асинхронного двунаправленного обмена.

Наибольшее число ВУ, обслуживаемых адаптером, обеспечивает первый режим. В этом режиме осуществляется программно-управляемая передача данных по четырем независимым каналам: портам А, В, С, и С2. Обмен осуществляется со скоростью, определяемой процессором. Сигналы квитирования, подтверждающие, что обмен происходит без сбоев, не передаются. Адаптер может обслуживать два ВУ с 8-разрядным словом обмена и два с 4-разрядным словом. Направление передачи для каждого ВУ фиксировано и определяется управляющим словом, заносимым в адаптер перед началом обмена. В процессе работы МП двумя разрядами адреса выбирает порт, через который осуществляется ввод или вывод данных.

Во втором режиме происходит асинхронный обмен данными между МП и ВУ. Для этого необходимы линии для передачи сигналов квитирования, которые создаются из линий портов С1 и С2. В результате образуются два 12-разрядных канала: портам А и В, через которые осуществляется передача данных, дополнительно передается по три линии портов С1 и С2, через которые происходит обмен сигналами квитирования. Таким образом, в этом режиме адаптер может обслуживать два ВУ. Направление обмена, как и в первом режиме, определяется управляющим словом. Поскольку для одного сигнала квитирования требуется один разряд, в этом режиме возможна индивидуальная установка в «0» и «1» каждого из разрядов портов С1 и С2.

Адаптер является приемопередатчиком между МП и ВУ, поэтому сигналы квитирования используются для организации диалога адаптера как с ВУ, так и с МП. Вот, например, какие сигналы квитирования нужны при передаче данных из ВУ в МП. ВУ после выдачи слова данных выдает сигнал «Данные выданы». Чтобы ВУ не выдавало нового слова данных до тех пор, пока данные не запишутся в МП, адаптер выдает ВУ сигнал «Буфер заполнен» и записывает слово данных в порт. После этого адаптер выдает в МП сигнал прерывания «INT». МП, получив этот сигнал, переходит к выполнению подпрограммы обслуживания прерывания, в которой имеется команда ввода данных из порта. Получив эту команду, адаптер снимает сигнал прерывания, а по окончании сигнала RD, свидетельствующего о завершении чтения слова данных, снимает сигнал «Буфер заполнен». После этого ВУ может переходить к посылке следующего слова. Аналогичные три сигнала квитирования требуются и для пересылки данных из МП в ВУ.

Для режима двунаправленного асинхронного обмена необходимы уже не три, а пять сигналов квитирования. Поэтому в этом режиме адаптер может обслуживать только одно ВУ. Для передачи слова данных используется порт А. Для передачи сигналов квитирования ему выделяются пять линий порта С.

Параллельный интерфейсный адаптер используется для связи микропроцессорной системы с удаленными не более чем на 15 м ВУ. Такая связь обычно осуществляется через радиальный параллельный интерфейс ИРПР. Шина данных этого интерфейса может быть 8- или 16-разрядной. Аппаратные средства для реализации этого интерфейса могут быть построены с использованием рассмотренной БИС или ее более современных аналогов.