Сокращенное обозначение групп уго

4.1. Для уменьшения объема документации допускается сокращенное обозначение групп УГО.

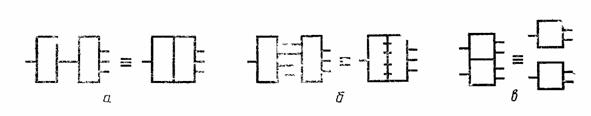

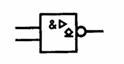

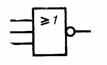

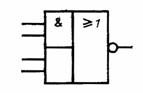

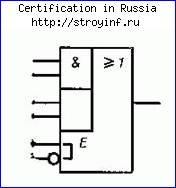

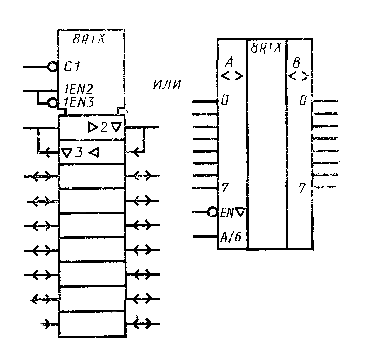

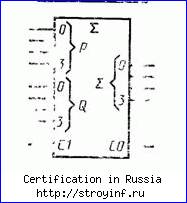

4.2. УГО элементов могут быть изображены совмещенно, прилегая друг к другу одной или двумя сторонами, параллельными распространению информации (черт. 16а). При этом логическое соединение между данными элементами отсутствует.

Примечание. Допускается изображать УГО элементов с общей стороной, перпендикулярной к распространению информации (черт. 16б). В этом случае существует хотя бы одно логическое соединение между данными элементами. Логические соединения следует указывать в соответствии с приложением 4. При отсутствии таких указаний считается, что имеется только одно логическое соединение между данными элементами (черт. 16в).

Черт. 16

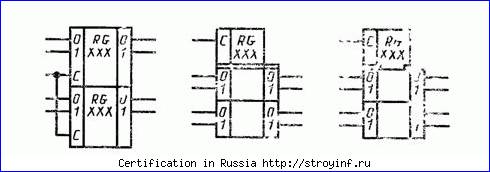

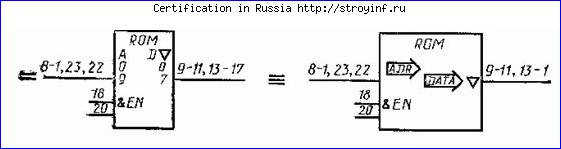

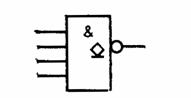

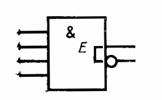

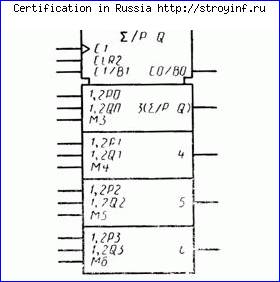

4.3. УГО группы однотипных элементов, изображенных совмещение и имеющих одинаковую информацию и общие выводы, могут содержать общий графический блок-блок управления (приложение 3). Допускается обозначать блок управления, как показано на черт. 17.

Черт. 17

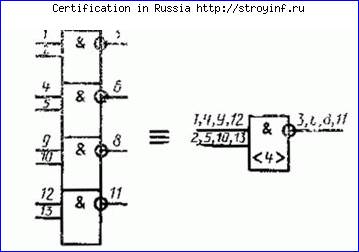

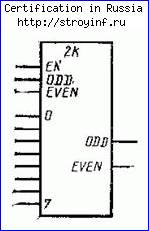

4.4. В группе элементов, изображенных совмещенно и содержащих одинаковую информацию в основном поле УГО, последнюю помещают в верхнем УГО (черт. 18а). Допускается отделять такие элементы друг от друга штриховой линией (черт. 18б).

Две последовательные группы элементов следует изображать, как показано на черт. 18в. Сокращенное обозначение группы из пар элементов показано на черт. 18г.

Группу элементов с идентичными выводами (входами и выходами), имеющих общий блок управления и не имеющих его, допускается изображать, как показано на черт. 18д и черт. 18г соответственно.

Черт. 18

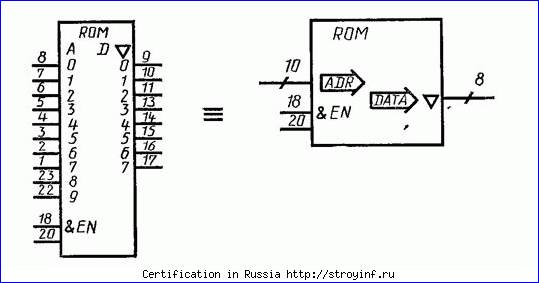

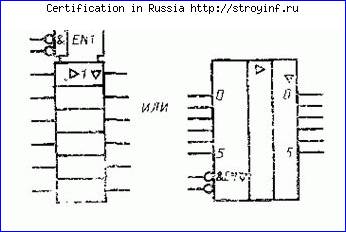

4.5. В схемах, имеющих элементы с большим числом выводов одного функционального назначения, допускается сокращенное обозначение таких элементов (черт. 19).

| Номер вывода | ||||||||||

| Метка вывода | А0 | А1 | А2 | A3 | А4 | A5 | A6 | А7 | A8 | A9 |

| Номер вывода | ||||||||||

| Метка вывода | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

Черт. 19

Примечания:

1. Записи выводов 13-17 и 13... 17 тождественны.

2. Таблицу (первый способ сокращенного обозначения элементов) следует помещать на поле схемы.

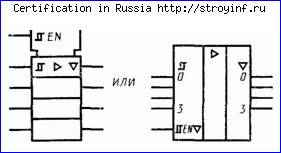

4.6. В схемах с повторяющимися элементами допускается также применять пакетный метод сжатия информации, т. е. пакетное изображение УГО элементов и линий их связи.

4.6.1. Пакет элементов-это группа однотипных элементов, изображенных в виде одного УГО. Пакет сигналов-это группа сигналов (логических связей элементов), изображенных одной линией. Пакеты элементов и сигналов поясняют на схеме при помощи пакетов информации,

4.6.2. Пакет информации-это краткое перечисление следующих данных:

идентификаторов сигналов (логических связей элементов);

конструктивных адресов элементов и сигналов;

координат элементов на схеме;

количество элементов или сигналов в пакете и т. д.

4.6.3. Краткая запись пакета информации может быть представлена следующим образом:

0,1; 0,1; 0,1; 0,1= (0,1) 4-последовательность 0,1 повторяется 4 раза;

0, 0, 0, 1, 1, 1 =3 (0,1)-каждый элемент указанной последовательности повторяется 3 раза подряд.

4.6.4. Пакетное изображение информации применяют при одновременном выполнении следующих условий:

однотипность элементов в группе;

однотипность входных и выходных сигналов элементов группы;

регулярность сигналов в каждом пакете, допускающая их удобное перечисление.

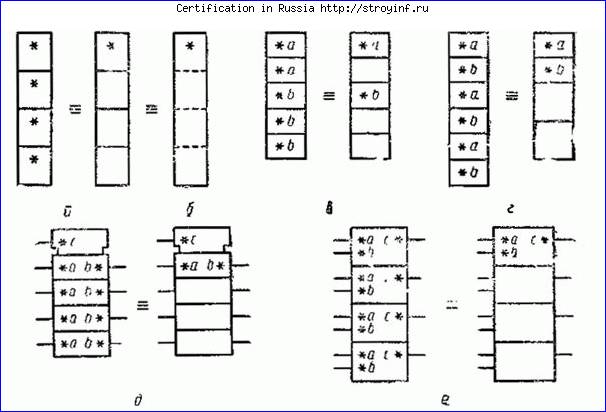

4.6.5. Внутри основного поля УГО пакета элементов помещают:

в первых трех строках информацию-по ГОСТ 2.708;

в последующих строках информацию о пакете.

При недостатке места в основном поле информацию о пакете элементов допускается помещать на поле схемы. Например, справа от УГО пакета элементов.

Пример УГО пакета элементов приведен на черт. 20.

Черт. 20

ПРИМЕРЫ УГО ЭЛЕМЕНТОВ

5.1. Примеры УГО элементов приведены в табл. 6-15 для соглашения положительной логики. Приведенные буквенные обозначения функций и меток выводов элементов являются обязательными, за исключением альтернативных, приведенных в табл. 2 или в табл. 4 (в круглых скобках). При этом допускается не указывать порядковые номера в метках выводов при обозначении зависимости.

Порядок расположения меток выводов (групп меток выводов-при их наличии) является рекомендуемым.

Указатели выводов элементов приведены в предпочтительной форме 1 табл. 3, однако допускается использовать все формы указателей, приведенных в табл. 3.

5.2. Примеры УГО логических элементов приведены в табл. 6.

Таблица 6

| Наименование | Обозначение |

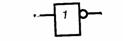

| 1. Элемент «НЕТ» |  |

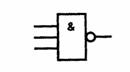

| 2. Элемент 3И-НЕ |  |

| 3. Элемент 2И-НЕ с открытым коллекторным выходом и повышенной нагрузочной способностью |  |

| 4. Элемент 3ИЛИ-НЕТ |  |

| 5. Комбинированный элемент 2И-ИЛИ с инвертированным выходом |  |

| 6. Элемент 4И-НЕТ с открытым коллектором на выходе |  |

| 7. Элемент 2И-ИЛИ с инвертированным выходом и расширительным входом |  |

| 8. Расширитель |  |

| 9. Элемент проверки четности или нечетности |  |

5.3. Примеры УГО приемопередающих элементов приведены в табл. 7.

Таблица 7

| Наименование | Обозначение |

| 1. Четыре шинных усилителя с двухпороговым входом и выходом на три состояния с общим входом разрешения третьего состояния |  |

| 2. Двунаправленный шинный приемопередатчик восьмиканальный |  |

| 3. Шестиканальный буферный элемент с тремя состояниями на выходе с сигналом разрешения по выходу |  |

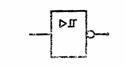

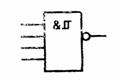

5.4. Примеры УГО гистерезисных элементов приведены в табл. 8.

Таблица 8

| Наименование | Обозначение |

| 1. Инвертирующий усилитель с порогом Шмитта |  |

| 2. Триггер Шмитта с логическим элементом 4И на входе |  |

5.5. Примеры УГО преобразователей (дешифраторов) и кодирующих устройств (шифраторов) приведены в табл. 9.

Таблица 9

| Наименование | Обозначение |

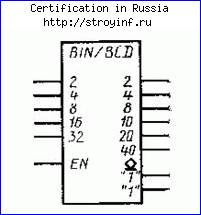

| 1. Преобразователь двоично-десятичного кода в десятичный код |  |

| 2. Преобразователь с трех линий на восемь |  |

| 3. Преобразователь двоичного кода в двоично-десятичный |  |

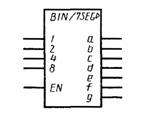

| 4. Преобразователь-усилитель двоичного кода в семисегментный Примечание. Допускается заменить строчные буквы прописными: А, В, С, D, Е, F, G |  |

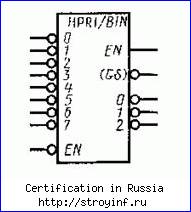

| 5. Кодирующее устройство приоритета (приоритетный шифратор) с 8 линий на 3 линии (GS-«групповой сигнал») |  |

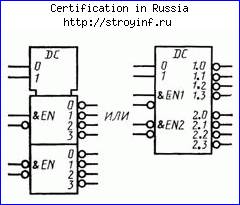

| 6. Два дешифратора, принимающих двухразрядный код. Примечание. Допускается обозначение дешифраторов А и В, которые изображаются в качестве групповой метки выходов соответствующего дешифратора |  |

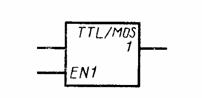

| 7. Преобразователь уровней ТТЛ в уровни МОП |  |

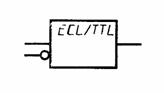

| 8. Преобразователь уровней ЭСЛ в уровни ТТЛ Примечание к пп. 7 и 8. Обозначение функции преобразователя сигналов */* может быть заменено обозначением *//*, если необходимо указать наличие гальванической связи между его входами и выходами |  |

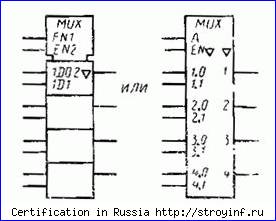

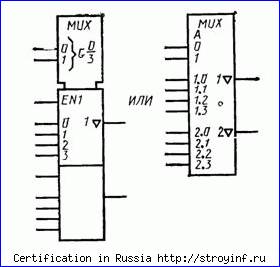

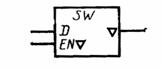

5.6. Примеры УГО мультиплексоров и демультиплексоров, а также коммутаторов цифровых и аналоговых сигналов приведены в табл. 10.

Таблица 10

| Наименование | Обозначение |

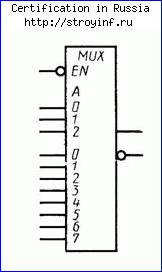

| 1. Мультиплексор на 8 входов со стробированием Примечание. Вход стробирования EN допускается обозначать STR |  |

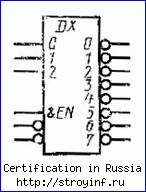

| 2. Демультиплексор на 8 линий |  |

| 3. Мультиплексор четырехканальный по два входа каждый |  |

| 4. Мультиплексор двухканальный по 4 входа каждый. Примечание к пп. 3, 4. При обозначении каналов мультиплексора не порядковыми номерами (1, 3 и т. д.), а буквами А, В и т. д.) для устранения неоднозначности понимания входу адреса данных присваивается метка «Выбор»: SELили SE |  |

| 5. Электронный коммутатор |  |

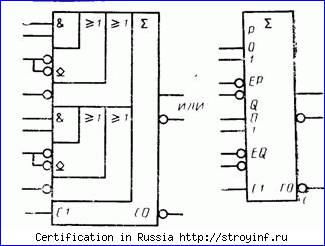

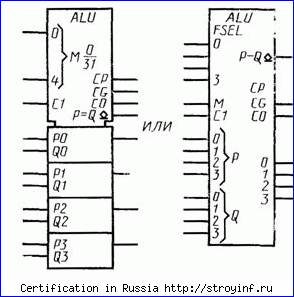

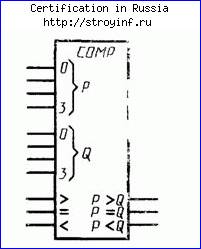

5.7. Примеры УГО арифметических элементов приведены в табл. 11.

Таблица 11

| Наименование | Обозначение |

| 1. Полный одноразрядный сумматор |  |

| 2. Четырехразрядный сумматор-вычитатель |  |

| 3. Полный сумматор на 4 бита |  |

| 4. Четырехразрядное скоростное АЛУ |  |

| 5. Генератор ускоренного переноса для АЛУ |  |

| 6. Четырехразрядный цифровой комларатор |  |

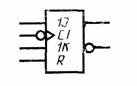

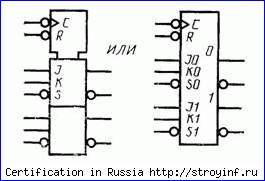

5.8. Примеры УГО триггеров (бистабильных элементов) приведены в табл. 12.

Таблица 12

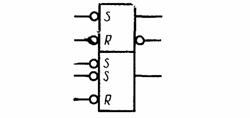

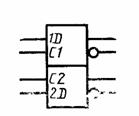

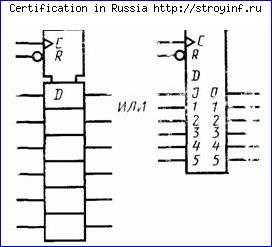

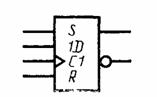

| Наименование | Обозначение |

| 1. Два триггера с раздельным запуском (RS-типа), один с дополнительным входом |  |

| 2. Два триггера задержки D-типа |  |

| 3. Шесть D-триггеров с общими входами управления и сброса |  |

| 4. Триггер D-типа, запускаемый по фронту |  |

| 5. Триггер JК-типа, запускаемый по фронту |  |

| 6. Универсальный JK-триггер со структурой «мастер-помощник» | |

| 7. Два JK-триггера с общими входами управления и сброса |  |

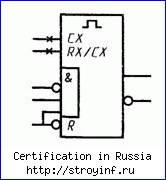

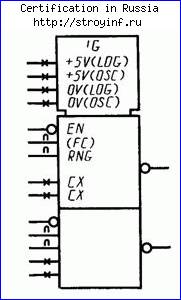

5.9. Примеры УГО моностабильных (мультивибраторов) и нестабильных элементов приведены в табл. 13.

Таблица 13

| Наименование | Обозначение |

| 1. Ждущий мультивибратор с перезапуском |  |

| 2. Два генератора, управляемых напряжением, с указанием выводов питания (LOG-питание цифровой части элемента, OSG-питание аналоговой части элемента, FC-управление частотой) |  |

5.10. Примеры УГО регистров и счетчиков приведены в табл. 14.

Таблица 14

| Наименование | Обозначение |

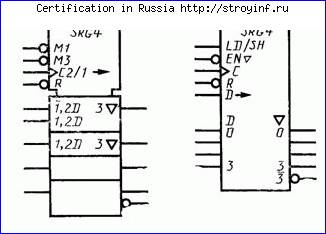

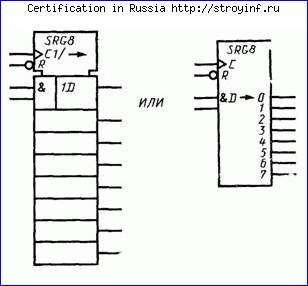

| 1. Сдвиговый 4-разрядный регистр с параллельными входами |  |

| 2. Сдвиговый 4-разрядный последовательно-параллельный регистр с прямым и дополнительным кодом на выходе (Т/С-вход переключения кода на выходах: прямой или дополнительный; P/S-вход, управляющий соединением разрядов регистров последовательно или параллельно) |  |

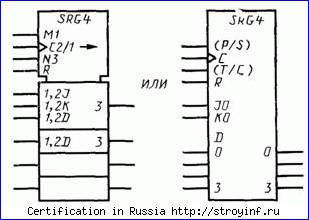

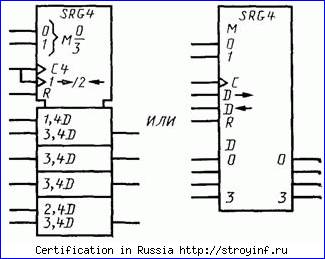

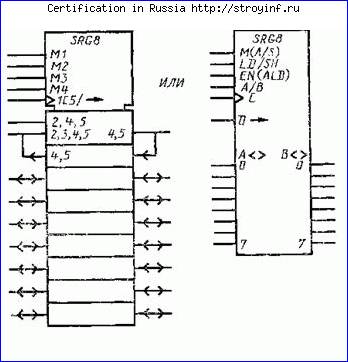

| 3. Сдвиговый 4-разрядный двунаправленный универсальный регистр |  |

| 4. Универсальный 8-разрядный регистр |  |

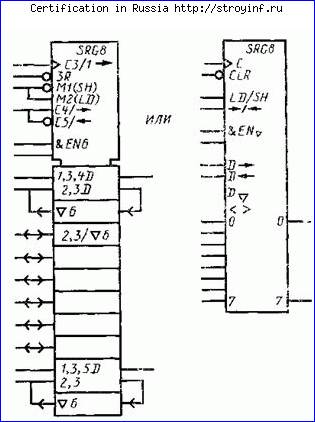

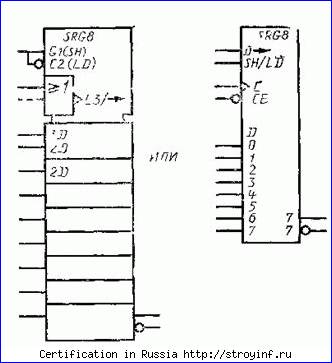

| 5. Сдвиговый 8-разрядный регистр с двойным последовательным входом и параллельными выходами |  |

| 6. Сдвиговый 8-разрядный универсальный регистр с последовательным и параллельными входами и выходами (A/S-вход, переключения режимов: асинхронного или синхронного; ALD-вход разрешения параллельной записи информации в канал ) |  |

| 7. Сдвиговый 8-разрядный регистр с параллельной загрузкой |  |

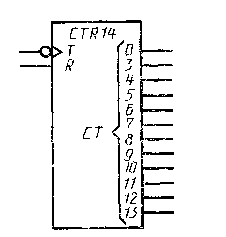

| 8. Двоичный 14-разрядный счетчик со сквозным переносом |  |

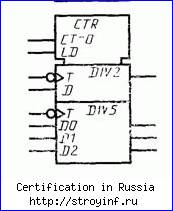

| 9. Асинхронный десятичный счетчик, состоящий из делителей на 2 и на 5 с параллельной записью |  |

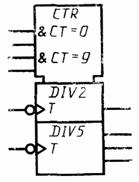

| 10. 4-разрядный асинхронный десятичный счетчик, состоящий из делителей на 2 и на 5 с предварительной установкой и синхронным сбросом |  |

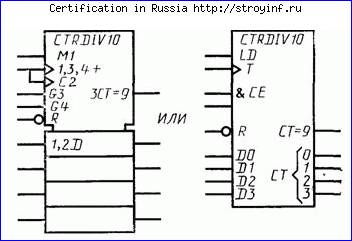

| 11. Синхронный десятичный счетчик с параллельной загрузкой |  |

| 12. Десятичный синхронный реверсивный счетчик |

5.11. Примеры УГО запоминающих устройств (ЗУ) приведены в табл. 15.

Таблица 15

| Наименование | Обозначение |

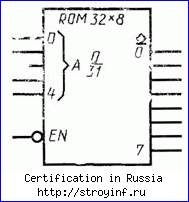

| 1. ПЗУ на 32 слова по 8 битов |  |

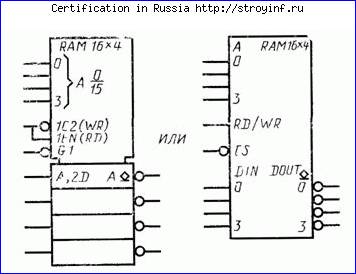

2. ОЗУ с произвольной выборкой на 16 слов по 4 бита Примечание. Обозначения выводов:  RD/WR и RD/WR тождественны RD/WR и RD/WR тождественны |  |

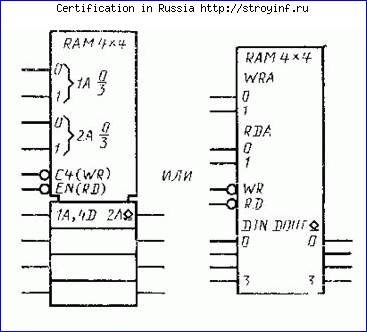

| 3. ОЗУ с произвольной выборкой на 4 слова по 4 бита с отдельной адресацией при записи и при считывании |  |

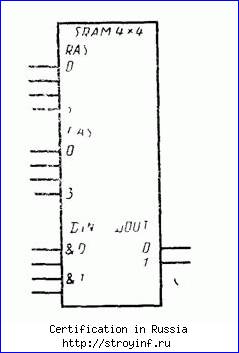

| 4. Статическое ОЗУ на 4 слова по 4 бита |  |

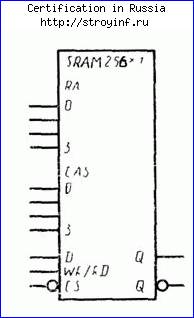

| 5. Статическое ОЗУ на 256 слов по 1 биту |  |

5.12. Соотношения размеров основных условных графических обозначений на модульной сетке приведены в приложении 5.

приложение 1

Рекомендуемое

ЛОГИЧЕСКОЕ СОГЛАШЕНИЕ

1. Двоичная логика имеет дело с переменными, которые могут принимать два логических состояния-состояния "логическая 1" (далее-LOG1) и состояния "логический 0" (далее-LOG0).

Символы логических функций, определенные данным стандартом, представляют собой связь между входами и выходами элементов в терминах логических состояний, не связанных с физической реализацией.

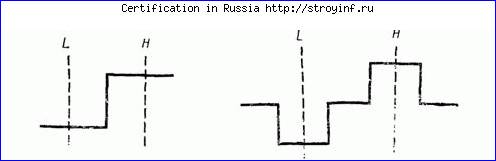

2. При конкретной физической реализации элементов логические состояния представляются физическими величинами (электрический потенциал, давление, световой поток и др.). В логике не требуется знание абсолютного значения величины, поэтому физическая величина идентифицируется просто как более положительная-H и менее положительная-L (черт. 21). Эти два значения называются логическими уровнями.

Черт. 21

3. Соответствия между данными понятиями устанавливаются следующими соглашениями: