Назначение и принцип работы микросхем дешифраторов

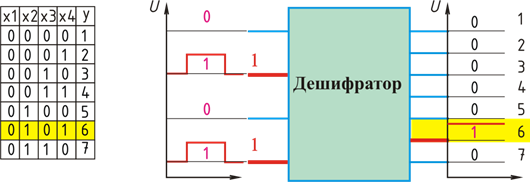

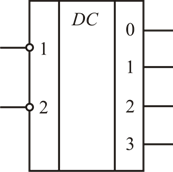

Дешифратором (декодером - Decoder) называется цифровое устройство, имеющее п входов и т выходов и преобразующее входной код в сигнал на одной отдельной выходной линии. Другими словами, в дешифраторе каждому предусмотренному набору входных сигналов соответствует один вполне определенный возбужденный выход (рисунок 5).

Дешифраторы являются преобразователями кодов, выполняющими преобразование двоичного или двоично-десятичного кодов в унитарный код. Унитарный код двоичного п - разрядного числа представляется 2п разрядами, только один из разрядов которого равен 1.

Рисунок 5 – Пояснение к принципу работы дишифратора

Дешифратор называется полным, если он имеет количество выходов m, связанных с количеством разрядов n входного двоичного числа следующим соотношением:

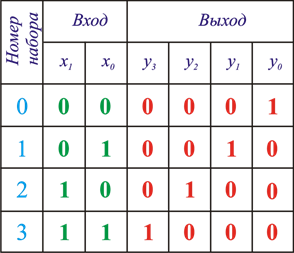

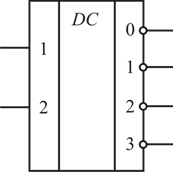

При этом на каждом из выходов появляется единица (т.е. выход возбужден) только в том случае, если на вход приходит соответствующая комбинация входных сигналов. Переключательная функция каждого выхода является конституентой единицы (рисунок 6).

Рисунок 6 – Таблица истинности двухразрядного дешифратора

Переключательная функция двухразрядного шифратора имеет следующий вид

;

;  ;

;  ;

;

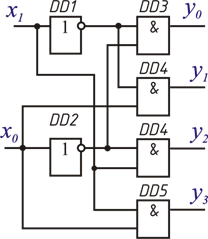

Реализация переключательных функций на базисе логических элементов «И», «НЕ» и условное графическое обозначение дешифратора приведены на рисунке 7.

Рисунок 7 - Реализация переключательных функций на базисе «И», «НЕ» и условное графическое обозначение дешифратора

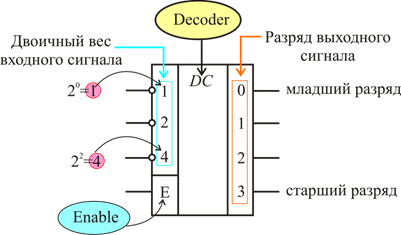

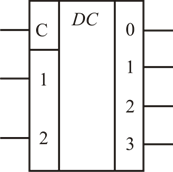

Дешифраторы могут иметь прямые и инверсные выходы. В зависимости от наличия и отсутствия сигнала синхронизации дешифраторы могут быть синхронными и асинхронными (рисунок 8).

Рисунок 8 – Условное графическое обозначение микросхем дешифраторов

Реализация полных дешифраторов с большим числом п в интегральном исполнении осложняется проблемой размещения большого числа выводов на корпусе микросхемы.

Задача дешифрирования при большом числе входных переменных может быть решена путем построении нескольких ступеней. Соответственно схемы дешифраторов такого типа называют многоступенчатыми. В зависимости от применяемой элементной базы многоступенчатые схемы могут быть построены на элементах дискретной схемотехники, либо же с использованием микропроцессорной техники.

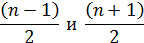

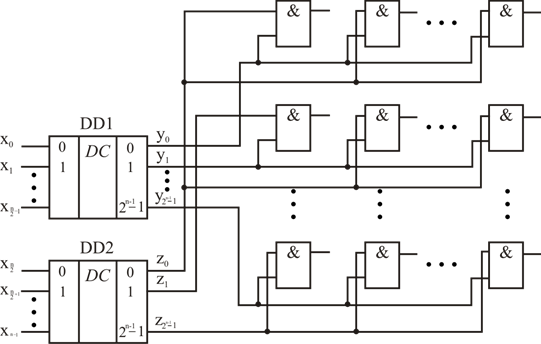

Применительно к первому случаю рассмотрим вариант построения двухступенчатых дешифраторов (рисунок 9). При построении такого п - разрядного дешифратора п - входные логические переменные делятся на две подгруппы по  переменных в каждой, если количество переменных четное, или по

переменных в каждой, если количество переменных четное, или по

переменных в каждой, если п - нечетное число. Для каждой подгруппы строится одноступенчатый дешифратор. После чего выводы дешифраторов объединяются схемой «И».

Рисунок 9 – Двухступенчатый дешифратор

В качестве особенностей приведенной схемы можно отметить простоту решения и анализа схемы, с одновременной схемотехнической сложностью. Наличия больших задержек сигналов, за счет того, что используется большое количество дискретных элементов. Схема характеризуется большим энергопотреблением, низкой надежностью и большими массогабаритными характеристиками.

Реализация второго способа представлена на рисунке 10. Как видно из рисунка все схемотехническое решение сводится к использованию в качестве шифратора второй ступени микроконтроллера.

Основными параметрами, по которым производится сравнение различных схем дешифраторов, являются время задержки сигнала в процессе дешифрации и аппаратурные затраты.

Поэтому многоступенчатые схемы дешифраторов обладают несомненным достоинством в экономии аппаратурных затрат, но проигрывают по сравнению с одноступенчатыми схемами во времени задержки сигнала.

Буквенное обозначение микросхем дешифраторов - ИД.

Рисунок 10 – реализация схемы двухступенчатого дешифратора на микроконтроллере