Jtag-интерфейс и системные функции на его основе

Важной характеристикой современных приборов (не только МП и ПЛ, но и других типов БИС) является поддержка JTAG-интерфейса. Исторически JTAG-интерфейс появился как название специальной группы, созданной по инициативе фирмы "Texas Instrument", для выработки стандарта на производство тестопригодных БИС(Joint Test Action Group - JTAG). Результатом работы этой группы явился Принятый в 1990 году стандарт IЕЕЕ Std.1149.1.

Предложенный стандарт имел два различных аспекта: один состоял в разработке протокола и принципов обмена информацией между БИС, соединенными в последовательную цепочку, а другой состоял в специальной (тестово ориентированной) организации связи между содержимым БИС и её внешними контактами. Использование подобной организации выходных контактов и возможность подачи (съема) информации, находящейся в цепочке, на (с) границы БИС для задач тестирования межсоединений БИС без физического доступа к каждому её выводу получил название метода граничного сканирования (Boundary Scan Testing-BST). Термин «граничное сканирование» представляется авторам более точно соответствующим задаче сканирования состояния границы между основными элементами ВИС и оборудованием, расположенным вне БИС, чем используемый иногда термин "периферийное сканирование".

Рассмотрим более детально идеи метода граничного сканирования.

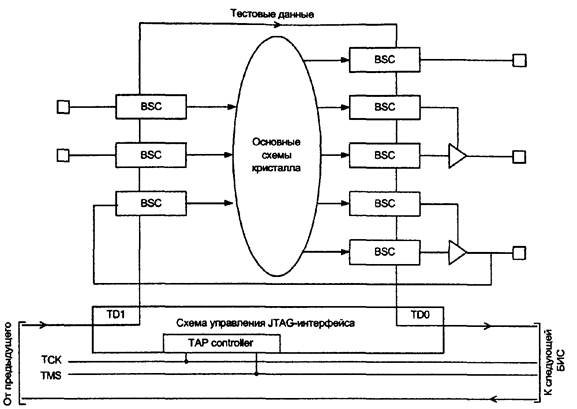

На рис. 8.7 показана организация ВИС, поддерживающая метод BST; рисунок позволяет понять основную концепцию граничного сканирования. Ячейки сканирования (BSC — Boundary Scan Cells) размещены между каждым внешним выводом микросхемы и схемами кристалла, образующими собственно БИС. Ячейки, с одной стороны, обеспечивают прием, сохранение или выдачу тестовой информации JTAG цепочки, а другой стороны, обеспечивают различные режимы взаимодействия между внешними контактами ВИС, запоминающими триггерами ячейки BSC и основными (внутренними) схемами кристалла.

Метод BST задумывался для выполнения следующих тестовых процедур: проверять функциональную пригодность БИС с помощью встроенных в них тестовых цепей; проверять качество соединений между различными контактами БИС, смонтированных на печатной плате; считывать или устанавливать сигналы на выходных контактах БИС в штатном режиме работы БИС. Выполнение команд тестирования базируется на соответствии длины регистров приема/передачи информации (встроенных в каждую БИС, поддерживающую методы BSТ) и числа тестируемых контактов БИС, а также на возможности различным образом настраивать взаимодействие разрядов этих регистров с внутренней структурой БИС и внешними контактами.

Ячейки BCS обеспечивают реализацию следующих режимов:

• за счет разрыва соединения внешних контактов и внутреннего содержимого БИС и подачи внутрь БИС информации из ячейки BCS, которая соответствует поступившим из цепочки данным, а затем фиксации в ячейке ВВС результирующей информации, которую впоследствии можно передать в JTAG-цепочку, могут быть организованы режимы самотестирования БИС, режимы программирования или чтения внутрисхемных ЗУ и т. д.;

• за счет разрыва соединения внешних контактов и внутреннего содержимого БИС и подачи на внешние выходные контакты БИС сигналов из ячейки BSC соответствующих поступившей из JTAG-цепочки информации, а затем фиксации в ячейках BSC информации, соответствующей состоянию сигналов на внешних контактах БИС, и возможности передачи этой информации в JTAG-цепочку, могут быть организованы режимы тестирования соединения БИС между собой;

Рис. 8.7. Организация граничного сканирования

• за счет фиксации в ячейках BSC сигналов от всех контактов БИС в задаваемый из JTAG цепочки момент времени при сохранении соединения внешних контактов и внутреннего содержимого БИС, и независимости считывания этой информации в JTAG-цепочку от штат- ной работы БИС, может осуществляться тестирование штатного режима работы БИС.

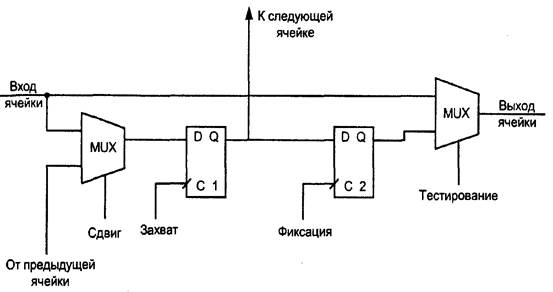

Схема сканирующей ячейки (рис. 8.8.) содержит два мультиплексора и два D-триггера. Триггер TD1 является триггером в сдвигающем регистре данных JTAG-цепочки, в состоянии ввода/вывода данных информация сдвигается по цепочке триггеров BSC-ячеек. В этих же триггерах может фиксироваться входная информация BSC-ячеек. Триггер TD2 является триггером-защелкой, буферизирующим данные основного сдвигающего регистра. Работа ячейки зависит от режима использования. В рабочем режиме информация со входа ячейки передается на выход, соединяя выходной контакт БИС с внутренними ресурсами БИС, но при этом входная информация ячейки может фиксироваться в TD1 сдвигающего регистра. В большинстве тестовых режимов вход и выход ячейки разъединены. Входная информация ячейки может при этом фиксироваться в триггере TD1, а выходная информация будет определяться содержимым триггера TD2.

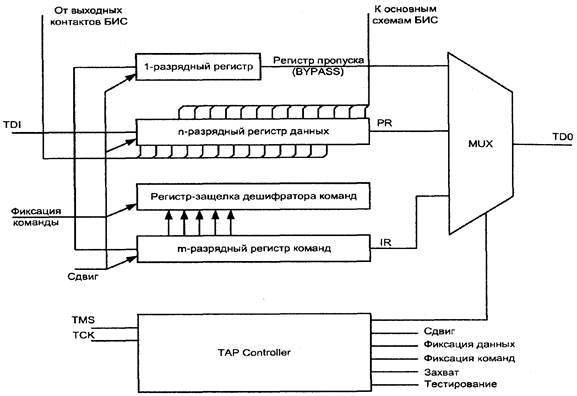

Структурная схема устройства управления граничным сканированием (ГС) приведена на рис. 8.9. Из рисунка видно, что основными и обязательными элементами устройства управления являются три регистра — регистр команд (RI), регистр пропуска (Bypass) и регистр данных (RD), выходной мультиплексор(MUX) и контроллер управления (ТАР Controller). В цикле записи команд в БИС JTAG-цепочки регистр команд фиксирует следующую команду к исполнению (как правило, после включения питания в этот же регистр заносится идентификационный код БИС). Одноразрядный регистр пропуска обеспечивает в режимах загрузки/выгрузки команд или данных обход при сдвигах многоразрядных данных или команд, не относящихся к данной БИС. Регистр данных является источником или приемником информации при всех действиях в JTAG-цепочках.

Рис. 8.8. Схема ячейки ВВС

Структура сканирующих ячеек позволяет ввести для каждой возможной тестовой процедуры выполнение определенной команды. Стандартом предусмотрена обязательность поддержания четырех команд граничного сканирования: ЕХТЕSТ, SAMPLE/PRELOAD, при этом допускается введение дополнительных команд, упрощающих работу с JTAG-цепочками или тестируемыми БИС.

Для решения задач самотестирования БИС предусмотрены две команды стандарта JTAG — INTEST и RUNBIST. Команда INTEST проверяет функционирование БИС путем проверки данных, зафиксированных в регистрах сканирования DR после прохождения данных (загруженных перед исполнением команды в регистр DR) через основные схемы кристалла. Команда RUNBIST производит тестирование кристалла без привлечения каких-либо внешних данных, данные, зафиксированные в регистре DR после завершения команды, однозначно определяют исправное состояние БИС.

Для тестирования внешних соединений на печатной плате предусмотрено использование команды ЕХТЕSТ. Исполнение команды предполагает отключение внутренних схем кристалла от внешних контактов — сигнал "Тестирование" на рис. 8.9. Состояния выходных контактов БИС определяются информацией, находящейся в регистрах данных DR БИС. В начале выполнения команды (при прохождении состояния автомата CAPTURE-DR) в буферных регистрах DR на фронте сигнала «Захват» фиксируется состояние сигналов на внешних контактах БИС, после этого зафиксированные данные (в состоянии автомата SHIFT-DR) при сигнале "Сдвиг" на мультиплексоре 1 могут выдвигаться из БИС и замещаться на вновь подаваемые данные, и наконец при завершении команды (при прохождении состояния UPDATE-DR) обновляется состояние регистров DR (а значит и состояния выходных контактов БИС) на фронте сигнала «Фиксация». Хотя команда ЕХТЕSТ позволяет производить тестирование межсоединений без привлечения каких-либо дополнительных команд, чаще всего она используется совместно с командой SAMPLE/PRELOAD, выполняющей роль команды, загружающей информацию в регистр данных.

Для сканирования сигналов, присутствующих на внешних контактах БИС, предусмотрена команда SAMPLE/PRELOAD. Поскольку исполнение команды не предполагает отключение внутренних схем кристалла от внешних контактов — инверсное состояние сигнала «Тестирование» на рис. 8.9, то в начале выполнения команды (при прохождении автоматом состояния CAPTURE-DR) в буферных регистрах DR по фронту сигнала «Захват» фиксируется состояние сигналов на внешних контактах БИС.

Рис. 8.9. Схема устройства управления командами граничного сканирования

Эти сигналы соответствуют штатному режиму работы БИС. Интерпретация содержания такого мгновенного «снимка состояния» сигналов на границе тестируемой БИС зависит от состояния других БИС, связанных с тестируемой. Если все БИС находятся в рабочем режиме, то содержание «снимка» отражает протекание штатных режимов в системе и обычно используется для целей отладки. Возможность создания произвольной конфигурации тестируемой системы - одна часть БИС формирует тестовые выходные сигналы, а другая часть БИС системы находится в рабочем режиме, позволяет организовывать совместное тестирование межсоединений и функционирования внутренних схем ВИС.

Команды СLАМР и HIGHZ позволяют расширить возможности совмещенного тестирования межсоединений и рабочего состояния части БИС в проверяемой системе. Команда HIGHZ переводит все выходные контакты БИС в Z-состояние и переводит БИС в состояние BYPASS. Аппаратная реализация такой команды требует минимальных затрат, но её использование особенно эффективно при тестировании систем с шинной организацией для БИС микропроцессоров реализация такого состояния их выходных контактов носит название "In-Circuit emulation" и упрощает использование внешних отладочных эмуляционных средств.

Команда СLАМР устанавливает на выходных контактах БИС значения, соответствующие данным регистра DR, и переводит БИС в состояние BYPASS.

Команда BYPASS позволяет установить устройство управления JTAG-интерфейсом в состояние сквозного пропуска данных через БИС. Команда соответствует отключению БИС от процедур тестирования без изъятия БИС из JTAG -цепочки.

Основу любого устройства управления JTAG-командами составляет контроллер тестирующего порта доступа (ТАР Controller). ТАР Controller — синхронный конечный автомат, изменение состояний которого происходит по состоянию управляющего сигнала - JTAG цепочки сигнала ТМS, фиксируемого по переднему фронту тактового сигнала цепочки — ТСК. Контроллер формирует выходные сигналы, управляющие поведением ячеек BSC — сдвиг, захват, тестирование.

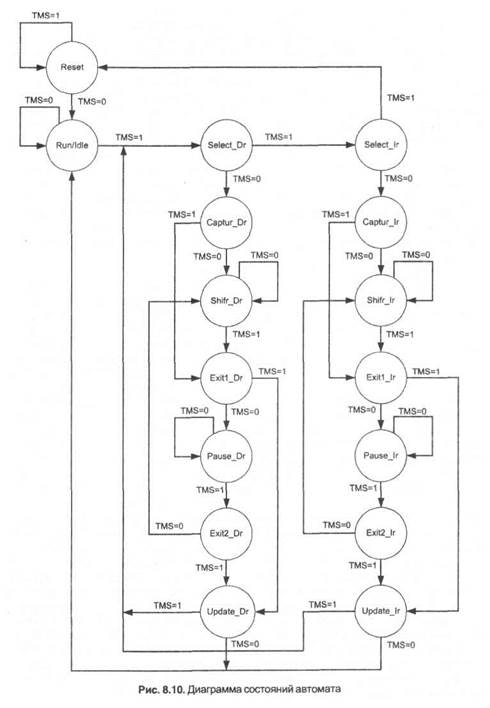

Диаграмма состояний автомата приведена на рис. 8.10. Некоторые пояснения к диаграмме. Условия переходов—значение сигнала ТМS, показано на диаграмме цифрами "0" или "1". В диаграмме состояний можно выделить четыре базовых фрагмента — состояние TEST-LOGIC_RESET (сброс логики тестирования), RUN-TEST\IDLE (состояние ожидания или выполнение внутренних тестов), режим управления вводом/выводом данными (семь состояний от SELECT-DR-SCAN до UPDATE-DR) режим управления вводом команд, чтением состояния от SELECT-IR-SCAN до UPDATE-DR. Основу режимов управления образу- ют три состояния: 1) состояния фиксации в выдвигаемых регистрах данных на момент начала фрагмента (состояние CAPTURE-DR или CAPTURE-IR); 2) состояния выдвигания зафиксированной информации из БИС и вдвигания новой информации в БИС (состояние SHIFT-DR или SHIFT-DR); 3) состояния фиксации новой информации (состояние UPDATE-DR или UPDATE-IR) на момент завершения фрагмента. Состояния PAUSE-DR и PAUSE-IR позволяют приостанавливать продвижение информации в цепочке на произвольное число тактов синхронизации (например, для выполнения каких-либо действий в БИС с внешним тактированием). Состояния EXIT1-DR, ЕХIТ2-DR, ЕХIТ1-IR и ЕХIТ2-IR носят вспомогательный характер (в том числе для реализации альтернативных переходов), но могут оказаться полезными при реализации устройств управления расширенных вариантов интерфейса JTAG, соответствующих новым вводимым командами.

JTAG - интерфейс проектировался для организации информационной связи между произвольным числом БИС на печатной плате, в приборе и т.д. Основное требование при этом состояло в минимизации числа контактов БИС, необходимого для организации информационного обмена. Обычно используется четыре (реже пять) выделенных для JTAG- интерфейса контакта БИС. Эти контакты образуют так называемый порт доступа (Test Access Port-TAP) контроллера управления JTAG-интерфейса (ТАР Controller).

Контакты имеют следующие названия и функциональное назначение:

ТСК (Test ClocK input — синхронизация передачи данных и команд;

ТМS (Test Mode Select) — выбор режима передачи (считывание по переднему фронту ТСК);

TDI (Test Data Input— вход данных и команд (считывание по переднему фронту ТСК);

TDO (Test Data Output — выход данных, команд или состояния (изменение по заднему фронту по спаду ТСК);

ТRST(Test ReSeT — сброс в исходное состояние контроллера (ТАР Controller).

Если на печатной плате или в устройстве установлено несколько БИС, поддерживающих JTAG-интерфейс, то эти схемы могут быть объединены в так называемую JTAG-цепочку. Устройство управления JTAG-цепочкой за счет управления контактами ТМS и ТСК может установить автоматы ТАР контроллеров всех БИС в исходное состояние, загрузить различные команды в БИС, входящих в цепочку, загрузить требуемые данные и (или) прочитать данные из регистров данных.

Реализация возможностей, предоставляемых JTAG -интерфейсом, определяется правильной политикой на этапе подготовки проектной документации для печатных плат. Поскольку для некоторых типов БИС ПЛ контакты, предназначенные для организации JTAG-интерфейса являются опционными, желательно как минимум оставлять их резервными, а лучше ВЫВОДИТЬ на контактные площадки, чтобы при необходимости можно было объединить БИС, находящиеся на печатной плате и поддерживающие методы граничного сканирования в единую JТАG-цепочку. для некоторых ПЛ характерно отсутствие постоянно существующих ячеек граничного сканирования и необходимо на этапах контроля межсоединений загружать в подобные БИС специально подготовленную конфигурацию, которая и позволит воспользоваться методами граничного сканирования. Подобные мероприятия позволят в случае необходимости организовать тестирование межсоединений на изготовленной плате. Естественно, что все описанные выше возможности реализуются в том случае, когда управление БИС, входящими в состав JTAG-цепочки,

выполняется достаточно интеллектуальным контроллером, обеспечивающим подачу предварительно разработанных тестовых последовательностей и контроль получаемых в результате тестирования последовательностей. Тестовые последовательности, как правило, создаются специальным программным обеспечением. Программное обеспечение, автоматизирующее процесс подготовки тестовых последовательностей, опирается на реализованную на плате систему межсоединений и на возможности БИС, расположенных на этой плате. Целый ряд фирм разрабатывает и поддерживает программные пакеты, автоматизирующие указанные выше тестовые процедуры.

Транспортный аспект стандарта JTAG -интерфейса (стандарт IЕЕЕ Std.1149.1) позволил стандартизировать, во-первых, прием (передачу) информации в (из) БИС, входящих в JTAG -цепочку, а во-вторых, исполнение команд JTAG -контроллерами, входящими в состав каждой БИС-цепочки. В результате он оказался прекрасным инструментом для со здания расширенных версий JTAG -интерфейса (enhanced JTAG interface), позволив тем самым использовать JTAG -интерфейс не только для решения задач тестирования, но и для решения широкого круга других задач. Возможность адресного направления информации внутрь БИС, расположенной на печатной плате, и одновременное указание о запоминании этого потока информации как содержимого ПЗУ этой БИС, привел к введению специального термина для такой возможности применения JTAG -интерфейса — внутрисхемное программирование(ISP).Для использования термина ISP безразлично, является ли ПЗУ памятью команд МП или памятью конфигурации БИС ПЛ. Если же в БИС находится ОЗУ с целевым назначением использования как память конфигурации схемы программируемой логики, то для такого применения JTAG -интерфейса иногда используется термин- "внутрисхемное реконфигурирование" (ISR). Если БИС программируемой логики расположена на плате расширения с интерфейсом РСI, а поскольку по стандарту среди контактов таких плат предусмотрено наличие контактов JTAG -интерфейса, то появляется возможность репрограммировать конфигурацию БИС платы расширения, не вынимая платы из компьютера. Такая возможность получила название ISP, с совпадением аббревиатуры для внутрисхемного программирования. И, наконец, широкое распространение в последнее время находит использование JTAG -интерфейса для обмена информацией c фрагментами БИС, предназначенными для отладки общесистемных проблем, что позволяет говорить о внутрисистемной, внутрисхемной отладке. Последнее свойство реализуется, например, в САПР Qartus фирмы "Altera" для связи со встраиваемыми логическими анализаторами как в БИС программируемой логики этой же фирмы АРЕХ2ОК , так и для защелкивания до 32 сигналов между БИС. Для БИС ПЛ класса SОРС фирмы "Triscend" таким же путем (через JTAG интерфейс) возможна установка аппаратных точек останова для встроенного в БИС микроконтроллера и доступ к его основным программным элементам.