Типичные схемотехнические решения

Разработкой и производством микросхем программируемой логики занимаются десятки фирм, каждая из которых выпускает обычно одновременно несколько семейств микросхем. Семейства, в свою очередь, представлены совокупностью микросхем, отличающихся своими архитектурными и схемотехническими особенностями. Так образуется чрезвычайно большое число вариантов микросхем, и на первый взгляд сориентироваться в их многообразии достаточно сложно. Вместе с тем при внимательном рассмотрении обнаруживается, что для построения разных вариантов микросхем программируемой логики используется та или иная комбинация типичных элементов и блоков, число которых относительно невелико. Такие элементы и блоки рассмотрены ниже.

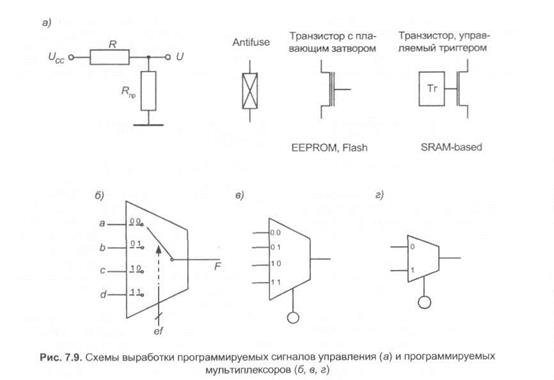

Простейшими элементами, обеспечивающими конфигурирование микросхем на заданное функционирование, являются рассмотренные ранее программируемые элементы связей (перемычки типа «antifuse», ЛИЗМОП-транзисторы с плавающим затвором, ключевые транзисторы, управляемые триггерами памяти конфигурации). Такие элементы могут просто замыкать или размыкать участки цепей, в которые они включены, либо входить в схемы резисторных делителей напряжения с программируемым коэффициентом деления для задания сигналов логического нуля или логической единицы. На рис. 7.9, а показан делитель напряжения, состоящий из резистора с постоянным сопротивлением R и программируемого сопротивления Rn, выходное напряжение делителя U = Ucc Rпр /(R + Rnp). В зависимости от программирования сопротивление Rnp имеет значения Rпр « R или Rпр » R. В первом случае напряжение U мало (близко к нулю) и с делителя снимается "сигнал логического нуля, во втором случае значение U близко к Uсс и соответствует логической единице.

Для конфигурирования межсоединений, а также построения логических блоков используются программируемые мультиплексоры. В первом из названных режимов (рис. 7.9, б) мультиплексор можно условно отобразить в виде переключателя, который под управлением адресующих входов (в данном случае это двухразрядное двоичное число ef) передает на выход Fодну из входных величин -а,b,с или d. На линии каждого входа отмечена комбинация адресующих величин, подключающая данный вход к выходу мультиплексора. В условном обозначении программируемого мультиплексора в режиме коммутации сигналов (рис. 7.9, в) факт программируемости обозначается кружком на адресующем входе. При программировании устанавливается определенный код еf и соответственно ему связь между выходом схемы и одним из входов. Для часто применяемых программируемых мультиплексоров размерности 2-1 условное обозначение имеет вид, изображенный на рис. 7.9, г. Комбинации адресующих величин против линий входов могут и не показываться, если в этом нет необходимости.

В п. 7.1.2 указано, что логические блоки CPLD выполняются как двухуровневые схемы И-ИЛИ, на входы которых подаются парафазные входные переменные. Логические блоки FPGA более разнообразны и могут представлять собою простые логические ячейки

(SLC, Small Logic Cells), схемы на основе мультиплексоров или табличные функциональные преобразователи (LUTs, Look-Up Tables). Подробнее логические (функциональные) блоки разных ИС ПЛ рассмотрены ниже, здесь же остановимся на способах повышения функциональной гибкости логической обработки сигналов, используемых как в FPGA, так и в CPLD.

Из числа приемов дополнительной обработки сигналов, получаемых от основных логических блоков, можно выделить следующие.

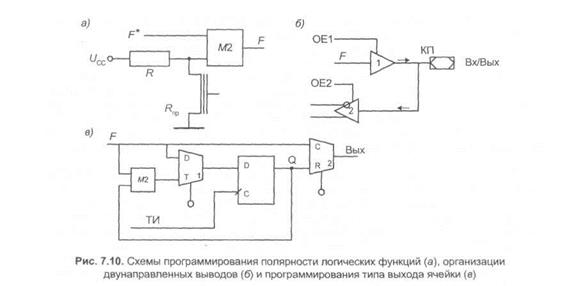

1. Программирование полярности вырабатываемых функций. Этот прием наиболее характерен для CPLD , реализующих функции в форме ДНФ (SOP). В этом случае можно «сыграть» на том, что логическая функция F и ее инверсия  не идентичны по сложности и выражения для них могут иметь существенно различные числа термов. Имея возможность перехода от прямых значений функций к их инверсиям и наоборот, можно выбирать для реализации в основном логическом блоке более простую из этих форм независимо от того, какая из этих двух функций понадобится в последующих операциях. Схемотехнически программирование полярности логических переменных осуществляется с помощью двух входового элемента сложения по модулю 2, на один из входов которого подается логическая переменная, а на второй - константа «О» или «1» (рис. 7.10, а). Схема программируется заданием определенного состояния ключевому транзистору Т. Если он открыт и находится в низковольтном состоянии, то напряжение на нижнем входе элемента М2 отображает логический нуль и F = F*

не идентичны по сложности и выражения для них могут иметь существенно различные числа термов. Имея возможность перехода от прямых значений функций к их инверсиям и наоборот, можно выбирать для реализации в основном логическом блоке более простую из этих форм независимо от того, какая из этих двух функций понадобится в последующих операциях. Схемотехнически программирование полярности логических переменных осуществляется с помощью двух входового элемента сложения по модулю 2, на один из входов которого подается логическая переменная, а на второй - константа «О» или «1» (рис. 7.10, а). Схема программируется заданием определенного состояния ключевому транзистору Т. Если он открыт и находится в низковольтном состоянии, то напряжение на нижнем входе элемента М2 отображает логический нуль и F = F*  0 = F*. Если же транзистор заперт, то на нижнем входе элемента Ш. действует высокое напряжение, близкое к Ucc, т. е. отображается сигнал логического нуля и F = F*

0 = F*. Если же транзистор заперт, то на нижнем входе элемента Ш. действует высокое напряжение, близкое к Ucc, т. е. отображается сигнал логического нуля и F = F*  1 = F*.

1 = F*.

2. Организация двунаправленных выводов. В зависимости от конкретного проекта для ИС ПЛ одной и той же сложности могут потребоваться различные соотношения чисел входов и выходов. Поэтому специализация выводов и жесткое разделение их на входы и выходы сужает функциональные возможности микросхемы. Вследствие этого широкое применение находят микросхемы с двунаправленными выводами, которые путем программирования можно сделать либо входами, либо выходами. Микросхема, имеющая т специализированных входов, n специализированных выходов и р двунаправленных выводов, может программироваться на число входов от т до т + р и на число выходов от n до n + р при условии, что в сумме число выводов не превысит m + n + р. Схемотехнически

это реализуется с помощью буферов, имеющих третье состояние (рис 7.10, б). Если сигналом ОЕ1 (Output Enable 1) буфер 1 разрешен, то вывод является выходом и переменная F поступает на внешний контакт (КП - контактная площадка). Если буфер 1 находится в третьем состоянии «отключено», а буфер 2 разрешен сигналом ОЕ2, то вывод служит входом. При этом входной сигнал преобразуется буфером 2 в парафазный. При активном буфере 1 через буфер 2 можно подавать в схему сигнал обратной связи, что также существенно увеличивает функциональные возможности микросхемы.

Если сигнал управления буфером 1 вырабатывается как терм, формируемый в матрице И, то возможны такие варианты программирования функций вывода:

• вывод является входом, если терм ОЕ1 запрограммирован на константу 0;

• вывод является простым выходом, если терм ОЕ1 запрограммирован на константу 1, а сигнал ОЕ2 запрещает буфер 2;

• выходной сигнал подается как сигнал обратной связи, если разрешена работа обоих буферов, причем выходной сигнал может вырабатываться постоянно при неизменном разрешающем сигнале ОЕ1 или появляться только в момент возникновения определенной комбинации входных переменных матрицы И соответственно программированию терма ОЕ1.

3. Введение триггеров. Еще один прием обогащения функциональных возможностей микросхем программируемой логики - введение триггеров в их макроячейки (это понятие объясняется ниже) или непосредственно в логические блоки, причем чаще всего логическое функционирование триггеров программируется. Обычно триггеры строятся на основе триггера типа D и дополнительных логических элементов. Триггеры типа D легко обеспечивают режим триггера типа Т (рис. 7.10, в) с помощью подключенных к ним элемента М2 и программируемого мультиплексора 1.

Если мультиплексор запрограммирован на передачу сигнала от верхнего входа D, то триггер работает как триггер типа D , принимая по разрешению тактового сигнала ТИ значение F. Если мультиплексор 1 запрограммирован на передачу сигнала от нижнего входа, то под воздействием тактового сигнала при F = 0 триггер принимает свое собственное состояние Q, т. е. находится в режиме хранения, а при F= 1 - инверсию своего состояния, т. е. переключается. Отсюда видно, что триггер функционирует как синхронный Т-триггер, ко входу Т которого подключен сигнал F.

В ряде микросхем программируемой логики возможно программирование триггеров на режимы не только D и Т, но и JK, RS (с помощью дополнительной внешней логики).

Для обогащения функциональных возможностей микросхем часто программируется тип выхода как комбинационный (combinatorial) или регистровый (registered). Для этого также используются программируемые мультиплексоры. Из рис. 7.10, в видно, что при программировании мультиплексора 2 на передачу сигнала от входа С реализуется комбинационный вариант выхода, когда величина F в обход триггера передается прямо на выход, а при передаче через мультиплексор сигнала от входа R реализуется регистровый вариант выхода (выходной сигнал снимается с триггера).

Перечисленные приемы повышения функциональной гибкости микросхем программируемой логики являются наиболее общими и характерны для многих из них. Ряд приемов более специфичен, такие приемы будут рассмотрены при описании конкретных разновидностей микросхем или их блоков.

7.3.2. СВОЙСТВА ИС ПЛ, ВАЖНЫЕ ДЛЯ ИХ ПРИМЕНЕНИЯ В СОСТАВЕ СИСТЕМ

Ряд свойств микросхем программируемой лотки не связан непосредственно с их логическим функционированием, но имеет важное значение при их использовании в системе. К таким (системным) свойствам относятся следующие.

Уровни питающих напряжений.Имеются веские причины для перехода ко все меньшим напряжениям как для питания микросхем в рабочих режимах, так и для программирования таких элементов, как ЛИЗМОП-транзисторы в схемах с памятью конфигурации типов EPROM и EEPROM. Если сравнительно недавно типовым значением питающего напряжения было 5 В, то сейчас все больше используются схемы с напряжениями питания 3,3; 2,5; 1,8 и даже 1,6 В. Кроме того, исключаются требования повышенных напряжений для программирования, и все процессы в схемах обеспечиваются с помощью внутренних средств от единого источника внешнего питания.

Наличие режимов различного энергопотребления.При работе того или иного блока для поддержания его быстродействия требуются определенные затраты энергии (для быстрых переключений требуется быстрый перезаряд неизбежно существующих паразитных емкостей, т. е. нужны большие токи, обеспечивающие требуемые длительности переходных процессов). При отсутствии переключений в той или иной схеме можно резко снизить ее энергопотребление, так как для сохранения неизменного логического состояния достаточны микротоки. Кроме двух указанных режимов можно создавать и ряд промежуточных, что широко используется в микросхемах программируемой логики. Активные режимы могут программироваться в разных вариантах (максимального быстродействия и номинального быстродействия с меньшей потребляемой мощностью). Пассивные режимы также часто имеют несколько подрежимов (покоя, когда схема не переключается, но готова к быстрому вхождению в рабочий режим, глубокого понижения мощности, когда потребление энергии чрезвычайно мало, но переход в активный режим занимает относительно большое время, и т. д.).

Интересно отметить, что с помощью несложных логических элементов схемы могут автоматически переходить из одного режима в другой, выявляя факт изменения информационных сигналов и реагируя на него увеличением рабочих токов.

В число программируемых величин может входить так называемый Turbo bit, задающий один из двух режимов, различающихся по соотношению скорость/мощность.

Наличие или отсутствие в микросхеме средств поддержки интерфейса JTAG.Первоначальные версии этого интерфейса обеспечивали тестирование систем методом периферийного (граничного) сканирования, более поздние расширенные версии, ориентированные на микросхемы программируемой логики, позволяют через интерфейс JTAG конфигурировать схемы с триггерной памятью, для чего требуется лишь загрузка в память конфигурации загрузочного файла.

Свойство программируемости в системе.Схемы, обладающие этим свойством, называются In-System Programmable (ISP). Свойство ISP могут иметь микросхемы с триггерной памятью конфигурации (заметим, что термин «программируемость» появился в этом абзаце в связи с его наличием в английском термине ISP, по существу же он означает то же самое, что и термин «конфигурируемость»). Поскольку триггерная память теряет свое содержимое при выключении питания, схемы типа SRAM-based программируются при каждом включении питания. Свойство ISP означает, что реконфигурацию можно производить без изъятия микросхемы из системы, перезагружая файл конфигурации, что возможно и во время функционирования системы. Такая возможность позволяет строить системы с многофункциональным использованием одних и тех же программируемых микросхем в качестве разных блоков системы, если эти блоки не используются одновременно, а также и другие варианты адаптивных систем.

Наличие средств защиты от считывания данных конфигурации.Такие средства имеют разную степень защиты. В простейшем случае предусматривается бит защиты или несколько таких битов.

Программирование крутизны фронтов.Известно, что одной из острых проблем при реализации цифровых устройств и систем является борьба с помехами, в том числе создаваемыми самими схемами этих устройств и систем. С целью снижения уровня возникающих импульсных помех для мощных буферов, прежде всего тех, которые формируют выходные сигналы кристалла, вводится программирование крутизны фронтов. Бит SLC (Slew Rate Control) задает режимы крутых или пологих фронтов. Рекомендуется везде, где допустимо, устанавливать режим пологих фронтов, создающий гораздо меньшие помехи. В критичных для быстродействия цепях с целью повышения производительности системы используются режимы крутых фронтов (т. е. быстрых переключений).