Кодирующие и декодирующие устройства

Шифраторы

Шифратор (кодер) — это функциональный узел, предназначенный для преобразования поступающих на его входы управляющих сигналов (команд) в n-разрядный двоичный код. В частности, такими сигналами или командами могут быть десятичные числа, например, номер команды, который с помощью шифратора преобразуется в двоичный код.

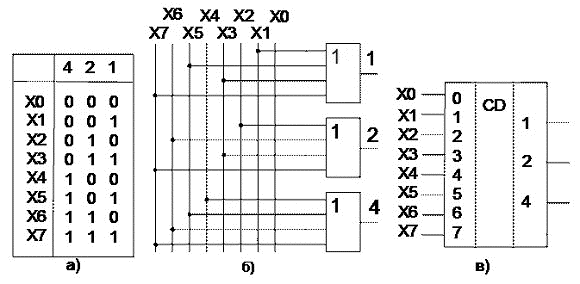

В качестве примера разработаем схему 3-разрядного шифратора. Вначале следует построить таблицу кодов (таблицу истинности), в которой код номера сигнала представим, например, двоичным кодом (рисунок 5,а). Схема, реализованная на элементах ИЛИ, приведена на рисунке 5,б.

Рисунок 5 Таблица кодов 3-разрядного шифратора а), его функциональная схема б) и УГО в).

В общем случае, при использовании двоичного кода, можно закодировать 2n входных сигналов. В рассмотренной выше схеме выходной код «000» будет присутствовать на выходе при подаче сигнала на вход X0 и в случае, если входной сигнал вообще не подаётся ни на один из входов. Для однозначной идентификации сигнала X0 в интегральных схемах формируется ещё один выходной сигнал — признак подачи входного сигнала, который используется и для других целей.

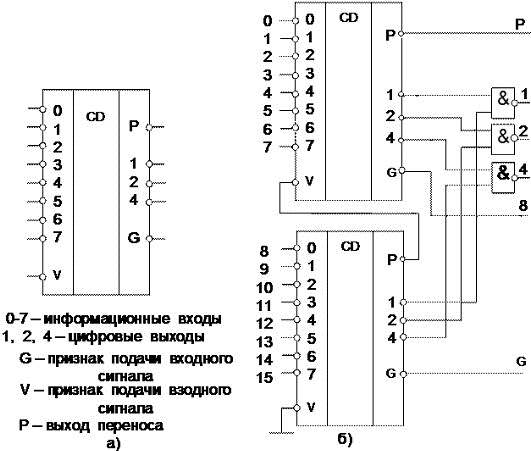

На рисунке 6 приведено УГО схемы 3-х разрядного приоритетного шифратора на 8 входов.

Рисунок 6. а) 3-разрядный приоритетный шифратор К555ИВ1 и

б) соединение двух МС

При подаче сигнала на любой из входов, устанавливается G=1, P=0, а на цифровых выходах — двоичный код номера входа, на который подан входной сигнал. Если сигнал подан одновременно на два или несколько входов, то на выходе установится код входа с большим номером. Отсюда название шифратора «приоритетный».

Если сигнал (лог.«0») подан на один из входов 0…7, то на выходах DD3 появятся младшие разряды прямого кода, на выходе G DD1 — лог. «0», определяющий разряд с весовым коэффициентом 8 выходного кода, на выходе P — лог. «1».

| Изм. |

| Лист |

| № докум. |

| Подпись |

| Дата |

| Лист |

| 68 |

| КР 15.02.07 09 00 00 ПЗ |

Таким образом, с выходов 1, 2, 4, 8 можно снять прямой код, соответствующий номеру входа, на который подан входной сигнал.

Дешифраторы (декодеры)

| Изм. |

| Лист |

| № докум. |

| Подпись |

| Дата |

| Лист |

| 69 |

| КР 15.02.07 09 00 00 ПЗ |

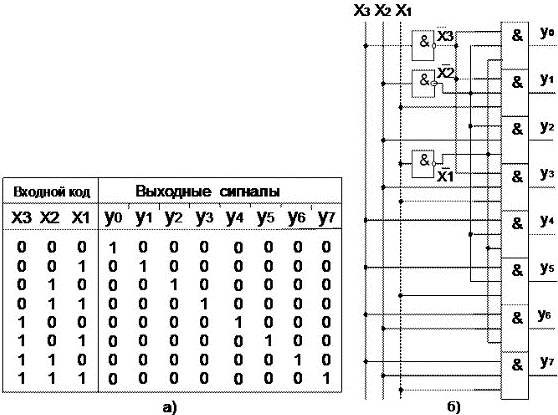

Рисунок 7 Дешифратор: а) – таблица истинности; б) – функциональная схема

Дешифраторы широко используются в устройствах управления, где они формируют управляющий сигнал в соответствии с входным кодом, который воздействует на какое-либо исполнительное устройство.

Интегральные микросхемы дешифраторов изготавливаются с дополнительными входами, например, с входом разрешения (стробирования). Стробирование позволяет исключить появление на входах дешифратора ложных сигналов, запрещая его работу в интервале времени переходного процесса при изменении цифрового кода на входе.

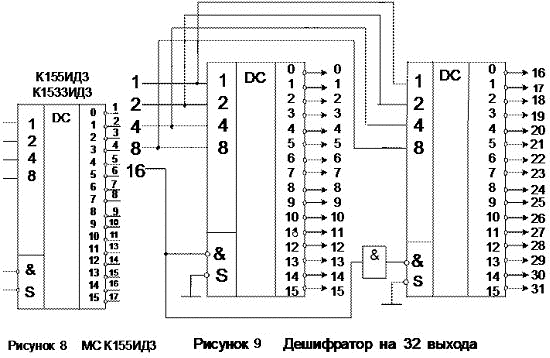

Микросхема ИД3 (рисунок 8) имеет четыре адресных входа с весовыми коэффициентами двоичного кода 1, 2, 4, 8, два инверсных входа стробирования S, объединённых по И, и 16 инверсных выходов 0–15. Если на обоих входах стробирования «лог. 0», то на том из выходов, номер которого соответствует десятичному эквиваленту входного кода, будет «лог. 0». Если хотя бы на одном из входов стробирования S «лог. 1», то независимо от состояния входов на всех выходах микросхемы формируется «лог. 1».

Наличие двух входов стробирования существенно расширяет возможности использования микросхем. Из двух микросхем ИД3, дополненных одним инвертором,

| Изм. |

| Лист |

| № докум. |

| Подпись |

| Дата |

| Лист |

| 70 |

| КР 15.02.07 09 00 00 ПЗ |

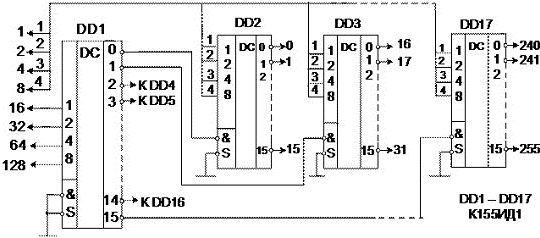

Рисунок 10 Дешифратор на 256 выходов