Цифровые интегральные микросхемы

Цифровой интегральной микросхемой (ЦИМС) называют конструктивно завершенное изделие, представляющее собой кремниевый кристалл на котором сформированы логические элементы.

Обычно ЦИМС заключена в герметичный корпус, защищающий кристалл от действия окружающей среды и рассеивающий выделяемое кристаллом тепло, на корпус закреплены выводы микросхемы. Иногда выпускаются бескорпусные ЦИМС, например, монтируемые сразу в плату.

Типы корпусов:

Типы корпусов:

Рис. 11

Чаще других используют плоские (планарные) корпуса и корпуса с двухрядным расположением выводов (DIP). DIP – изображён вышк первым.

Корпус может быть металлостеклянным, металлокерамическим, стеклокерамическим, но дешевле и ненадёжней всех – пластмассовый корпус.

Количество выводов корпуса от 6 до нескольких сотен, схему соединения выводов с элементами ЦИМС называют цоколёвкой.

Микросхема может иметь разный уровень интеграции. Малый уровень интеграции имеют микросхемы, в которых реализован набор несвязанных логических элементов. В микросхемах среднего уровня интеграции логические элементы соединены друг-с-другом образуя какую-то типовую схему цифровой электроники (счетчик, дешифратор, сумматор). В больших интегральных схемах (БИС) реализована масса соединенных друг-с-другом типовых схем. К классу БИС относятся: микропроцессоры, однокристальные микро ЭВМ, микросхемы памяти.

· малая интегральная схема (МИС) — до 100 элементов в кристалле,

· средняя интегральная схема (СИС) — до 1000 элементов в кристалле,

· большая интегральная схема (БИС) — до 10000 элементов в кристалле,

· сверхбольшая интегральная схема (СБИС) — более 10 тысяч элементов в кристалле.

По технологии изготовления отличают:

· полупроводниковая ИС – выполнена на одном полупроводниковом кристалле.

· плёночная ИС – выполнена на тонких либо толстых плёнках.

· гибридная ИС – содержит, кроме полупроводникового кристалла, бескорпусные элементы в одном корпусе с кристаллом.

· смешанная ИС – содержит, кроме полупроводникового кристалла, плёночные элементы, размещённые на поверхности кристалла.

А также:

Микросхемы на полевых транзисторах — самые экономичные (по потреблению тока):

· МОП-логика (металл-оксид-полупроводник логика) — микросхемы формируются из полевых транзисторов n-МОП или p-МОП типа.

· КМОП-логика (комплементарная МОП-логика) — каждый логический элемент микросхемы состоит из пары взаимодополняющих (комплементарных) полевых транзисторов (n-МОП и p-МОП). Очень распространённая и экономичная с точки зрения потребляемого тока технология, уязвимо к статическому электричеству.

Микросхемы на биполярных транзисторах:

· РТЛ — резисторно-транзисторная логика (устаревшая, заменена на ТТЛ).

· ДТЛ — диодно-транзисторная логика (устаревшая, заменена на ТТЛ).

· ТТЛ — транзисторно-транзисторная логика — микросхемы сделаны из биполярных транзисторов с многоэмиттерными транзисторами на входе. Распространённая, быстрая, энергоёмкая.

· ТТЛШ — транзисторно-транзисторная логика с диодами Шоттки — усовершенствованная ТТЛ, в которой используются биполярные транзисторы с эффектом Шоттки.

· ЭСЛ — эмиттерно-связанная логика — на биполярных транзисторах, режим работы которых подобран так, чтобы они не входили в режим насыщения, — что существенно повышает быстродействие. Самая быстрая, самая энергоёмкая, редкая.

· ИИЛ — интегрально-инжекционная логика.

Подробнее об характеристиках и устройстве различных видов логики см. ниже.

Также ЦИМС различают по назначению (какая именно схема реализована).

Микросхемы выпускаются сериями, т. е. группами микросхем, сходных по техническому исполнению. В пределах одной серии обычно МС имеют одинаковые: напряжения питания, входные и выходные сопротивления, уровни сигналов.

Условные обозначения ИС, выпускаемых отечественной промышленностью, устанавливаются ОСТ 11073.915-80, в соответствии с которым обозначения ИС состоят из четырех основных элементов.

1. Первый элемент - цифра, обозначающая группу по технологическому признаку, к первой группе относятся полупроводниковые ИС (цифры 1,5,6,7), ко второй - гибридные ИС (цифры 2,4,8), к третьей - прочие (цифра 3).

2. Второй элемент обозначает порядковый номер серии.

3. Третий элемент состоит из двух букв и определяет функциональное назначение ИС. Первая из букв определяет подгруппу, а вторая - вид ИС. Соответствующие данные по функциональному назначению ИС приведены в таблице 1.

4. Четвертый элемент - порядковый номер разработки ИС данного функционального типа.

Уровни проектирования ЦИМС:

1. Логический

2. Схемотехнический

3. Электрический – принципиальная схема на транзисторах, конденсаторах и тп.

4. Физический – методы реализации элементов предыдущего уровня на кристалле.

5. Топологический – создание фотошаблона для производства.

6. Программный – программирование для ПЛИС, микроконтроллеров и микропроцессоров.

Существуют САПР (системы автоматического проектирования), облегчающие жизнь разработчикам микросхем (напр. САПРы фирм Xilinx, Altera и тп.).

По функциональному назначению ЦИМС дел. на подгруппы: логические элементы, триггеры (D, T, JK, RS), регистры, генераторы цифровых импульсных сигналов, элементы дискретных и арифм. ус-в. Каждая группа делится на ЛЭ: И, ИЛИ, ИЛИ-НЕ, И-НЕ.

Статические параметры определяются с помощью статических характеристик, которые снимаются при медленных изменениях токов и напряжений. Это обстоятельство позволяет пренебрегать переходными процессами в элементах схемы. К статическим характеристикам относятся: передаточная Uвых= f(Uвх) при Iвых=0, обратной связи Uвх= f(Uвых) при Iвх=0, входная Iвх= f(Uвх) при Iвых=0 и выходная Iвых= f(Uвх) при Iвх=0 .

К динамическим параметрам ЦИМС относятся: время задержки сигнала при включении и время задержки сигнала при выключении, среднее время задержки, длительность фронтов нарастания и спада импульса.

| Параметры ИМС | ТТЛ | ТТЛШ | КМОП | ЭСЛ |

| Напряжение питания, В | 3-15 | - 5,2 | ||

| Уровень логического 0, В | 0,4 | 0,5 | 0,01 | -1,6 |

| Уровень логической 1, В | 2,4 | 2,7 | 2,99-14,99 | -0,9 |

| Время задержки Тз, нс | ||||

| Коэффициент разветвления по выходу Кр | 5-7 | 10-12 | 2-5 | |

| Статическая помехоустойчивость, В | 0,4-1,1 | 0,4-1,1 | 2-3 | 0,1-0,3 |

| Статическая потребляемая мощность Рп, мВт | 2-40 | 2-40 | 0,1-0,001 | 20-80 |

| Серии ИМС | К155, К555, КР1533 | К531, КР1531 | К561, КР1561, К1564 КР1554 | К500, К1500,К193 |

Рис. 12

1. Быстродействие определяется средней задержкой сигнала Тз, равной среднему арифметическому задержек включения и выключения одного инвертора. При определении Тз в качестве границ временных интервалов обычно берут точки на фронтах, соответствующие уровням 0,1 и 0,9 этого перепада. По средней задержке логические ИМС делятся на следующие группы:

· сверхбыстродействующие (Тз < 5 нс),

· быстродействующие (5 < Tз < 10 нс),

· среднего быстродействия (10 < Tз < 100 нс),

· малого быстродействия (Tз > 100 нс).

2. Потребляемая мощность зависит от того, какие сигналы поданы на входы этой ИМС. Поэтому данное свойство принято оценивать средней мощностью (Рп), потребляемой типовым логическим элементом во включенном и выключенном состояниях. Как правило, чем выше быстродействие ЦИМС, тем больше средняя потребляемая ими мощность. В процессе переключения логического элемента средняя мощность выше статической мощности, вследствие всплесков тока в переходных режимах. Поэтому в динамическом режиме потребляемая мощность зависит от частоты F переключения:

Pд = (U1 - U0)2C0F, где (U1 — U0) — перепад логических уровней; C0 — выходная емкость, включая емкость монтажа (C0 = 30—50 пФ). Эффект увеличения потребляемой мощности в динамическом режиме особенно заметен для КМОПТЛ, которые в статическом режиме потребляют очень мало. В связи с этим для КМОПТЛ указывают не статическую, а динамическую потребляемую мощность на определенной частоте переключения.

3. Помехоустойчивость.

Статическая помехоустойчивость — это наименьшее постоянное напряжение, которое, будучи добавлено к полезному входному сигналу, вызовет ошибку по всей последующей цепи логических схем. Статическая помеха наблюдается в тех случаях, когда относительно велико сопротивление проводников, подводящих к ЦИМС напряжение питания. Падения напряжения на "земляной" шине, разные для разных ЦИМС, будут суммироваться со входными сигналами и могут приводить к сбоям. Для исключения подобных ситуаций необходимо по возможности увеличивать сечение проводников, подводящих питание к ЦИМС.

Что касается динамической или импульсной помехоустойчивости, то для того чтобы возник сбой, импульсная помеха, как правило, должна быть больше, чем статическая. Поэтому при одинаковой статической помехоустойчивости схемы с большим быстродействием сильнее подвержены действию импульсных помех.

4. Нагрузочная способность характеризуется параметром Кр( коэффициент разветвления по выходу), Кр определяется числом входов схем той же самой серии, которые могут быть присоединены к выходу данной схемы без нарушения ее работоспособности. Так как входное сопротивление КМОПТЛ в статическом режиме велико, то последующие элементы практически не нагружают предыдущие. Это дает возможность иметь очень большой коэффициент разветвления по выходу. Однако в динамическом режиме входное сопротивление КМОПТЛ падает из-за наличия входных емкостей. Ток, потребляемый от данной микросхемы, увеличивается.

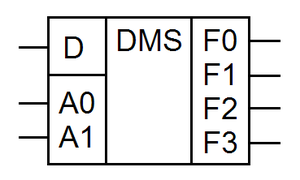

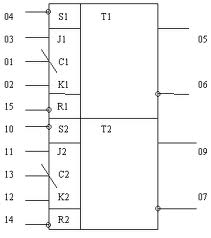

Пример условного графического обозначения ЦИМС.

На рис. 13 изображён демультиплексор 1 к 4.

DMS – условное обозначение демультиплексора.

Правый столбец – выходы, левый – входы и управляющие воздействия.

Рис. 13

Такой вид обозначения характерен для ЦИМС, меняется наименование схемы, число и вид входов и выходов. Обозначения других ИС см. ниже в разделах, посвящённых соответствующим устройствам.

Технологии изготовления логических элементов.

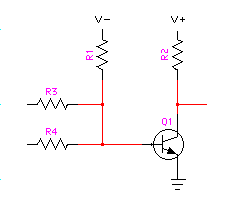

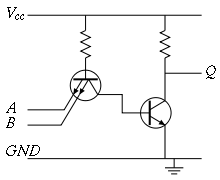

РТЛ – резисторно-транзисторная логика.

Рис. 14

Принцип работы (по рис. 14).

Коллектор транзистора через резистор соединён с питанием, эмиттер – с землёй, на базу через резисторы подаются входные сигналы. Если на входах 0 В – транзистор закрыт, на выход идёт напряжении питания, если хотя бы на одном входе уровень напряжения соответствует логической единице – транзистор открывается и питание «сливается» на землю. Таким образом, на рис. 14 изображён базисный элемент ИЛИ-НЕ в позитивной логике, он же – И-Не в негативной (уровни 0 и 1 инвертированны).

РЕТЛ – резисторно-ёмкостно-транзисторная логика.

Попытка усовершенствования РТЛ путём добавления ёмкостей на входы (фильтруют постоянный ток, пропускает только импульсы).

Достоинства РТЛ и РЕТЛ:

· Конструктивная простота;

· Низкая стоимость.

Недостатки:

· Высокая рассеиваемая мощность (на включенном транзисторе, резисторах);

· Нечёткий уровень сигналов (уровень единицы от ~0,9В до напряжения питания);

· Крайне низкое быстродействие;

· Низкая помехоустойчивость;

· Cложность разработки;

· Низкая нагрузочная способность выходов (обычно не более трёх входов других элементов).

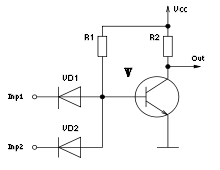

ДТЛ – диодно-транзисторная логика.

Рис. 15

При наличии 0 хотя бы на одном входе, ток течёт от питания через R1 во входную цепь – транзистор закрыт, на выходе 1. Если оба входа по единице, ток через R1 идёт на базу транзистора, он открывается, «сливает» на землю питание, на выходе – 0. Таким образом, рис. 15 – это схема двухвходового И-НЕ.

Преимущества перед РТЛ – можно создать больше входов (т. к. на входах диоды, а не резисторы). Недостатки – по прежнему малое быстродействие, т. к. открытый транзистор находится в режиме насыщения.

ТТЛ – транзисторно-транзисторная логика.

Логика работы как в ДТЛ, только вместо диодов – многоэмиттерный транзистор. На рис. 16 элемент 2И-НЕ.

Рис. 16

ТТЛШ – ТТЛ с диодами Шотки, отличается от ТТЛ наличием диодов Шоттки в цепях база — коллектор, для исключения насыщение транзистора, а также наличием диодов Шоттки на входах для подавления импульсных помех.

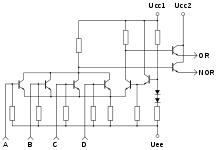

ЭСЛ – эмиттерно-связная логика

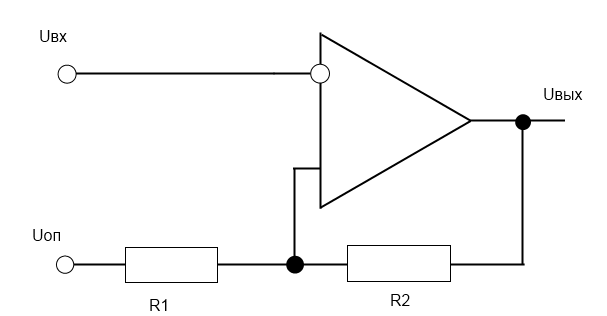

Основная идея ИСЛ – ключ на двух транзисторах (рис. 17).

Рис. 17

На базу одного подаётся опорное постоянное напряжение (Uоп), если при этом напряжение на второй базе (Хо) будет выше или ниже Uоп, то это приведёт к перераспределению тока Iэ между транзисторами (у кого напряжение на базе больше, через того больше тока течёт). Режим насыщения исключён, что сказывается положительно на быстродействии, т. к. Rk1и Rk2 малы, то перепад напряжений между уровнями 0 и 1 тоже небольшой, значит время перезарядки выходной ёмкости транзисторов тоже уменьшается. Выходное напряжения снимается с выходов Y0 и Y1, оно, очевидно, больше Uоп, так что, между Y0 и Y1 и выходом элемента нажно поставить эмиттерный повторитель для согласования. На рис. 18 изображён элемент 4ИЛИ/ИЛИ-НЕ.

Особенности ЭСЛ: высокое быстродействие, высокое энергопотребление, низкая помехоустойчивость, низкая степень интеграции (из-за высокой потребляемой мощности элементов), высокая цена.

Рис. 18

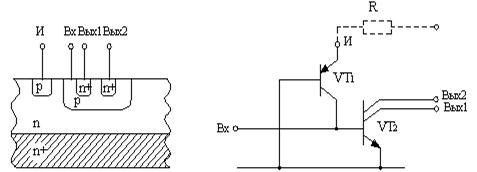

ИИЛ – интегрально-инжекционная логика (она же И2Л).

Рис. 19

Основа ИИЛ – инвертор, представленный на рис. 19, VT1 – npn транзистор, VT2 – pnp транзистор. База VT1 является эмиттером VT2, коллектор VT1 является базой VT2 (см. рис. 19, левую часть). VT1 – называется инжектором (добавляет ток в базу VT2). По сути VT1 – выполняет роль нагрузочного сопротивления, а VT2 – ключа. Если на вход подать 1, VT2 откроется, ток с VT1 стечёт на корпус, если 0 – VT2 закрыт, ток с VT1 насыщает VT2, на его коллекторах будет ток. На рис. 20 показана реализация базиса 2ИЛИ-НЕ на И2Л.

Рис. 20

Схема работы аналогична ключу на рис. 17, только вместа одного входного транзистора VT1 поставлено 4.

Особенности И2Л: высокая экономичность, высокое быстродействие, высокая степень интегрированности, помехоустойчивость, частота работы до 50 МГц (мало).

n-МОП, p-МОП – технология, основанная на применении соотвтствующего типа МОП транзисторов.

Рис. 21

На рис. 21 представлены соответственно элементы НЕ, ИЛИ-НЕ, И-НЕ на основе n-МОП.

В данных схемах нагрузочный транзистор на питании имеет встроенный канал, т. о. всегда проводит ток, думаю, что вам теперь не составит труда понять как работают элементы, изображённые на риунке.

n-МОП и p-МОП технологии не различаются по принципу работы, однако, первая быстрее (электроны подвижней дырок + ряд особенностей технологического процесса) и сложнее в изготовлении.

Особенности МОП: для современных МОП элементов характерны низкая цена, малое энергопотребление и большая степень интеграции.

КМОП (CMOS) - комплементарная логика на транзисторах металл-оксид-полупроводник.

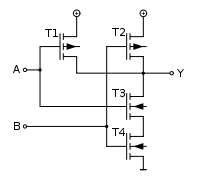

Рис. 22

КМОП основана на применении МОП транзисторов с разнам типом канала в одной схеме.

На рис. 22 представлен элемент 2И-НЕ. Если входы А и В имеют высокий уровень – Т3 и Т4 открыты, Т1 и Т2 закрыты, выход Y соединён с землёй. Если на А подать низкий уровень Т1 - откроется, Т3 – закроется, Y соединяется с питанием, схема симметрична, поэтому при подаче на В высокого уровня Y также соединяется с питанием.

Особенности КМОП – нет резисторов, значит, нет рассеиваемой мощности на резисторах, и в статическом состоянии по схеме текут только токи утечки транзисторов (очень малы). Так что энергия тратится только на процесс переключения (заряд затворов транзисторов), и энергопотребление тем ниже, чем ниже частота переключений схемы (характерно и для МОП). Наличие транзисторов обоих типов канала приводит к ещё большему, чум у МОП быстродействию и меньшему энергопотреблению. Снижена степень интеграции, более сложных процесс изготовления.

И так, мы познакомились с основными элементами цифровой схемотехники, объединяя несколько таких элементов можно получить функциональные ухлы и блоки (напр. сумматор).

Глава 3. Последовательные цифровые устройства — цифровые автоматы.

Мы упоминали выше, что автомат запоминает своё предшествующее состояние, и оно также рассматривается как входной параметр.

3.1. Цифровые триггерные схемы

Триггер – цифровой автомат, меняющий устойчивое состояние на выходе на противоположное устойчивое состояние (0 на 1 / 1 на 0) под воздействием входных сигналов.

Как правило, триггер имеет 2 выхода – прямой и инверсный, и два стабильных состояния на этих выходах – 0 и 1, хотя, возможен и n-ичный триггер. Триггер сохраняет уровни сигнала на выходах до следующего, изменяющего сигнал, входного воздействия, таким образом, представляет собой энергозависимое запоминающее устройство. Схема триггера содержит одну или несколько обратных связей.

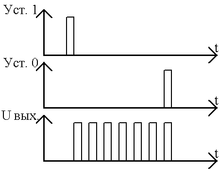

Триггеры бывают динамическими и статическими. Если на выходе динамического триггера выставлена 1 – она представляет из себя последовательность импульсов определённой частоты (см. рис. 23), для статического триггера единица – непрерывный уровень сигнала.

Рис. 23. Временная диаграмма динамического триггера.

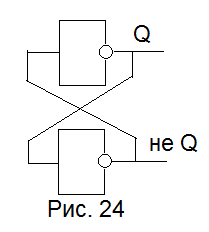

Основу для триггера – запоминающий элемент, проще всего представить в виде двух связанных инверторов, изображённый на рис. 24. По рисунку видно, что, логические уровни выходов сохраняются при наличии питания.

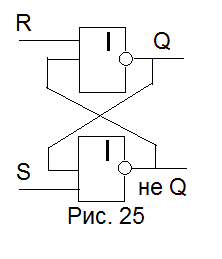

Для того, чтобы подобная схема стала триггером, нам надо научиться выставлять нужные нам уровни логических выходов, т. е., добавить в схему управляющие входы (например, как на рис. 25).

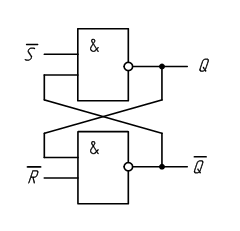

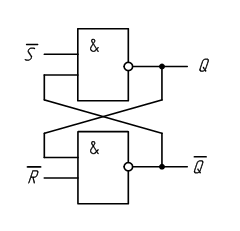

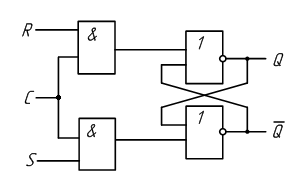

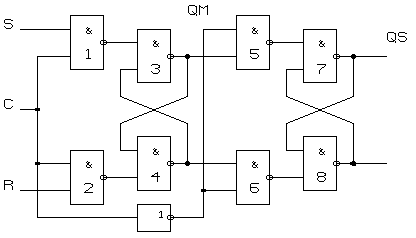

Статический асинхронный RS – триггер.

На рис. 25 изображён RS-триггер на базе элементов ИЛИ-НЕ. R-вход – устанавливает 0 на Q-выходе (от англ. Reset –сброс), S-вход – устанавливает 1 на Q – выходе (от англ. Set – установка).

Рассмотрим подробнее схему работы RS-триггера.

Напомним, что логический элемент ИЛИ-НЕ выдаёт 0 на выходе при наличии 1 хотя бы на одном из входов (см. таблицы истинности логических функций).

Пусть R=1, S=0 – тогда Q=0,  =1 (т. к. Q=0, S=0).

=1 (т. к. Q=0, S=0).

Пусть R=0, S=1 – тогда Q=1,  =0.

=0.

Пусть R=0, S=0 – тогда Q=Qпредидущее,  =

=  . Это режим хранения, на выходе триггера сохраняются уровни, установленные до перехода в этот режим.

. Это режим хранения, на выходе триггера сохраняются уровни, установленные до перехода в этот режим.

Пусть R=1, S=1 – тогда Q=0,  =0. Это неустойчивый режим, сразу после установки прямого и инверсного выходов в одинаковое состояние (в данном случае 0) ячейка памяти триггера сбросит выходы в одно из устойчивых состояний за счёт наличия обратной связи, причём выбор устойчивого состояния произволен (зависит от временных характеристик элементов схемы). Этот режим называется запрещённым состоянием триггера, некоторые современные RS-триггеры умеют сохранять 00 на выходах за счёт ряда схемотехнических решений. На рис. 26 приведена таблица состояний RS-триггера. Q(t) – состояния выхода до прихода соответствующих входных сигналов, Q(t+1) – состояние выхода после входного воздействия.

=0. Это неустойчивый режим, сразу после установки прямого и инверсного выходов в одинаковое состояние (в данном случае 0) ячейка памяти триггера сбросит выходы в одно из устойчивых состояний за счёт наличия обратной связи, причём выбор устойчивого состояния произволен (зависит от временных характеристик элементов схемы). Этот режим называется запрещённым состоянием триггера, некоторые современные RS-триггеры умеют сохранять 00 на выходах за счёт ряда схемотехнических решений. На рис. 26 приведена таблица состояний RS-триггера. Q(t) – состояния выхода до прихода соответствующих входных сигналов, Q(t+1) – состояние выхода после входного воздействия.

| R | S | Q(t) | Q(t+1) | Режим |

| Режим хранения информации R=S=0 | ||||

| Режим установки единицы S=1 | ||||

| Режим установки нуля R=1 | ||||

| - | R=S=1 запрещённое состояние | |||

| - |

Рис. 26

Рис. 27

На рис. 27, 28 представлены принципиальная схема и таблица состояний RS-триггера на базе И-НЕ элементов. Обратите внимание, входы триггера инвертированы и поменяны местами!

|  | Q(t) | Q(t+1) | Режим |

| - | R=S=0 запрещённое состояние | |||

| - | ||||

| Режим установки нуля R=1 | ||||

| Режим установки единицы S=1 | ||||

| R=S=1 режим хранения информации | ||||

Рис. 28

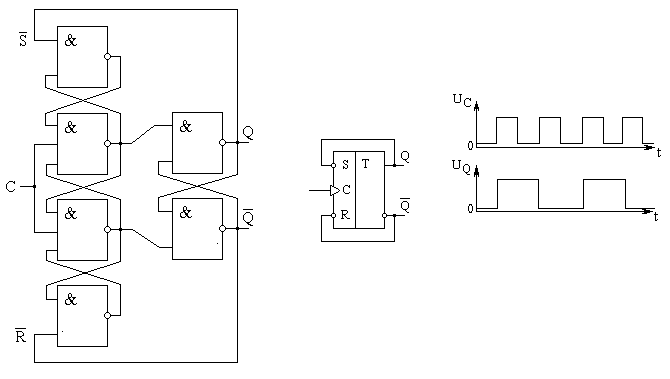

Статический синхронный RS – триггер.

Рис. 29

В реальной схеме смена входных логических уровней не происходит мгновенно, да к тому же возможны помехи, это вызывает ненужные перепады на информационных выходах триггера. Дополнительный вход С, добавленный к RS-триггеру (см. рис. 29), позволяет уменьшить вероятность несанкционированных перепадов входного сигнала, т. к. сигнал теперь считывается только при С=1 (С выставляется в 1 чуть позже, чем приходят R и S, таким образом, R и S получают некоторое время, для того, чтобы перейти в новое состояние, когда С=0 на входы триггера может поступать что угодно, это никак не отражается на состоянии выходов). Синхронным называется триггер, запоминающий входные воздействия только при установленном в 1 входе синхронизации. На рис. 30 даны УГО асинхронного и синхронного RS-триггеров.

Рис. 30

Синхронный RS-триггер с динамическим управлением.

Рис. 31

И так, синхронный RS-триггер решает вопрос неустойчивости выходного сигнала во время спада и нарастания входного сигнала. Но, по-прежнему, существует проблема помехи. Мы выставляем С=0 и далее Q определяется комбинацией входных сигналов, но, если на вход придёт помеха, а С при этом равняется 1 – помеха повлияет на выходной сигнал, что явно не способствует устойчивости схемы с подобным устройством внутри. Чтобы минимизировать вероятность описанного выше негативного влияния помехи были придуманы триггеры с динамическим управлением. На рис. 31 изображена схема (слева) и УГО (справа) синхронного RS –триггера с динамическим управлением. Направление стрелки на УГО показывает, что триггер управляется фронтом импульса (обратное направление – спадом), вместо стрелки бывают изображены / и \ для фронта и спада соответственно.

Принцип действия:

Посмотрев на схему, мы видим, что её правая часть есть не что иное, как простой RS-триггер. Левая часть схемы – управляющая. Будем обозначать логические блоки парами слева на право. При С=0 на выходах обоих элементов второй пары формируется 1, что соответствует режиму хранения информации. При установке С в 1 один из логических элементов второй пары получит на входе три единицы, на выходе у него, соответственно, будет 0 (учитываем наличие запрещённого состояния, см. выше). На втором элементе второго блока будет 1, мы имеем либо режим установки 1, либо режим установки 0 для третьего блока, такая ситуация сохраняется, пока С не станет равным 0.

Таким образом, Синхронный RS-триггер с динамическим управлением записывает информацию только по фронту (в рассмотренном случае), или спаду тактового импульса.

Двухтактный синхронный RS-триггер (он же – RS-триггер со структурой мастер-помощник).

Другим способом увеличения помехоустойчивости RS-триггера является его двухступенчатое исполнение. На рис. 32 представлена принципиальная

Рис. 32

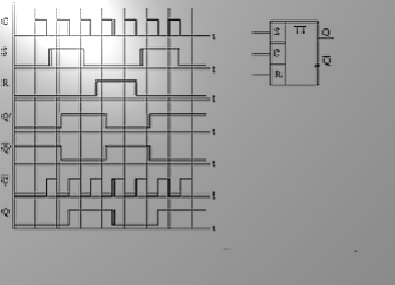

схема двухтактного RS-триггера, на рис. 33 – его временная диаграмма и УГО. (Временная диаграмма – графический способ представления таблицы состояний в виде графиков зависимостей уровня сигнала от времени).

Видно, что двухтактный триггер состоит из двух однотактных и инвертора, соединяющего их С-входы. Таким образом, подавая 1 на С-вход, мы открываем первый триггер на запись информации, одновременно заблокировав второй (инвертор перевернёт С-сигнал, и на синхронизирующий вход второго триггера поступит 0). Когда же синхронизирующий сигнал станет равным 0 – первый триггер (принимающий, хозяин) закроется для записи информации, а второй (запоминающий, помощник) – откроется, и то, что было записано в первый триггер, попадёт во второй.

Подобная система решает проблема помех решается исходя из предположения о том, что за время, предоставленное первому триггеру, все помехи пройдут, и в нём окажется адекватная информация, которая и будет переписана во второй триггер. Важной особенностью двухтактного триггера является задержка информационного сигнала на время, равное длительности тактового сигнала. Надёжность подобного решения меньше, чем у динамических триггеров, но структура мастер-помощник нашла важное применение в цифровой технике, в частности, для построения Т-триггеров – основы для счётчиков.

Рис. 33

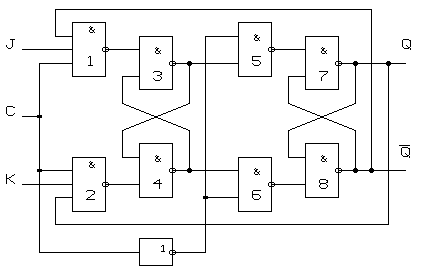

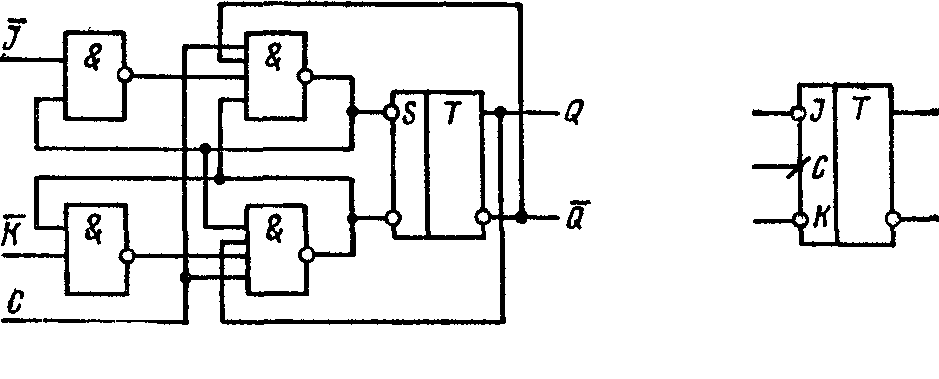

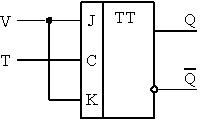

JK-триггер.

И так, мы рассмотрели некоторые возможные решения проблемы помехоустойчивости RS-триггера. Теперь поговорим о запрещённом состоянии.

На рис. 34 представлена схема JK-триггера (J – jump, прыжок, К – keep, хранить), видно, что от рассмотренного выше двухтактного RS-триггера он отличается наличием двух обратных связей с выходов помощника на входы мастера. Принцип работы довольно прост, рассмотрим только случай J=K=1 (т. к. остальные случаи аналогичны RS-триггеру, а эта комбинация в RS-триггере запрещена). На одном из выходов триггера-помощника имеется нулевой уровень (выходы же взаимно-инверсны, как ему там не иметься), он, за счёт обратной связи, заблокирует соответствующий входной элемент (т. е., подав на вход И-НЕ 0 на выходе мы получаем всегда единицу, независимо от остальных входов). Второй же вход установит выходы триггера помощника в инвертированное состояние (т. к. обратные связи перекрестные, то блокируется вход накрест, а я надеюсь, вы уже заметили, что единичный сигнал на входе рассматриваемых триггеров устанавливает в 1 соответствующий выход). Поскольку JK-триггер построен на основе двухтактного триггера, то он тоже имеет задержку. JK-триггер часто называют универсальным, т. к. на его основе несложно построить другие

типы триггеров. Рис. 35, 36 – таблица состояний и УГО, соответственно.

Рис. 34

| J | K | Q(t) | Q(t+1) | Режим |

| Режим хранения информации | ||||

| Режим установки нуля | ||||

| Режим установки единицы | ||||

| Инверсия выходов, счётный режим | ||||

Рис. 35

Рис. 36

Рис. 37. Динамический JK-триггер и его УГО.

Другие типы триггеров.

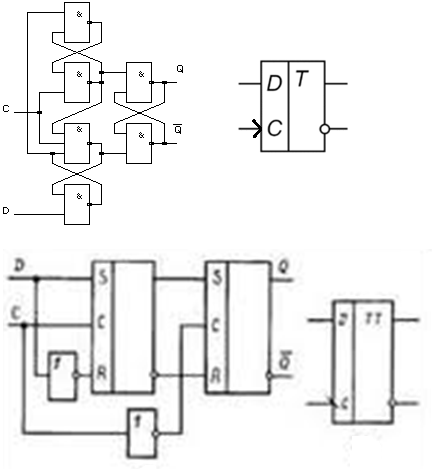

Синхронный D-триггер (от англ. delay – задержка) – триггер, выставляющий на выход значение входного информационного сигнала с задержкой по синхронизирующему импульсу (см. рис. 38,39).

| D | Qn | Qn+1 |

Рис. 38

Рис. 39

Если на D подать 0 и С при этом 1, то на Q будет выставлена 1, если подать 0 – выставится 0, вопрос в том, что ничего не изменится на выходах до прихода следующего синхроимпульса. Поскольку, по входу С обычно микросхемы синхронизируют между собой, постольку , иногда, в D-триггер добавляют ещё один вход V, дублирующий С, он нужен для дополнительного управления триггером. При наличии V-входа запись информации возможна только при V=C=1, при нулевом V значение триггера сохраняется независимо от синхроимпульсов. D-триггер – простейшая ячейка оперативной памяти.

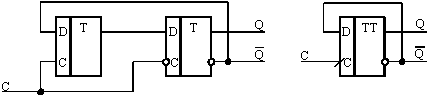

Для большей помехоустойчивости, D-триггер может быть построен на базе динамического или двухтактного триггеров (на рис. 40 сверху и снизу соответственно).

Рис. 40

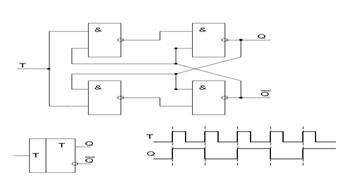

Т-триггер (от time – время) – триггер с единственным входом (это синхровход), меняет своё состояние по фронту каждого синхроимпульса. На рис. 41 представлены: схема, временная диаграмма и УГО Т-триггера. Т-триггер делит частоту входного импульса на 2.

Рис. 41

Рис. 42

На рис. 42 представлена схема Т-триггера на двух D-триггерах. По сути, это триггер мастер-помошник. Т-триггер также, как и D-триггер, может иметь необязательный разрешающий вход V, тогда он называется TV-триггером (рис. 44).

Рис. 43. Т-триггер с динамическим управлением.

Рис. 44

Рис. 45. Схемы различных триггеров на основе JK.

Рис. 46. Несколько триггеров на одной схеме.

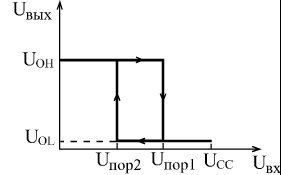

Триггер Шмитта – два компаратора, либо инвертор, с положительной обратной связью (рис. 47). По сути, не триггер, да и не цифровой элемент, т. к. вход у него аналоговый. На рис. 50 изображена передаточная характеристика триггера Шмитта (инвертирующего), при понижении входного напряжения до точки Uпор2, выход триггера устанавливается в 1, сохраняя свой уровень, пока входное напряжение не превысит Uпор1. Триггер Шмитта назван триггером, т. к. обладает свойством запоминать информацию, применяется для выравнивания сигнала.

Рис. 47

Рис. 48. Применение триггера Шмитта – подавление дребезга кнопок (выравнивание сигнала).

Рис. 48. Применение триггера Шмитта – подавление дребезга кнопок (выравнивание сигнала).

Рис. 49. Уго триггер Шмитта.

Рис. 49. Уго триггер Шмитта.

Рис. 50