Исследование синхронного триггера на логике И-НЕ

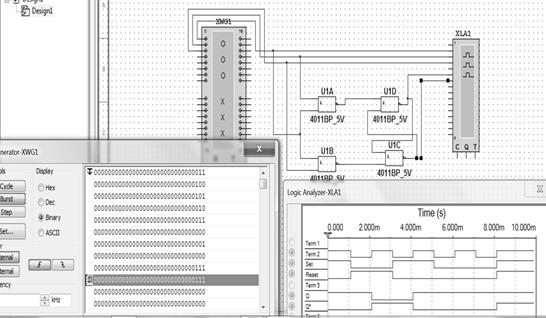

На рисунке 2.5.6. показана схема синхронного RS – триггера на логике

И-НЕ. Генератор запрограммирован так, чтобы можно было проверить все возможные состояния триггера по таблице состояний. На первом такте подается импульс синхронизации. На входе «S» логическая единица, на входе «R» логический ноль. Триггер устанавливается в состояние «1», Q = «1».

Во втором такте входы «S» и «R» изменяют свои значения на противоположные, но триггер находится в режиме хранения и не меняет своего состояния, так как вход С = «0».

В третьем такте при С= «1» происходит изменение состояния триггера, он устанавливается в «0», Q = «0».

В четвертом такте С = «0» – хранение.

В пятом такте установка в состояние «1», Q = «1».

В шестом такте - хранение, так как все входные сигналы равны «0».

В седьмом такте – хранение, так как хотя С= «1», «S» = «R» = 0.

В восьмом такте – хранение.

В девятом и десятом тактах –запретное состояние С= «S» = «R» = «1», при

этом Q =Q*=1.

При исследовании триггера используйте однократную развертку временной диаграммы в режиме «Burst».

Рис.2.5.6. Схема синхронного RS – триггера на логике И-НЕ

Отчет должен содержать заголовок работы, цель исследования, определение триггера и его назначение. Таблицы состояний триггеров с пояснениями, схемы исследуемых триггеров, временные диаграммы их исследования на всех возможных входных наборах входных сигналов. Выводы о соответствии результатов теоретически построенным таблицам состояния триггеров.

Вопросы для подготовки к отчету:

1. Какие функции выполняют триггеры в схемах вычислительной техники?

2. Чем отличаются триггеры, построенные на логике И-НЕ и на логике ИЛИ-НЕ.

3. Для чего применяются синхронные триггеры?

4. Как работает синхронный триггер на логике И-НЕ?

6. Лабораторная работа № 6

Исследование работы двухтактного RS-триггера.

Цель работы: Изучить основы построения двухтактного RS – триггера.

Задание: Изучить теоретическое введение, собрать схему двухтактного RS – триггера в в Muitisim, исследовать его работу, сделать заключение о соответствии экспериментальных результатов таблице состояния триггера.

Теоретическое введение

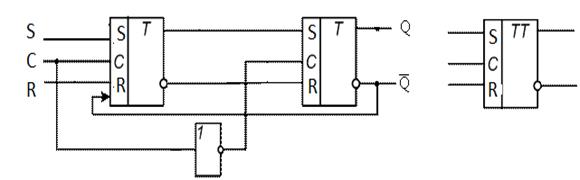

Одновременно принимать информацию в однотактный триггер по импульсу синхронизации и читать информацию из этого же триггера невозможно. Такую задачу решает двухтактный триггер. Двухтактный триггер состоит из двух однотактных.

Первый триггер принимает информацию по импульсу синхронизации, а из второго в это время можно читать информацию, записанную ранее. После окончания импульса синхронизации принятая информация переписывается во второй триггер. Импульс синхронизации на второй триггер подается через инвертор. Когда первый триггер принимает информацию, второй триггер находится в режиме хранения, именно потому из него можно читать записанную ранее информацию в том же такте (рис.2.6.1).

Рис.2.6.1. Синхронный двухтактный триггер

Второй триггер изменяет свои состояния только после окончания действия сигнала синхронизации С=1. Используемый принцип записи позволяет исключить потерю информации, когда один и тот же элемент памяти одновременно используется в качестве приёмника и источника информации.

Поэтому из двухтактных триггеров можно строить произвольные схемы, в том числе подавать сигналы с выхода триггера на его вход

Для асинхронной установки триггера в состояние «1» или «0» вводят дополнительные схемы, устанавливающие обе ступени двухтактного триггера в состояние «0» или «1» при подаче устанавливающих сигналов на входы. На рис. 2.6.2 показан двухтактный триггер, имеющий входы асинхронной установки и сброса и его обозначение на схемах.

Рис.2.6.2. Двухтактный синхронный RS-триггер с асинхронной установкой и сбросом

Таблица переходов двухтактного триггера приведена в таблице 2.6.1.

Таблица 2.6.1