Регистры памяти и сдвиговые регистры

Цель работы:Изучить принципы построения регистров и их назначение в вычислительной технике

Задание:Произвести исследование параллельного регистра хранения данных и последовательного сдвигового регистра.

Теоретическое введение

Регистром называется совокупность триггерных схем, объединенных общими цепями управления и применяемых для приема, преобразования хранения и передачи данных в двоичном коде. Количество триггеров в регистре соответствует числу разрядов двоичного кода. Занесение информации в регистр называется операцией записи. Извлечение информации из регистра – операцией считывания.

В регистрах могут выполняться микрооперации над словами, это:

· установка триггера в начальное состояние (запись нулевого кода, сброс);

· запись слова в регистр, данные хранятся в регистре, пока не появится команда на их смену;

· чтение слова из регистра;

· запись входной информации в параллельном коде;

· запись входной информации в последовательном коде;

· выполнение поразрядных логических операций над словами;

· сдвиг кода вправо или влево на требуемое число разрядов;

· преобразование параллельного кода в последовательный;

· преобразование последовательного кода в параллельный.

В зависимости от формы представления числа (параллельной или последовательной), используемой при вводе числа в регистр, различают два типа регистров: параллельные и последовательные. В параллельный регистр предназначенное для хранения число подается одновременно всеми разрядами (в параллельной форме). В последовательный регистр ввод числа производится в последовательной форме путем последовательной во времени подачи цифр отдельных разрядов (обычно начиная с цифры младшего разряда).

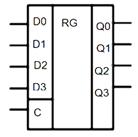

Параллельные регистры.В параллельных регистрах операции записи и считывания информации осуществляются во всех разрядах одновременно. На схемах регистр обозначается буквами RG, условное обозначение параллельного регистра показано на рис. 2.13.1

Рис. 2.13.1. Условное обозначение параллельного регистра

На рис. 2.13.2. показана схема параллельного регистра, который принимает информацию по команде записи «WR» – сигнал «С». Чтение осуществляется по команде «RD». При «RD» = 1 логические схемы «И» на выходе регистра разрешают передачу сигналов с выходов триггеров на шину данных.

Рис. 2.13.2. Схема параллельного регистра на D – триггерах

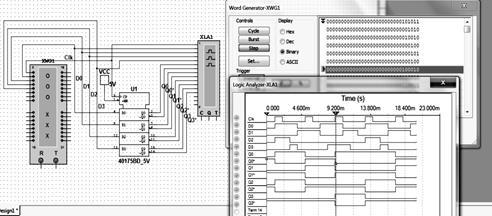

На рис. 2.13.3. показана схема параллельного регистра на микросхеме 40157BD_5V. Вход «MR» = «1» разрешает прием данных в регистр, поэтому на него подается логическая единица с источника «VCC».

Рис. 2.13.3. Схема параллельного регистра на D – триггерах

(микросхема 40157BD_5V)

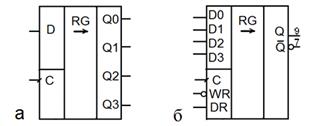

Сдвигающие последовательные регистры. В последовательных регистрах запись кода числа начинается с младшего разряда путем последовательного продвижения (сдвига) информации с помощью тактовых импульсов. Такие регистры строятся из синхронных триггерных схем, соединенных последовательно, так что выходной сигнал предыдущего триггера поступает на информационный вход последующего. Все триггеры управляются общим сигналом синхронизации. Для построения сдвигающего регистра необходимы, синхронные триггеры с динамическим управлением или двухтактные триггеры, так как в них выходные сигналы не меняются во время действия синхроимпульса. В регистрах сдвига могут применяться любые двухтактные триггеры: (R-S, D, J-K). Но все они работают в режиме D - триггера, который по сигналу синхронизации устанавливается в состояние, определяемое D - входом. Последовательный n-разрядный регистр принимает n-разрядное число за n-тактовых импульсов. Поступивший на вход последовательный код преобразуется в регистре в параллельный код: число может быть считано параллельным кодом с выходов триггеров. Число можно считать последовательно с одного выхода. Сдвиг информации на один разряд равнозначен умножению кода на 2, поэтому сдвиг можно применять для изменения порядка числа. Условное графическое изображение последовательно – параллельного регистра показано на рис. 2.13.4.

Рис. 2.13.4. Условное графическое изображение сдвигового

а) последовательно – параллельного регистра

б) параллельно – последовательного регистра

Вход WR – разрешает прием информации параллельным кодом. DR – последовательный вход.

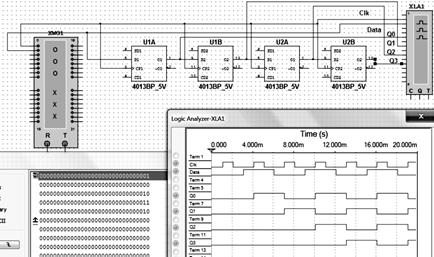

Сдвиговый регистр на D – триггерах динамического типа показан на рис. 2.13.5.

Рис. 2.13.5. Схема сдвигового регистра на D – триггерах