Fpga-программируемые пользователем вентильные матрицы

7.4.1. АРХИТЕКТУРА И БЛОКИ FPGA

Программируемые пользователем вентильные матрицы (FPGA или ППВМ) топологически сходны с канальными БМК. Их основой служит матрица регулярно расположенных по строкам и столбцам идентичных конфигурируемых логических блоков. Между строками и столбцами логических блоков проходят трассировочные каналы, содержащие ресурсы межсоединений. При программировании логические блоки настраиваются на требуемые операции преобразования данных, а трассировочные ресурсы - на обеспечение нужных взаимных соединений логических блоков. В результате во внутренней области FPGA реализуется функциональная схема проектируемого устройства. В периферийной области кристалла, по его краям, размещены блоки ввода/вывода, обеспечивающие интерфейс FPGA с другими микросхемами, причем в современных FPGA схемы ввода/ вывода способны выполнять требования множества стандартов на сигналы передачи данных, число которых может доходить до 20.

Свойства и возможности FPGA зависят прежде всего от ключевых архитектурных факторов — типа логических блоков и системы межсоединений.

Важной характеристикой логических блоков (ЛБ) является зернистость (granularity). Зернистость характеризует уровень разбиения схемы блока на коммутируемые при программировании части. Примерами наиболее мелкозернистых логических блоков могут служить цепочки транзисторов с р- и n-каналами, с помощью которых можно собирать логические схемы непосредственно из пар транзисторов по обычной методике реализации КМОП-логики. Мелкозернистость придает гибкость использованию схемных элементов кристалла, но усложняет систему межсоединений. Более крупнозернистые блоки используются в большинстве FPGA и имеют довольно разнообразный характер.

Типичными представителями логических блоков FPGA являются:

• логические модули на основе мультиплексоров;

• логические модули на основе программируемой памяти (блоки типа LUT- Look-Up Tables).

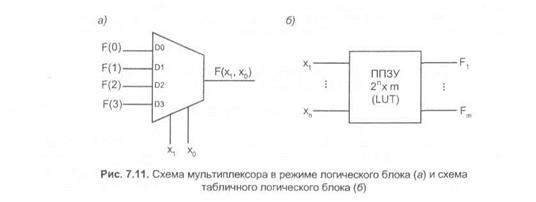

В некоторых FPGA применяют логические блоки, состоящие из нескольких малоразмерных Известно, что мультиплексоры могут работать в режиме универсальных логических модулей, если на их адресные входы подавать аргументы переключательной функции, а на информационные -настроечные сигналы. При настройке константами 0 и 1 мультиплексор размерности 2n - 1 воспроизводит функции п переменных, что иллюстрируется на рис. 7.11, а примером для функции двух переменных. Действительно, комбинация х1х0 = 00 определяет передачу на выход мультиплексора сигнала DO с нулевого информационного входа. Если на этом входе задано в качестве настроечного сигнала значение функции при нулевом аргументе F(0), то на выходе получим искомый результат. Комбинация х1х0 = 01 передает на выход сигнал D1, и если D1 = F(1), то получим необходимый результат и для этого набора аргументов и т. д. Таким образом можно получать с помощью мультиплексора любую функцию n аргументов.

В некоторых FPGA применяют логические блоки,состоящие из нескольких мультиплексоров (2-1,4-1), получая при этом программируемые логические блоки с широкими логическими возможностями.

Самые распространенные логические блоки FPGA - табличные (LUTs). Эти блоки называют часто табличными функциональными преобразователями. В них используются программируемые запоминающие устройства. При этом набор аргументов служит адресом, по которому записывается соответствующее значение функции, если память имеет одноразрядную организацию, или значения m функций, если разрядность хранимых слов равна т. Число аргументов воспроизводимых функций равно разрядности адреса памяти. Табличные функциональные преобразователи (рис. 7.11, б) воспроизводят любые функции данного числа аргументов.

Для систем межсоединений FPGA характерны сегментированные линии, составленные из отдельных отрезков, соединяемых друг с другом программируемыми элементами. Программируемые соединительные элементы могут быть размещены в так называемых переключательных блоках, конфигурируемых так, чтобы составить из сегментов необходимые цепи. Программируемые соединительные элементы (ключи) вносят в линии передач сигналов задержки, так как имеют паразитные параметры (сопротивление R и емкость С). Задержки, обусловленные постоянными времени ключей RC, доминируют над другими, так что число ключей в линии передачи сигнала практически определяет и задержку в линии связи.

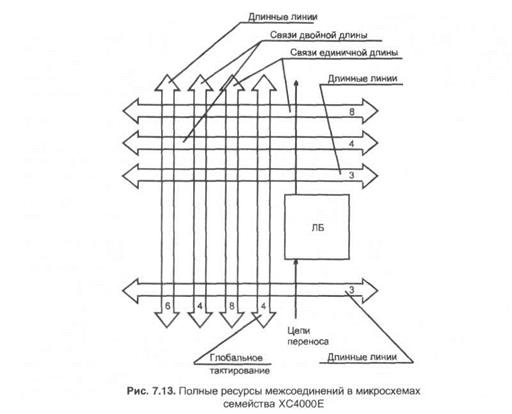

Выбор длин сегментов - непростая задача, поскольку короткие сегменты затрудняют передачи сигналов на большие расстояния (появится большое число ключей в линии), а длинные сегменты неудобны для реализации коротких передач. Обычно применение однотипных сегментов не может дать удовлетворительных результатов, и система межсоединений организуется как иерархическая. Так, например, в широко известных FPGA фирмы «Xilinx» ресурсы межсоединений содержат основные связи (General Purpose Interconnects) с сегментами единичной длины, основные связи с сегментами двойной длины, так называемые прямые связи для соединения логических блоков с ближайшими соседями (Direct Connects) и длинные линии (Long Lines), пересекающие кристалл по всей его длине и ширине для передач сигналов на большие расстояния и с малыми задержками.

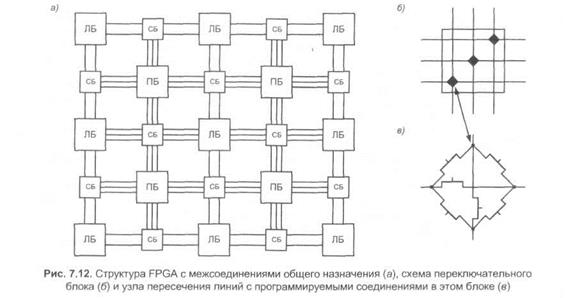

На рис. 7.12, а представлена структура FPGA с простейшей системой межсоединений, содержащей только основные связи с единичной длиной сегментов. Через ЛБ обозначены

конфигурируемые логические блоки (для краткости принято обозначение ЛБ, в котором конфигурируемость не обозначена, также обозначаются конфигурируемые логические блоки и в дальнейшем). В структуру входят также переключательные блоки ПБ и соединительные блоки СБ. Соединительные блоки обеспечивают связи ПБ с трактами передач сигналов, проходящими через переключательные блоки.

В сущности, это совокупность пересечений линий ввода/вывода логических блоков с линиями, проходящими через переключательные блоки, с элементами программируемых соединений в точках пересечений. Схема ПБ раскрыта на рис. 7.12, б. Сигналы, поступающие по какой-либо линии в ПБ, могут быть направлены далее по трем направлениям, что обеспечивается наличием в ПБ показанных зачерненными квадратами схем, представленных на рис. 7.12, в. Иными словами, сигналы могут передаваться по горизонтальным или вертикальным линиям и переходить с одних на другие.

Ресурсы межсоединений в FPGA в полном виде показаны на рис. 7.13 на примере микросхемы ХС4000Е фирмы «Xilinx» . Здесь наряду с основными связями единичной длины (восемь линий в каждом из направлений) имеются основные связи с линиями двойной длины (четыре линии в каждом из направлений), шесть вертикальных и шесть горизонтальных длинных линий и четыре линии глобального, т. е. общего для всей микросхемы тактирования.

В сегментированных линиях межсоединений задержки сигналов зависят от путей их распространения, так как пути неидентичны и в них может оказаться разное число ключей.

7.4.2. ПОПУЛЯРНЫЕ FPGA ФИРМЫ «XILINX»

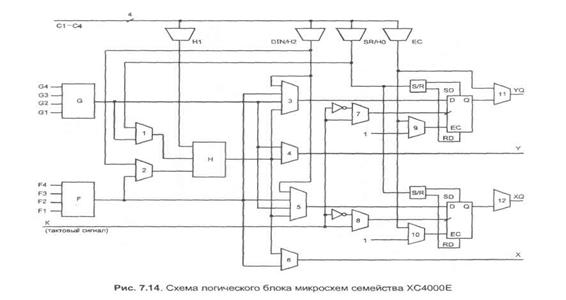

Логический блок семейства FPGA XC4000E фирмы «Xilinx» (рис. 7.14) иллюстрирует характерные особенности подобных блоков. Фирма «Xilinx» является ведущей в области разработки FPGA, ее продукция занимает 30-40% мирового рынка микросхем программируемой логики, ею был создан перспективный класс FPGA с триггерной памятью конфигурации.

Заметим предварительно, что на рис. 7.14 программируемость не отражена в обозначениях мультиплексоров, так как все они являются программируемыми.

Логические преобразования выполняются тремя табличными преобразователями: G, F и Н. Преобразователи G и F представляют собою программируемые запоминающие устройства с организацией 16 х 1 и могут воспроизводить любые функции четырех переменных. Через нижние входы мультиплексоров 1 и 2 выходы преобразователей G и F могут быть поданы на преобразователь Н (память с организацией 8 х 1) для образования «функции от функций» с целью получения функций, зависящих от более чем четырех аргументов. Преобразователь Н может также использоваться как третий независимый генератор функций со входами НО, Н1 и Н2, если через мультиплексоры 1 и 2 передаются сигналы их верхних входов. Имеется возможность добавления в число аргументов преобразователя Н входного сигнала DIN. Таким образом, два из входов преобразователя Н могут быть альтернативно заданы как внешние входы или выходы преобразователей G и F, третий же вход Н1 всегда является внешним.

Как видно из схемы, на выход Y в зависимости от программирования мультиплексора 4 могут подаваться значения функций G или Н, а на выход X в зависимости от программирования мультиплексора 6 - значения функций F или Н.

С помощью имеющихся функциональных преобразователей можно получать различные результаты: три отдельные функции независимых переменных (две от четырех аргументов и одну от трех при запоминании одного из выходов триггером), любую функцию пяти переменных, некоторые функции большего числа переменных (вплоть до девяти).

В зависимости от программирования мультиплексоров 3 и 5 триггеры принимают данные от функциональных преобразователей или внешнего входа DIN.

Сигнал тактирования триггеров К поступает от общего входа через мультиплексоры 7 и 8, программирование которых позволяет индивидуально выбирать полярность фронта, тактирующего триггер. Сигнал разрешения тактирования ЕС (Enable Clock) также поступает от общего входа. Благодаря наличию мультиплексоров 9 и 10 можно либо пользоваться сигналом ЕС, либо постоянно разрешить тактирование сигналом логической единицы.

Триггеры имеют асинхронные входы установки SD (Set Direct) и сброса RD (Reset Direct), один из которых через программируемый селектор S/R может быть подключен к сигналу SR, который, в свою очередь, может программироваться для подключения к любому из внешних выводов С1-С4. Возможно подключение к разным линиям С1-С4 и для выходов других мультиплексоров верхней строки (на рисунке не пронумерованы).

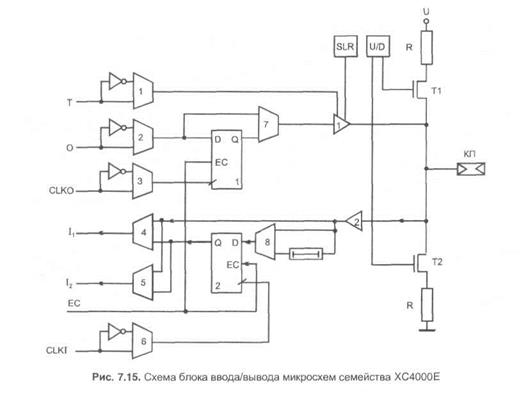

Блок ввода/вывода микросхем ХС4000Е (рис. 7.15) имеет два канала - для ввода сигналов и для вывода. В каждом канале возможна как прямая передача сигнала, так и с запоминанием его в триггере в зависимости от программирования мультиплексоров 7 и 4.

При переводе буфера 1 в третье состояние выходной контакт не должен оставаться разомкнутым, так как в этом случае на нем может накапливаться неконтролируемый заряд в силу чрезвычайно высокого входного сопротивления МОП-транзистора. Подключение к выходу одного из резисторов R либо «подтягивает» потенциал выхода к высокому уровню напряжения, либо привязывает его к нулевой точке. Вследствие своей высокоомности подключенные к выходу сопротивления R не оказывают заметного влияния на режимы работы при использовании выхода для передачи сигналов. Выбор между двумя вариантами задания потенциала разомкнутому выходу программируется элементами памяти конфигурации в схеме U/D (Up/Down). Выходной буфер 1 имеет регулировку крутизны фронта SLR (Slew Rate). Можно выбрать одно из двух значений скорости изменения выходного сигнала, для чего в схеме имеется элемент памяти SLR. Везде, где это приемлемо, желательны пологие фронты для снижения уровня помех, возникающих при переключениях буферов.

Если вывод работает в режиме входа (буфер 1 в третьем состоянии, буфер 2 активен), то внешний сигнал может подаваться в схему либо напрямую, либо через триггер, либо в обоих вариантах одновременно. В последнем случае блок ввода/вывода может демультиплексировать внешние сигналы (например, для шин адресов/данных сохранить принятый адрес в триггере и передавать данные по прямому входу). Синхросигналы триггеров различны для входного (CLKI) и выходного (CLKO) триггеров. Их полярности, как и полярность выходного сигнала О (Output), могут программироваться соответствующими мультиплексорами.

Сигнал на входе триггера 2 можно специально задерживать на несколько наносекунд программированием мультиплексора 8. Это сделано для такого подбора временного положения сигнала относительно тактирующего импульса, который обеспечивает компенсацию задержек в цепях распределения синхросигналов.