Устройства сдвига и сравнения кодов чисел

Сдвиг кода числа вправо или влево используется при выполнении различных математических операций. В сдвигающем регистре операцию сдвига можно выполнять лишь после того, как все число будет записано в регистр. Применение мультиплексоров значительно упрощает осуществление операции сдвига, так как при этом не требуется специального управляющего устройства, используемого для введения числа в регистр.

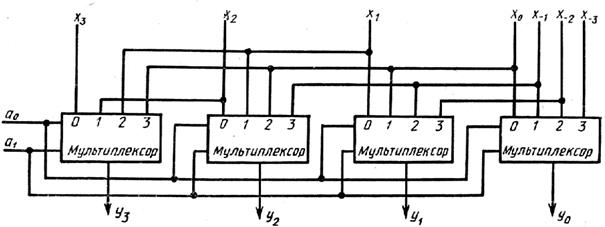

Схема комбинационного устройства сдвига на мультиплексорах приведена на рис. 13.23. Прохождения разрядов

Рис. 13.23. Функциональная схема устройства сдвига на мультиплексорах

числа х3х2х1х0х-1х-2х-3на выходы у3, у2, у1и у0мультиплексоров определяются состояниями а0и a1адресных входов. Если а0= а1 = 0, то на выходы мультиплексоров поступают разряды с нулевых входов, т. е. у3 = х3, у2= х2, у1= х1, у0 = х0. При a1= =0 и а0 = 1 (код адреса 01) на выходы мультиплексоров поступают разряды с первых входов, т. е. у3 = х2, у2= х1, у1= х0, у0 = х-1,что соответствует сдвигу двоичного кода числа на один разряд влево. Если a1 = a0 = l, то у3 = х0, у2= х-1, у1= х-2 и у0 = х-3, что соответствует сдвигу влево на три разряда. Чтобы при сдвиге влево не происходила потеря старших разрядов, перед первым мультиплексором нужно подключить такое же устройство на мультиплексорах.

Сравнение двух чисел осуществляют с помощью сравнивающих компараторов. На выходе компаратора появляется логическая единица, если сравниваемые двоичные числа А и В равны. Если А ≠ В, то на выходе будет логический нуль.

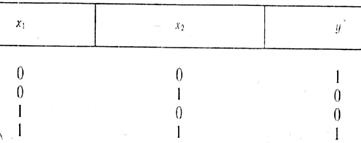

Для определения равенства двух переменных х1и х2используется логический элемент, состояния которого определяются табл. 13.5. В соответствиии с табл. 13.5

Такой ЛЭ называют ИСКЛЮЧАЮЩИМ ИЛИ — НЕ. Его реализация на логических элементах НЕ, И и ИЛИ показана на рис. 13.24, а, а на рис. 13.24, б дано условное обозначение.

Табл. 13.5. Состояния ЛЭ ИСКЛЮЧАЮЩЕЕ ИЛИ — НЕ

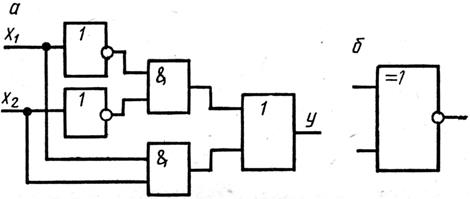

Если сравниваемые переменные имеют несколько разрядов, то подобным образом осуществляется поразрядное сравнение и схема компаратора примет вид, приведенный на рис. 13.25, а.

Рис. 13.24. Схема (а) и условное обозначение (б) ЛЭ, осуществляющего

операцию ИСКЛЮЧАЮЩЕЕ ИЛИ — НЕ

Рис. 13.25. Схемы устройств сравнения двух чисел

В случае, если при сравнении двух переменных а и b требуется установить не только их равенство или неравенство, но и указать, какая из них больше, используется схема, приведенная на рис. 13.25, б.

СУММАТОРЫ

Сумматором называют устройство, выполняющее операцию сложения цифровых кодов двух чисел. Сумматоры входят в состав арифметического устройства (АУ) ЭВМ. В АУ, кроме того, входят устройства, осуществляющие умножение и деление цифровых кодов чисел, однако и они содержат суммирующие устройства.

По принятой в ЭВМ системе счисления и кодирования сумматоры делятся на двоичные, десятичные, двоично-десятичные и др.

По способу организации суммирования сумматоры могут быть комбинационные, в которых результат суммирования не запоминается, и накапливающие (с запоминанием результата суммирования).

По способу выполнения операций сумматоры подразделяются на последовательные, параллельные и параллельно-последовательные. В последовательных сумматорах суммирование осуществляется последовательно от младших разрядов к старшим, а в параллельных суммирование одноименных разрядов происходит одновременно. В параллельно-последовательных сумматорах суммируемые многоразрядные числа разбиваются на группы, в которых производится параллельное поразрядное суммирование, а полученные при этом частичные суммы складываются последовательно.

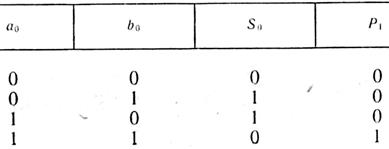

Неполный сумматор.Простейшим является одноразрядный двоичный сумматор на два входа, работа которого отражена в табл. 13.1.Так как при сложении двух одноразрядных чисел, каждое из которых равно 1, формируется единица переноса в старший разряд, то сумматор должен иметь два выхода: один — для формирования частичной суммы, относящейся к данному разряду, второй — для формирования переноса в старший разряд. Состояния такого сумматора при сложении двух одноразрядных двоичных чисел а0и b0приведены в табл. 13.6. Здесь S0— частичная сумма; Р1— сигнал переноса.

Табл. 13.6. Состояния двухвходового полусумматора

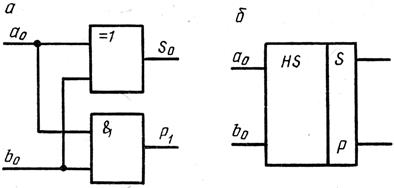

На основании табл. 13.6 легко получить логические выражения для S0и Р1: S0= а0b0 + a0b0, Р1= а0b0,из которых следует, что формирование переноса осуществляется с помощью функции И, а частичной суммы — с помощью функции неравнозначности (рис. 13.26, а).

На основании табл. 13.6 легко получить логические выражения для S0и Р1: S0= а0b0 + a0b0, Р1= а0b0,из которых следует, что формирование переноса осуществляется с помощью функции И, а частичной суммы — с помощью функции неравнозначности (рис. 13.26, а).

В данном одноразрядном сумматоре не учитывается перенос из младшего разряда, и его называют неполным, или полусумматором. Условное изображение полусумматора дано на рис. 13.26, б.

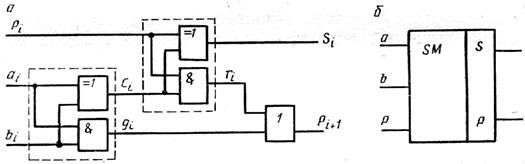

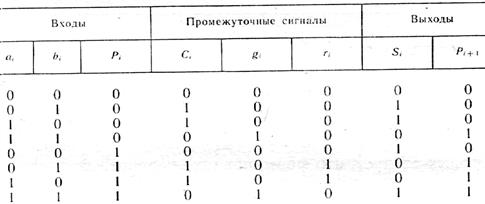

Полный сумматор.С учетом переноса из младшего разряда полный сумматор должен иметь три входа: два входа для первого и второго слагаемых и один — для цифры переноса из младшего разряда. Полный сумматор можло составить из двух полусумматоров (рис. 13.27, а). Правила его работы приведены в табл. 13.7, а условное изображение — на рис. 13.27, б.

Рис. 13.26. Схема (а) и условное обозначение (б) неполного одноразрядного сумматора

Рис. 13.27. Схема (а) и условное обозначение (6) полного одноразрядного сумматора

Табл. 13.7. Состояние полного сумматора

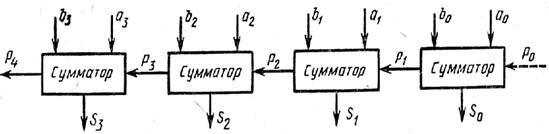

При сложении двух многоразрядных чисел на каждый разряд, кроме младшего, необходимо иметь полный сумматор. На рис. 13.28 приведена схема сумматора, предназначенного для сложения двух четырехразрядных чисел

Рис. 13.28. Функциональная схема полного сумматора для двух четырехразрядных двоичных чисел

А и В споследовательным переносом. Если для младшего разряда используется полный сумматор, то появляется возможность наращивания разрядов сумматора, тем самым осуществлять суммирование двоичных чисел с большим количеством разрядов.

Недостатком рассмотренного четырехразрядного сумматора с последовательным переносом является малая скорость выполнения операции суммирования: сигнал переноса Р2 устанавливается лишь после установки правильного значения переноса Р1, Р3 — после установки правильного значения Р2, и сигнал Р4— после установки правильного значения Р3.Для повышения быстродействия при сложении многоразрядных чисел применяются сумматоры с параллельным переносом, в которых все сигналы переноса вычисляются непосредственно по значениям входных переменных.

Сумматоры в интегральном исполнении имеются в сериях К155 и КМ155 (К155ИМ1, КМ155ИМ1 — одноразрядные полные сумматоры; К155ИМ2, КМ155ИМ2 — двухразрядные полные сумматоры; К155ИМЗ, КМ155ИМЗ — четырехразрядные сумматоры), в серии К176 (К176ИМ1 — четырехразрядный полный сумматор) и некоторых других.