Исследование дешифраторов и шифраторов

Цель работы:Изучить принципы синтеза и работы дешифраторов и шифраторов.

Задание:Произвести синтез схемы дешифратора на основе таблицы истинности. Исследовать полученную схему дешифратора. Исследовать работу микросхемы дешифратора. Собрать и исследовать схему каскадного включения дешифраторов. Собрать схему и исследовать работу шифратора.

Теоретическое введение

Дешифраторы и шифраторы принадлежат к схемам преобразователей кодов. С принятием шифрации связано представление о сжатии данных, с понятием дешифрации – обратное преобразование. В условных обозначениях дешифраторов и шифраторов используются буквы DC и CD (от слов decoder и coder соответственно).

Дешифратор – это устройство, преобразующее цифровой сигнал, заданный кодом в другую, не закодированную форму. Дешифраторы широко используются в качестве преобразователей двоичного кода в десятичный, а также во многих других устройствах.

Дешифратор цифровых сигналов – элемент цифровой техники необходимый для организации работы микропроцессорных устройств.

Классическим дешифраторомназывается комбинационная схема, имеющая n – входов и 2n выходов, преобразующая поступающий на входы код (адрес выхода) в сигнал только на одном из ее выходов (унитарный код).

Если часть входных наборов не используется, то дешифратор называют неполным и у него количество выходов меньше, чем 2n. В ЭВМ с помощью дешифраторов осуществляется выборка необходимых ячеек запоминающих устройств, расшифровка кодов операций с выдачей соответствующих управляющих сигналов и т.д.

Функционирование дешифратора описывается системой логических уравнений составленных на основе таблицы истинности. Построим дешифратор на основе таблицы истинности и составленных соответственно логических уравнений для выходных функций.

Наша задача – построить дешифратор на 3 входа. Количество выходов дешифратора N=23=8.

Обозначим адресные входы дешифратора А0, А1, А2, а выходы дешифратора – Y0, Y1, Y2, Y3, Y4, Y5, Y6, Y7. Составим на основе определения классического дешифратора таблицу истинности

Таблица истинности дешифратора

Таблица 2.11.1.

| Адресные входы | Выходы дешифратора | |||||||||

| A2 | A1 | A0 | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 |

Запишем уравнения для функций выходов дешифратора.

Y0 = А2* v A1* v A0*

Y1 = A2* v A1* v A0

Y2 = A2* v A1 v A0*

Y3 = A2* v A1 v A0

Y4 = A2 v A1* v A0*

Y5 = A2 v A1* v A0

Y6 = A2 v A1 v A0*

Y7 = A2 v A1 v A0

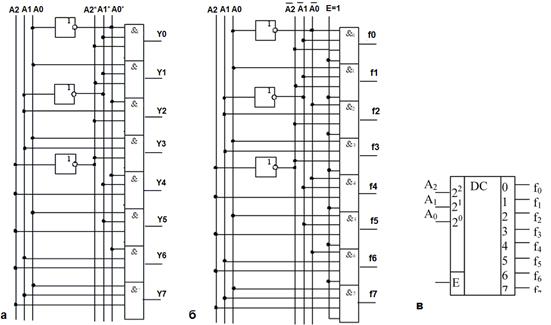

Построим схему дешифратора по полученным уравнениям (рис. 2.11.1а).

На рис. 2.11.1б показана схема дешифратора с разрешающим входом Е, на рис. 2.11в – показано обозначение дешифратора на схеме.

Рис. 2.11.1 а,б,в. Схема и микросхема дешифратора

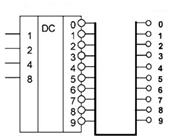

Широкое распространение получил двоично-десятичный дешифратор, имеющий четыре входа и десять выходов (не полный дешифратор). Выходы могут подключаться к разрядам цифрового или знакового индикатора, например, так как это показано на рис.2.11.2.

Рис. 2.11.2. Использование неполного дешифратора для индикации 10-ти состояний

Дешифраторы с десятичными выходами, кроме работы с цифровыми индикаторами, могут быть использованы и для других целей, например, для реализации логических функций. Рассмотрим пример синтеза логических функций для управления семисегментным индикатором.

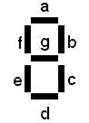

Семисегментные индикаторы имеют семь стандартно расположенных сегментов и предназначены для отображения цифровой информации (рис. 2.11.3).

Рис. 2.11.3. Схема расположения сегментов в семисегментном индикаторе

Для реализации функций управления семисегментным индикатором составим таблицу истинности (табл. 2.11.2), в которой сопоставим двоичные коды, соответствующие десятичным цифрам, поданным на входы дешифратора, и активизацию сегментов индикатора для отображения соответствующей десятичной цифры. Fn – выход дешифратора. Будем считать, что активизация сегмента соответствует подаче на него уровня логической единицы.

Таблица 2.11.2

| Цифра | Входы | Выходы | |||||||||

| F | X3 | X2 | X1 | X0 | a | b | c | d | e | f | g |

По таблице истинности можно записать булевы выражения функций для каждого сегмента семисегментного индикатора:

a = F0 v F2 v F3 v F5 v F6 v F7 v F8 v F9

……………………………………

…………………………………….

g = F2 v F3 v F4 v F5 v F6 v F8 v F9

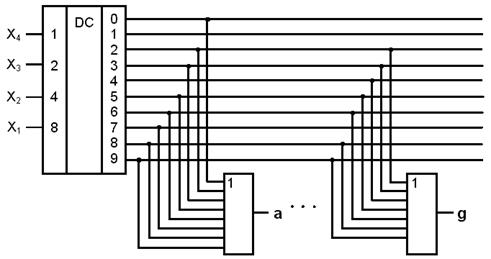

Схемная реализация дешифратора для управления семисегментным индикатором приведена на рис. 2.11.4.

Рис. 2.11.4. Применение дешифратора для управления семисегментным индикатором

В устройствах цифровой индикации для работы с индикаторами используются специализированные дешифраторы или преобразователи кода.