Минимизация структурных формул

Минимизация структурных формул осуществляется 2 способами:

1. Аналитический (математический) способ, который обеспечивает минимизацию структурной формулы с большим количеством аргументов Xi.

2. Табличная минимизация структурной формулы, например карты Карно. Этот способ обеспечивает минимизацию для количества аргументов

не более 5.

1) Аналитический способ анализа структурных формул.

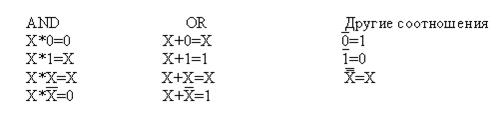

Основные соотношения и правила Булевой алгебры

Правила:

1. Перемещения: X2vX1=X1vX2 , X2X1=X1X2

2. Поглощение: X1 v X1X2=X1(1 v X2)=X1

v

v  = X2 (

= X2 (  X1 ) = X2

X1 ) = X2

3. Правило де Моргана:

Правило де Моргана применяется для перехода от классического базиса И-ИЛИ-НЕ к базису И-НЕ (AND-NOT):

Или к базису ИЛИ-НЕ (OR-NOT):

=

=

Табличный способ минимизации структурных формул с использованием карты Карно.

Сокращенная запись таблицы истинности

;

;

где 3,5,6,7 – номера единичных наборов таблицы истинности.

Минимизация структурно формулы в СДНФ имеет вид:

Y=(X2X1) v (X3X1 ) v (X3X2)

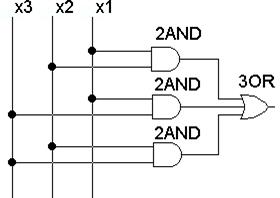

Схема устройства имеет вид :

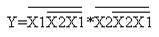

Запишемформулу в базисе АND-NOT. Для этого введем два отрицания справа от знака равенства в формуле и применим правило де Моргана:

Y=(X2X1) v (X3X1 ) v (X3X2)

Домашнее задание:Вычертить схему мажоритарного устройства в базисе 2AND-NOT. На практике в ПЛИС используются только ЛЭ 2AND-NOT.

Обратите внимание, как использовать только ЛЭ 2AND-NOT вместо 3AND-NOT (лестничная схема включения).

Синтез сумматора по модулю 2 (устройство неравнозначности).

Логическая функция сумматора по модулю 2 Y=1,если значения входных сигналов Xi неравнозначны и Y=0,если значения входных сигналов Xi равнозначны.

Применяется сумматора по модулю 2 в арифметических устройствах и в устройствах управления.

Таблица истинности для сумматора по модулю 2:

| №наб. | X2 | X1 | Y |

СДНФ:

V

V

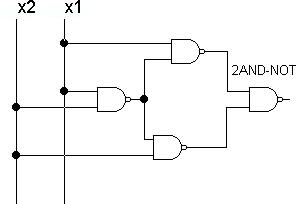

В базисе И-НЕ (итоговая формула):

Домашнее задание: Записать формулу в СКНФ, перейти в базис 2AND-NOT и вычертить схему в базисе 2AND-NOT.

Синтез КЦУ на 4 входа и один выход с использованием карты Карно

Сокращенная запись таблицы истинности.

Опасные состязания сигналов в ЦУ

Инерционность ЛЭ приводит к тому, что выходные сигналы предыдущих ЛЭ поступают на вход после ЛЭ не одновременно. По этой причине происходят ложные срабатывания ЛЭ (ошибки).

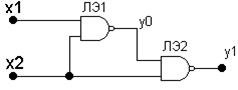

Например, в представленной схеме на вход ЛЭ2 сигналы Y0 иX2 приходят не одновременно, так происходит задержка сигнала X1 при прохождении через ЛЭ1.

Демонстрация работы схемы.

Меры борьбы: синхронизация срабатывания микросхем.