Разработка структурной схемы стенда

Им. МАРШАЛА СОВЕТСКОГО СОЮЗА

А. М. ВАСИЛЕВСКОГО

КАФЕДРА ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ

И АВТОМАТИЗИРОВАННЫХ СИСТЕМ

ДИАГНОСТИКА ВЫЧИСЛИТЕЛЬНЫХ

МАШИН И КАНАЛОВ ПЕРЕДАЧИ ДАННЫХ

Контрольные задания и методические рекомендации

Для студентов заочного обучения

Контрольная работа

«Разработка диагностического стенда с использованием

вероятностного метода тестирования»

Смоленск – 2009

УДК 681.3.016

| |

С 82

|

Сторожок Е.А. Диагностика вычислительных машин и каналов передачи данных. Контрольные задания и методические рекомендации для студентов заочного обучения. Издание академии. 2009. С.10.

Пособие предназначено для оказания помощи студентам в их самостоятельной подготовке и выполнении контрольной работы № 1 по темам «Основы теории технической диагностики», «Аппаратные средства диагностики».

© Сторожок Е.А., 2009

© ВА ВПВО ВС РФ, 2009

Введение

Методические рекомендации предназначены для студентов, изучающих дисциплину «Диагностика вычислительных машин и каналов передачи данных». В методических указаниях представлены:

- задание на контрольную работу;

- указания по содержанию пояснительной записки и графической части;

- указания по разработке структурной схемы стенда;

- указания по разработке принципиальной электрической схемы стенда;

- пример разработки принципиальной электрической схемы блока управления на основе счетчика и дешифратора.

Техническая диагностика является областью науки о распознавании состояний технических объектов. Эта задача возникает при производстве изделий на заводах и затем при их технической эксплуатации. При выпуске изделия на заводе необходимо убедиться в его исправности. Это означает, что изделие должно удовлетворять всем требованиям нормативно-технической и конструкторской документации. Если какое-то требование не выполняется, то изделие бракуется. Процент годности выпускаемой продукции является главным показателем качества производства.

В процессе эксплуатации технического объекта необходимо контролировать его работоспособность. При возникновении отказов объект теряет способность выполнять свои основные функции. В этом случае требуется зафиксировать факт отказа, определить место его возникновения и осуществить замену неисправного элемента или блока. Впоследствии такие блоки могут ремонтироваться специализированными бригадами в ремонтно-технологических участках.

ЗАДАНИЕ НА КОНТРОЛЬНУЮ РАБОТУ

Разработать стенд для автоматического контроля ТЭЗ (типовой элемент замены) с использованием некомпактного вероятностного метода тестирования. Вариант задания определяется по списочному номеру студента в соответствии с таблицей 1.

Таблица 1

| Номер студента по списку | ТЭЗ (ИМС узла) | Разрядность ГПСП | Размерность теста (число тестовых проверок) |

| К155ИР13 | |||

| К530ИР18 | |||

| К530ИР19 | |||

| К555ИР9 | |||

| К555ИР10 | |||

| К555ИР11А | |||

| К555ИР16 | |||

| К555ИР15 | |||

| КР1554ИЕ6 | |||

| К555ИЕ9 | |||

| К555ИЕ10 | |||

| К555ИЕ13 | |||

| К555ИЕ14 | |||

| К555ИЕ15 | |||

| К555ИЕ17 | |||

| К555ИЕ18 | |||

| К155ИД3 | |||

| К555ИД6 | |||

| К555ИД7 | |||

| К555ИД4 | |||

| К555ИД10 | |||

| К555ИД5 | |||

| К555ИД19 | |||

| К555ИД18 | |||

| К555ИД6 |

Примечание: В качестве ТЭЗ выступают интегральные микросхемы (ИМС) цифровых узлов. Разрядность генератора псевдослучайной последовательности (ГПСП) определяет количество проверяемых разрядов узла. Разрядность счетчика циклов определяется размерностью теста.

Состояние выходов контролируемого и эталонного ТЭЗов должны отображаться в двоичном коде с помощью светодиодов. В случае полного совпадения откликов с эталонного и контролируемого ТЭЗов на всех тестах, должен формироваться сигнал «Годен» с отображением его на цифровом табло. В противном случае, формируется сигнал «Брак», проверка останавливается и загорается соответствующий светодиод. Продолжение проверки должно осуществляться с этого тестового вектора до следующего несовпадения на выходах ТЭЗов или до конца проверки.

Для выполнения контрольной работы необходимо:

• определить свой вариант задания;

• изучить рекомендуемую литературу;

• разработать структурную схему стенда;

• рассчитать параметры временной диаграммы функционирования стенда;

• разработать электрические схемы ГПСП, счетчика циклов, формирователя входных воздействий, схемы сравнения, генераторов тактовых и строб импульсов, блока индикации и управления и всего стенда в целом;

• составить перечень комплектующих изделий;

• промоделировать работу стенда на ПЭВМ.

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

Объем и содержание контрольной работы

Контрольная работа состоит из пояснительной записки и графической части.

Пояснительная записка должна включать:

1.Задание на контрольную работу и исходные данные;

2.Теоретический вопрос;

3.Описание принципа работы разрабатываемого стенда, включающее структурную схему, временные диаграммы работы и т.д.;

4. Расчет параметров временной диаграммы функционирования стенда;

5. Выбор элементной базы для реализации стенда, разработка электрических схем блоков и расчет их электрических параметров;

6. Перечень комплектующих изделий;

7. Результаты моделирования работы стенда.

Графическая часть должна содержать:

1.Принципиальные электрические схемы блоков;

2.Принципиальную электрическую схему стенда.

Графические материалы должны быть оформлены с соблюдением требований ЕСКД.

Теоретический вопрос

В этой части работы необходимо изложить известные методы контроля узлов и блоков ЭВМ, дать их сравнительную характеристику, привести структурные схемы тестирования.

Работу над данной частью контрольной работы рекомендуется начать с изучения лекционного материала и учебной литературы [7]. Не следует переписывать вопрос целиком из каких-либо монографий или учебников. В тексте обязательно должны быть ссылки на используемые литературные источники.

Разработка структурной схемы стенда

4.

Вероятностное тестирование характеризуется тем, что на входы проверяемого устройства подаются случайные или псевдослучайные последовательности [7]. В самом общем виде схему вероятностного некомпактного тестирования можно представить в следующем виде (рис. 1).

Подсчет количества тестовых векторов в автоматических тестерах обычно проводится с использованием счетчика циклов. Поэтому в разрабатываемом стенде необходимо предусмотреть такой блок.

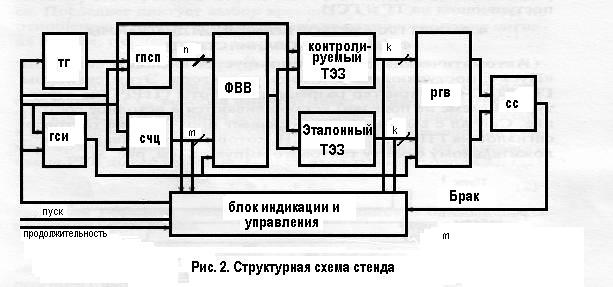

С учетом изложенного структурная схема автоматического стенда (один из возможных вариантов) может иметь вид (рис. 2).

В состав стенда входят следующие блоки:

• тактовый генератор (ТГ);

• генератор стробирующих импульсов (ГСИ);

• генератор псевдослучайной последовательности (ГПСП);

• счетчик циклов (СЧЦ);

• формирователь выходных воздействий (ФВВ);

• входной регистр (РГВ);

• схема сравнения (СС);

• блок индикации и управления (БИУ).

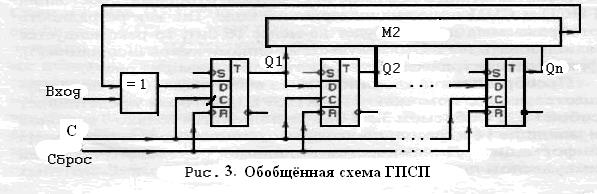

Вопросы, связанные с проектированием полиномиальных счетчиков или так называемых генераторов псевдослучайных последовательностей, недостаточно широко освещены в научно-технической литературе. Такие счетчики строятся на основе сдвиговых регистров, у которых в цепи обратной связи используются сумматоры по модулю 2 [3, 4]. Причем, в сдвиговых регистрах должны применяться триггеры с динамической записью информации. На рис. 3 показана обобщенная схема такого генератора.

При нулевых состояниях всех триггеров и нуле на входе схема не реагирует на поступающие синхросигналы С, оставаясь в нулевом состоянии. Если на вход схемы будет подан высокий уровень напряжения, то по очередному положительному фронту тактового сигнала С счетчик изменит свое состояние. Поступление следующих тактовых сигналов вызывает смену состояний счетчика по некоторому закону, зависящему от номеров выходов, с которых снимаются сигналы обратной связи. В табл. 2 приведены номера выходов регистра сдвига, с которых снимаются сигналы обратной связи. При этом генерируется псевдослучайная последовательность максимальной длины. Статистические характеристики последовательностей единиц и нулей, получаемых с выхода любого триггера, близки к характеристикам случайной последовательности и тем ближе к ней, чем больше разрядность регистра сдвига. Выход из режима генерации ГПСП осуществляется только по цепи асинхронного сброса.

|

| Разрядность регистра сдвига | Номера выходов, с которых снимаются сигналы обратной связи | Длина последовательности |

| 8,7,5,3 | ||

| 9,4 | ||

| 10,3 | ||

| 11,2 | ||

| 12,11,8,6 | ||

| 13,10,6,4 | ||

| 14,13,8,4 | ||

| 15,1;15,4;15,7 | ||

| 16,12,9,7 | ||

| 17,3;17,5;17,6 | ||

| 18,7;18,11 | ||

| 19,18,17,14 | ||

| 20,3;20,17 |

Примечание. В таблице для некоторых разрядностей регистра приведено несколько эквивалентных вариантов создания цепи обратной связи.

5. Пример разработки принципиальной электрической схемы БУ

Блок управления (рис. 4) может быть построен на основе двоичного счетчика DD1 и дешифратора DD2. Моменты выработки требуемых управляющих сигналов определяются номерами выходов дешифратора, с которых они снимаются. Временные диаграммы работы блока управления представлены на рис. 5.

Счётчик DD1 построен на основе интегральной микросхемы К155ИЕ5. Данная микросхема имеет в своём составе два счётчика- делителя частоты. Первый одноразрядный счётчик имеет счётный вход +1А, выход А1 и вход установки в ноль- вывод 2. Второй трёхразрядный счётчик имеет счётный вход +1В, выходы В1, В2, В3 и вход установки в ноль- вывод 3. Для получения четырёхразрядного счётчика необходимо вывод 12 соединить с выводом 1, а выводы 2 и 3 соединить вместе. У полученного таким образом счётчика счётным входом будет являться 14 вывод микросхемы. На этот вход поступают прямоугольные импульсы с выхода тактового генератора ТГ. Выходы СТ2 соединены с входами дешифратора DD2. Дешифратор- демультиплексор реализован на основе микросхемы К155ИД3. Выходы дешифратора являются инверсными. Это необходимо учитывать при съёме выходных сигналов, используемых в качестве управляющих. Так, в приведённом на рис. 4 варианте реализации БУ управляющий сигнал «Уст. 0», предназначенный для установки в ноль счётчика СТ2, предварительно инвертируется при помощи логического элемента НЕ, реализованного на микросхеме DD3.1. Инвертирование необходимо, так как вход установки в 0 счётчика является прямым статическим, а в качестве активного сигнала для данного входа выступает высокий уровень напряжения, соответствующий «Лог. 1».

| |||

| |||

|

|

|

|

|

Вопросы для подготовки к зачёту

1. Математические модели объектов диагноза.

2. Системы диагностирования.

3. Функциональные схемы систем диагностирования.

4. Функциональное диагностирование.

5. Тестовое диагностирование.

6. Алгоритмы диагностирования и методы их построения.

7. Диагностирование логических схем.

8. Модели неисправностей логических схем.

9. Тесты логических элементов.

10. Методы построения тестов.

11. Вероятностное тестирование.

12. Диагностирование дискретных устройств с памятью.

13. Построение проверяющих и диагностических тестов.

14. Сигнатурный анализ.

15. Методы сканирования.

16. Функциональное диагностирование дискретных систем.

17. Диагностирование микропроцессорных систем.

18. Схемы организации тестового диагностирования.

19. Тестирование элементов микропроцессорной системы (МПС).

20. Тестирование программ.

21. Средства функционального диагностирования МПС.

22. Диагностирование средств телеобработки данных.

23. Диагностирование мультиплексора передачи данных.

24. Диагностирование канала передачи данных.

25. Проверка канала тональной частоты.

26. Системы диагностирования.

27. Характеристики систем диагностирования.

28. Методы диагностирования.

29. Метод диагностирования, ориентированный на проверку сменных блоков.

30. Диагностирование устройств АСОИУ.

31. Диагностирование ОЗУ.

32. Особенности диагностирования каналов ввода-вывода.

33. Сериализация данных о состоянии ЭВМ.

34. Диагностическая программа Sandra.

35. Диагностическая программа Everest.

36. Диагностическая программа Motherboard Monitor.

37. Диагностика и устранение неисправности жесткого диска компьютера.

38. Мониторинг температуры и напряжения питания процессора, материнской платы и винчестера (Motherboard Monitor).

39. Диагностическая программа монитора Nokia Monitor Test.

40. Диагностическая программа процессора Cpu-Z.

41. Диагностика процессоров.

42. Диагностика оперативной памяти (Memory Diagnostic).

|