Организация функционирования микропроцессорной системы (МПС).

8.1.1. Назначение, параметры и классификация микропроцессоров

Микропроцессором называется программно-управляемое устройство для обработки цифровой информации и управления процессом обработки, реализованное в виде большой (БИС) или сверхбольшой (СБИС) интегральной микросхемы.

Микропроцессор обрабатывает информацию в компьютерах, системах управления объектами и процессами, в информационно-измерительных системах, используемых в промышленности, бытовой технике, аппаратуре связи и многих других областях применения.

Микропроцессор описывается множеством параметров, присущих как электронным приборам: быстродействие, потребляемая мощность, габариты и масса, количество уровней питания, надежность, стоимость, тип корпуса, температурный диапазон и др., так и вычислительным средствам: разрядность, цикл выполнения команд или микрокоманд, число внутренних регистров, наличие микропрограммного управления, тип стековой памяти, состав программного обеспечения и др.

Микропроцессорный комплект (МПК) содержит набор БИС для построения микропроцессорных систем, в который входят микросхемы центрального процессора, микросхемы для организации связи с внешними устройствами, тактовый генератор и др.

По числу БИС в микропроцессорном комплекте различают однокристальные, многокристальные (логическая структура процессора разделена на функционально законченные части) и многокристальные секционные МП.

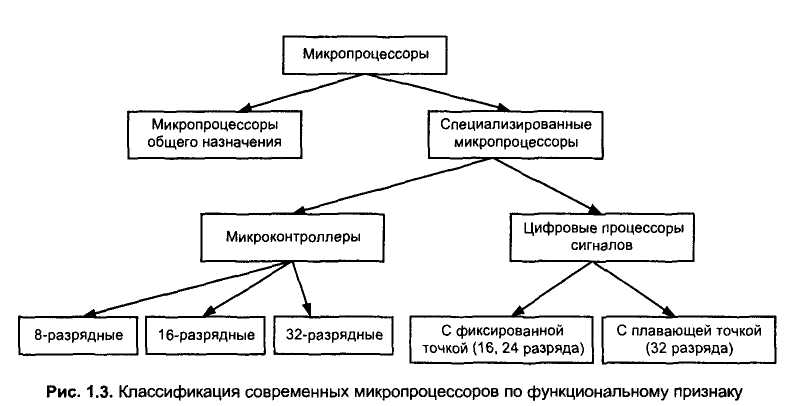

По функциональному признаку выделяются два класса: микропроцессоры общего назначения и специализированные микропроцессоры (рисунок 8.1.1.1).

Рисунок 8.1.1.1. Классификация МП

Микропроцессоры общего назначения предназначены для решения широкого круга задач обработки разнообразной информации. Их основной областью использования являются персональные компьютеры, рабочие станции, серверы и другие цифровые системы массового применения.

Среди специализированных микропроцессоров наиболее широкое распространение получили микроконтроллеры, предназначенные для выполнения функций управления различными объектами. Характерной особенностью структуры микроконтроллеров является размещение на одном кристалле с центральным процессором внутренней памяти и большого набора периферийных устройств. В состав периферийных устройств обычно входят несколько 8-разрядных параллельных портов ввода-вывода данных (от 1 до 8), один или два последовательных порта, таймерный блок, аналого-цифровой преобразователь. Микроконтроллеры принято подразделять на 8-, 16- и 32-разрядные. Основными областями применения 8-разрядных микроконтроллеров являются бытовая и измерительная техника, промышленная автоматика, автомобильная электроника, теле-, видео- и аудиоаппаратура, средства связи. Основная сфера применения 16 - разрядных микроконтроллеров - сложная промышленная автоматика, телекоммуникационная аппаратура, медицинская и измерительная техника. Микроконтроллеры, обрабатывающие 32 разрядные данные находят широкое применение в системах управления сложными объектами промышленной автоматики (двигатели, робототехнические устройства, средства комплексной автоматизации производства), в контрольно-измерительной аппаратуре и телекоммуникационном оборудовании

Цифровые процессоры сигналов (DSP – Digital Signal Processor) ориентированы на реализацию процедур, обеспечивающих необходимое преобразование аналоговых сигналов, представленных в цифровой форме (в виде последовательности числовых значений). Специфической особенностью алгоритмов обработки аналоговых сигналов является необходимость последовательного выполнения ряда команд умножения-сложения с накоплением промежуточного результата в регистре-аккумуляторе. Поэтому архитектура ЦПС ориентирована на реализацию быстрого выполнения операций такого рода. Набор команд этих процессоров содержит специальные команды MAC (Multiplication with Accumlation), реализующие эти операции.

По виду обрабатываемых входных сигналов различают аналоговые и цифровые МП.

По разрядности различают МП с фиксированной и с изменяемой разрядностью слова.

По характеру временной организации работы МП делят на синхронные и асинхронные.

По количеству выполняемых программ различают однопрограммные и мультипрограммные МП.

По способу управления МП подразделяются на микропрограммируемые и с жестким управлением.

Основными направлениями развития микропроцессоров является увеличение их производительности и расширение функциональных возможностей, что достигается как повышением уровня микроэлектронной технологии, используемой для производства микропроцессоров, так и применением новых архитектурных и структурных вариантов их реализации. Развитие микроэлектронной технологии обеспечивает непрерывное уменьшение размеров полупроводниковых компонентов, размещаемых на кристалле микропроцессора. При этом уменьшаются паразитные емкости, определяющие задержку переключения логических элементов, и увеличивается число элементов, размещаемых на кристалле. В настоящее время разрешающая способность промышленной технологии изготовления микросхем обеспечивает создание компонентов с минимальными размерами 0,13 – 0,18 мкм. При этом обеспечивается создание микропроцессоров, работающих с тактовой частотой до 1 – 2 ГГц и содержащих на кристалле десятки миллионов транзисторов

8.1.2. Основные варианты архитектуры и структуры микропроцессоров

Архитектурой процессора называется комплекс его аппаратных и программных средств, предоставляемых пользователю. В это общее понятие входит набор программно-доступных регистров и исполнительных (операционных) устройств, система основных команд и способов адресации, объем и структура адресуемой памяти, виды и способы обработки прерываний.

Структура микропроцессора определяет состав и взаимодействие основных устройств и блоков, размещенных на его кристалле. В эту структуру входят:

· центральный процессор (процессорное ядро), состоящее из устройства управления (УУ), одного или нескольких операционных устройств (ОУ);

· внутренняя память (РЗУ, кэш-память, блоки оперативной и постоянной памяти);

· интерфейсный блок, обеспечивающий выход на системную шину и обмен данными с внешними устройствами через параллельные или последовательные порты ввода/вывода;

· периферийные устройства (таймерные модули, аналого-цифровые преобразователи, специализированные контроллеры);

· различные вспомогательные схемы (генератор тактовых импульсов, схемы для выполнения отладки и тестирования, сторожевой таймер и ряд других).

Архитектура и структура микропроцессора тесно взаимосвязаны. Реализация тех или иных архитектурных особенностей требует введения в структуру микропроцессора необходимых аппаратных средств (устройств и блоков) и обеспечения соответствующих механизмов их совместного функционирования.

В современных микропроцессорах реализуются следующие варианты архитектур.

По набору выполняемых команд и способов адресации различают CISC и RISC архитектуры.

CISC (Complex Instruction Set Computer) - архитектура реализована во многих типах микропроцессоров, выполняющих большой набор разноформатных команд с использованием многочисленных способов адресации. Примером CISC-процессоров являются микропроцессоры семейства Pentium. Они выполняют более 200 команд разной степени сложности, которые имеют размер от 1 до 15 байт и обеспечивают более 10 различных способов адресации. Такое большое многообразие выполняемых команд и способов адресации позволяет программисту реализовать наиболее эффективные алгоритмы решения различных задач. Однако при этом существенно усложняется структура микропроцессора, особенно его устройства управления, что приводит к увеличению размеров и стоимости кристалла, снижению производительности.

RISC (Reduced Instruction Set Computer) – архитектура отличается использованием ограниченного набора команд фиксированного формата. Современные RISC-процессоры обычно реализуют около 100 команд, имеющих фиксированный формат длиной 4 байта. Также значительно сокращается число используемых способов адресации. Обычно в RISC-процессорах все команды обработки данных выполняются только с регистровой или непосредственной адресацией. При этом для сокращения количества обращений к памяти RISC-процессоры имеют увеличенный объем внутреннего РЗУ- от 32 до нескольких сотен регистров, тогда как в CISC-процессорах число регистров общего назначения обычно составляет 8-16.

По способу реализации памяти и организации

выборки команд и данных различаются процессоры с Принстонской и Гарвардской архитектурой.

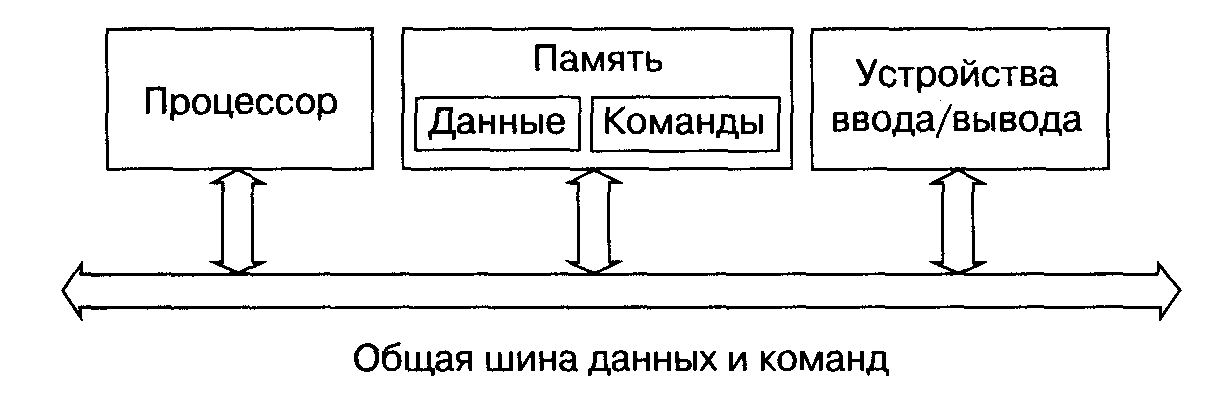

Принстонская архитектура (архитектура Фон-Неймана) представлена на рисунке 8.1.2.1.

Рисунок 8.1.2.1. Принстонская архитектура

Принстонская архитектура характеризуется использованием общей оперативной памяти для хранения программ, данных, а также для организации стека. Для обращения к этой памяти используется общая системная шина, по которой в процессор поступают и команды, и данные. Эта архитектура имеет ряд важных достоинств. Наличие общей памяти позволяет оперативно перераспределять ее объем для хранения отдельных массивов команд, данных и реализации стека в зависимости от решаемых задач. Таким образом, обеспечивается возможность более эффективного использования имеющегося объема оперативной памяти в каждом конкретном случае применения микропроцессора. Использование общей шины для передачи команд и данных значительно упрощает отладку, тестирование и текущий контроль функционирования системы, повышает ее надежность. Однако ей присущи и существенные недостатки. Основным из них является необходимость последовательной выборки команд и обрабатываемых данных по общей системной шине. При этом общая шина становится «узким местом» (bottleneck - «бутылочное горло»), которое ограничивает производительность цифровой системы.

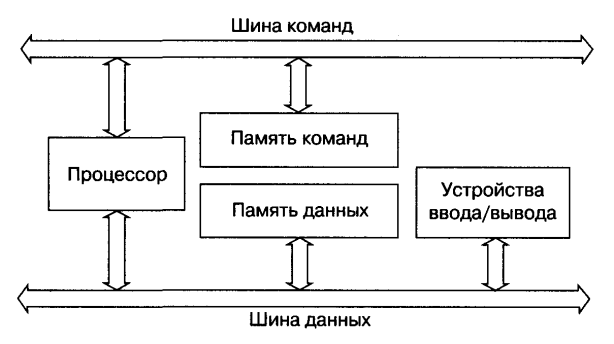

Гарвардская архитектура представлена на рисунке 8.1.2.2.

Рисунок 8.1.2.2. Гарвардская архитектура

Гарвардская архитектура характеризуется физическим разделением памяти команд (программ) и памяти данных. В ее оригинальном варианте использовался также отдельный стек для хранения содержимого программного счетчика, который обеспечивал возможности выполнения вложенных подпрограмм. Каждая память соединяется с процессором отдельной шиной, что позволяет одновременно с чтением-записью данных при выполнении текущей команды производить выборку и декодирование следующей команды. Благодаря такому разделению потоков команд и данных и совмещению операций их выборки реализуется более высокая производительность, чем при использовании Принстонской архитектуры. Недостатки Гарвардской архитектуры связаны с необходимостью проведения большего числа шин, а также с фиксированным объемом памяти, выделенной для команд и данных, назначение которой не может оперативно перераспределяться в соответствии с требованиями решаемой задачи. Поэтому приходится использовать память большего объема, коэффициент использования которой при решении разнообразных задач оказывается более низким, чем в системах с Принстонской архитектурой. Однако развитие микроэлектронной технологии позволило в значительной степени преодолеть указанные недостатки, поэтому Гарвардская архитектура широко применяется во внутренней структуре современных высокопроизводительных микропроцессоров, а во внешней структуре большинства микропроцессорных систем реализуются принципы Принстонской архитектуры.

8.1.3 Организация конвейера команд

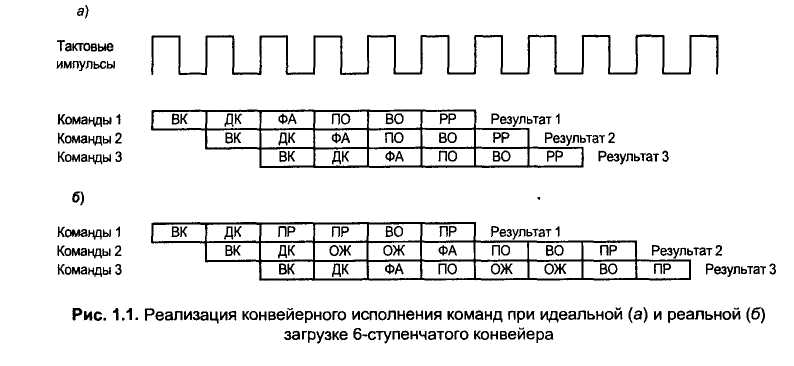

Во внутренней структуре современных высокопроизводительных микропроцессоров реализуется конвейерный принцип выполнения команд. При этом процесс выполнения команды разбивается на ряд этапов. На рисунке 3.1.3.1 а) приведен пример разбиения команды на шесть этапов ее выполнения:

1) выборка очередной команды (ВК);

2) декодирование выбранной команды (ДК);

3) формирование адреса операнда (ФА);

4) прием операнда из памяти (ПО);

5) выполнение операции (ВО);

6) размещение результата в памяти (РР).

Реализация каждого этапа занимает один такт машинного времени и производится устройствами и блоками процессора, образующими ступени исполнительного конвейера, на каждой из которых выполняется соответствующая микрооперация. При последовательной загрузке в конвейер выбираемых команд каждая его ступень реализует определенный этап выполнения очередной команды. Таким образом, в конвейере одновременно находятся несколько команд, находящихся на разных этапах выполнения. В идеальном варианте при полной загрузке конвейера на его выход в каждом такте будет поступать результат выполнения очередной команды (рисунок 8.1.3.1 а) В этом случае производительность процессора (операций/с) будет равна его тактовой частоте (тактов/с).

Однако такая эффективная работа конвейера обеспечивается только при его равномерной загрузке однотипными командами. Реально отдельные ступени конвейера могут оказаться незагруженными, находясь в состоянии ожидания или простоя.

Рисунок 8.1.3.1 Разбиение команды на шесть этапов ее выполнения

На рисунке 8.1.3.1 б) показан пример работы 6-ступенчатого конвейера при выполнении фрагмента реальной программы, когда отдельные ступени оказываются в состоянии ожидания (ОЖ) или простоя (ПР).

Наибольшая эффективность использования конвейера обеспечивается при поступлении однородных команд. Причиной снижения эффективности конвейера являются команды условного ветвления. Если выполняется условие ветвления, то приходится производить перезагрузку конвейера командами из другой ветви программы, что требует выполнения дополнительных рабочих тактов и вызывает значительное снижение производительности.

В современных высокопроизводительных микропроцессорах эффективность конвейера обеспечивается увеличением числа его ступеней (достигает 10 и более), а также сокращением числа его перезагрузок при выполнении условных переходов с помощью реализации механизмов предсказания направления ветвления.

8.1.4 Структурная схема МПС

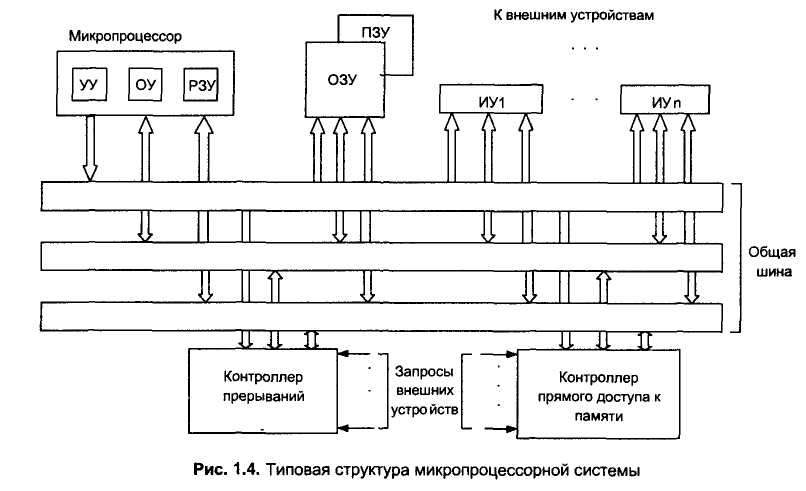

Большинство микропроцессорных систем имеет магистрально-модульную структуру (рисунок 8.1.4.1), в которой отдельные устройства (модули), входящие в состав системы, обмениваются информацией по общей системной шине - магистрали.

Рисунок 8.1.4.1 Типовая структура МПС

Основным модулем системы является микропроцессор, который содержит устройство управления (УУ), операционное устройство (ОУ) и регистровое запоминающее устройство (РЗУ) - внутреннюю память, реализованную в виде набора регистров. Оперативное запоминающее устройство (ОЗУ) служит для хранения выполняемой программы (или ее фрагментов) и данных, подлежащих обработке. Так как обращение к ОЗУ по системной шине требует значительных затрат времени, в большинстве современных высокопроизводительных микропроцессоров дополнительно вводится быстродействующая промежуточная память (кэш-память) ограниченного объема (от нескольких Кбайт до сотен Кбайт).

Постоянное запоминающее устройство (ПЗУ) служит для хранения констант и стандартных (неизменяемых) программ. В ПЗУ обычно записываются программы начальной инициализации (загрузки) систем, тестовые и диагностические программы и другое служебное программное обеспечение. В микропроцессорных системах, управляющих определенными объектами с использованием фиксированных или редко изменяемых программ, для их хранения также обычно используется ПЗУ (память ROM - Read-Only Memory) или репрограммируемое ПЗУ (память EEPROM - Electrically Erased Programmable Read-Only Memory или флэш-память).

Остальные устройства являются внешними и подключаются к системе с помощью интерфейсных устройств (ИУ), реализующих определенные протоколы параллельного или последовательного обмена. Такими внешними устройствами могут быть клавиатура, монитор, внешние запоминающие устройства (ВЗУ), использующие гибкие или жесткие магнитные диски, оптические диски (CD-ROM), магнитные ленты и другие виды носителей информации, датчики и преобразователи информации (аналого-цифровые или цифроаналоговые), разнообразные исполнительные устройства (индикаторы, принтеры, электродвигатели, реле и другие). Для реализации различных режимов работы к системе могут подключаться дополнительные устройства - контроллеры прерываний, прямого доступа к памяти и другие, реализующие необходимые специальные функции управления.

Данная структура соответствует архитектуре Фон-Неймана.

Системная шина содержит несколько десятков (в сложных системах более 100) проводников, которые в соответствии с их функциональным назначением подразделяются на отдельные шины - адреса А, данных D и управления С.

Шина А служит для передачи адреса, который формируется микропроцессором и позволяет выбрать необходимую ячейку памяти ОЗУ (ПЗУ) или требуемое ИУ при обращении к внешнему устройству. Разрядность шины адреса определяет максимальный объем адресуемой процессором внешней памяти. Например, 32-разрядная шина А обеспечивает адресацию памяти объемом до 4 Гбайт. Во многих микропроцессорных системах передача адреса и данных сопровождается посылкой контрольных битов четности, которые обеспечивают выявление возможных ошибок, возникающих в процессе обмена.

Шина D служит для выборки команд, поступающих из ОЗУ или ПЗУ в УУ микропроцессора, и для пересылки обрабатываемых данных (операндов) между микропроцессором и ОЗУ или ИУ (внешним устройством). Разрядность шины данных обычно соответствует разрядности операндов, обрабатываемых микропроцессором. Поэтому чаще всего шина D содержит 8, 16 или 32 линии.

В некоторых системах для уменьшения числа необходимых линий связи и соответствующих выводов и контактов используется мультиплексирование линий адреса и данных. В таких системах для передачи адреса и данных используются одни и те же линии связи, на которые сначала выдается адрес, а затем поступают данные.

По шине С передаются разнообразные управляющие сигналы, определяющие режимы работы памяти (запись или считывание), интерфейсных устройств (ввод или вывод информации) и микропроцессора (запуск, запросы внешних устройств на обслуживание, информация о текущем режиме работы и другие сигналы). Разрядность шины управления С определяется организацией работы системы, возможностями реализации различных режимов ее функционирования, используемыми методами контроля микропроцессора и других устройств. Поэтому набор передаваемых по шине С управляющих сигналов является индивидуальным для каждой модели микропроцессора. Имеется ряд управляющих сигналов, которые используются в большинстве микропроцессорных систем. К ним относятся сигналы начального запуска (RESET), сигналы, задающие режим работы памяти (чтение - RD, запись - WR), сигналы, необходимые для реализации прерываний и ряд других.

8.1.5 Функционирование МПС при выполнении основной программы. Процедура выполнения команд. Рабочий цикл микропроцессора.

В процессе функционирования микропроцессорной системы реализуются следующие основные режимы ее работы:

• выполнение основной программы;

• вызов подпрограммы;

• обслуживание прерываний и исключений;

• прямой доступ к памяти.

Структура команд. Команды микропроцессора могут быть безадресными, одноадресными и двухадресными.

Безадресными являются команды, для выполнения которых не требуется операнд (например, команда останова HALT) или размещение операнда определяется структурой микропроцессора и задается непосредственно кодом операции. Например, в микропроцессорах, использующих регистр-аккумулятор, выполнение ряда команд над одним операндом предполагает, что он размещается в этом регистре.

Одноадресные команды содержат адрес одного операнда. Эти команды используются для выполнения операций над одним операндом, например, сдвигов, логической инверсии, изменения знака и ряда других. В микропроцессорах с аккумуляторной организацией обработки данных такие команды служат также для выполнения операций над двумя операндами, один из которых находится в аккумуляторе.

В двухадресных командах содержатся адреса двух операндов. Если при этом один из операндов выбирается из памяти, то другой операнд хранится в регистре (регистровая адресация) или содержится непосредственно в команде (непосредственная адресация) Результат операции записывается на место одного из операндов, значение которого при этом теряется.

Следует отметить, что в некоторых типах микропроцессоров реализуются также трехадресные команды, где задаются отдельные адреса размещения двух операндов и результата операции. Такие команды используют только регистровую адресацию и выполняются в микропроцессорах с RISC-архитектурой, имеющих значительный объем РЗУ, например, в PowerPC.

Выполнение основной программы. В этом режиме процессор выбирает из ОЗУ очередную команду программы и выполняет соответствующую операцию. Команда представляет собой многоразрядное двоичное число (рисунок 8.1.5.1), которое состоит из двух частей (полей) – кода операции (КОП) и кода адресации операндов (КАД).

| Код операции (КОП) | Код адресации операнда (КАД) |

Рисунок 8.1.5.1. Формат типовой команды микропроцессора.

Код операции КОП задает вид операции, выполняемой данной командой, а код адресации КАД определяет выбор операндов (способ адресации), над которыми производится заданная операция.

Для хранения адреса очередной команды служит специальный регистр процессора - программный счетчик PC (Program Counter), содержимое которого автоматически увеличивается на 1 после выборки следующего байта команды. Таким образом, обеспечивается последовательная выборка команд в процессе выполнения программы. При выборке очередной команды содержимое PC поступает на шину адреса, обеспечивая считывание из ОЗУ следующей команды выполняемой программы. При реализации ветвлений или других изменений последовательности выполнения команд выполняется загрузка в PC нового содержимого, в результате чего производится переход к другой ветви программы или подпрограмме.

Принятая из ОЗУ команда поступает в регистр команд, входящий в состав УУ процессора. Затем производится дешифрация команды, в процессе которой определяется вид выполняемой операции (расшифровка КОП) и формируется адрес необходимых операндов (расшифровка КАД). В соответствии с кодом поступившей команды УУ процессора генерирует последовательность микрокоманд, обеспечивающих выполнение заданной операции.

Рабочий цикл микропроцессора.Каждая микрокоманда выполняется в течение одного машинного такта - периода тактовых импульсов, задающих рабочую частоту всех внутренних узлов и блоков микропроцессора. Таким образом, тактовая частота микропроцессора (1ГГц и более) определяет время выполнения отдельных микрокоманд, последовательность которых обеспечивает получение необходимого результата операции (поступившей команды).

При выполнении команды может потребоваться обращение к ОЗУ или внешнему устройству. Для выполнения такой команды требуется определенное количество командных циклов и тактов. Командным циклом называется промежуток времени, требуемый для выполнения обращения к ОЗУ или внешнему устройству с помощью системной шины. Обычно реализация такого цикла занимает от 2 до 4 системных тактов (периодов синхросигналов шины), которые требуются для:

– установки требуемого адреса,

– выдачи сигналов, определяющих вид цикла - чтение или запись,

– получения сигнала готовности к обмену (от памяти или внешних устройств),

– собственно передачи данных или команд.

При современной технологии изготовления системных плат частота синхросигналов шины обычно составляет десятки мегагерц (типичные значения 25, 33, 50, 66, 75, 100, 133 МГц).

Таким образом, при выполнении каждой команды в первых циклах производится ее выборка из ОЗУ, а последующая дешифрация команды определяет необходимое число циклов для ее выполнения (если для выполнения команды не требуется обращение к памяти или УВВ, то такая команда выполняется за один цикл, если требуется обращение к памяти или УВВ то потребуются дополнительные циклы чтения (ввода) или записи (вывода).

Из–за различного быстродействия МП и системной шины в МПС включается промежуточная буферная память, в которой хранятся данные, посылаемые микропроцессором на системную шину.

Текущее состояние процессора при выполнении программы определяется содержимым регистра состояния SR (State Register), в микропроцессорах Pentium данный регистр называется EFLAGS). Этот регистр содержит биты управления, задающие режим работы процессора, и биты признаков (флаги), указывающие характеристики результата выполненной операции:

N – признак знака (старший бит результата), N = 0 - при положительном результате, N = 1 -при отрицательном результате;

С – признак перенос, С = 1, если при выполнении операции образовался перенос из старшего разряда результата;

V – признак переполнения, V = 1, если при выполнении операций над числами со знаком произошло переполнение разрядной сетки процессора;

Z – признак нуля, Z = 1, если результат операции равен нулю;

P – признак четности результата и др.

8.1.6 Функционирование МПС при выполнении подпрограммы

Обращение к подпрограмме реализуется при поступлении в микропроцессор специальной команды CALL (в некоторых процессорах эта команда имеет мнемоническое обозначение JSR – Jump-to-SubRoutine), которая указывает адрес первой команды вызываемой подпрограммы. Этот адрес загружается в PC, обеспечивая в следующем командном цикле выборку первой команды подпрограммы. Предварительно выполняется процедура сохранения в специальном регистре или ячейке памяти текущего содержимого PC, где хранится адрес следующей команды основной программы, чтобы обеспечить возвращение к ней после выполнения подпрограммы. Возврат к основной программе реализуется при поступлении команды RETURN (мнемоническое обозначение RET), завершающей подпрограмму. По этой команде сохранявшееся содержимое PC снова загружается в программный счетчик, обеспечивая выполнение команды, которая в исходной программе следовала за командой CALL.

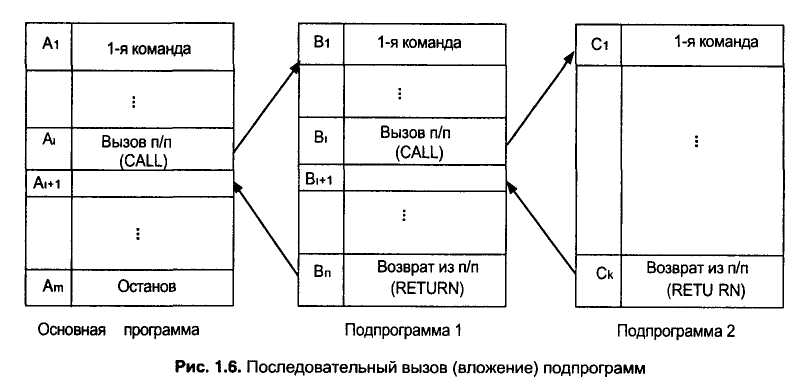

Особенность этой процедуры состоит в том, что большинство микропроцессоров обеспечивают возможности вложения подпрограмм, т. е. реализуют при выполнении подпрограммы вызов новой подпрограммы с последующим возвращением к предыдущей подпрограмме (рисунок8.1.6.1). При вложении нескольких подпрограмм требуется сохранение нескольких промежуточных значений содержимого PC и последовательная загрузка этих значений в PC при возврате к предыдущим подпрограммам и к основной программе.

Для реализации этой процедуры используется стек – специальная память магазинного типа, работающая по принципу «последний пришел – первый ушел» (стек типа LIFO – «Last In-First Out»). Существуют различные варианты реализации стека.

Рисунок8.1.6.1 Организация вложенных подпрограмм

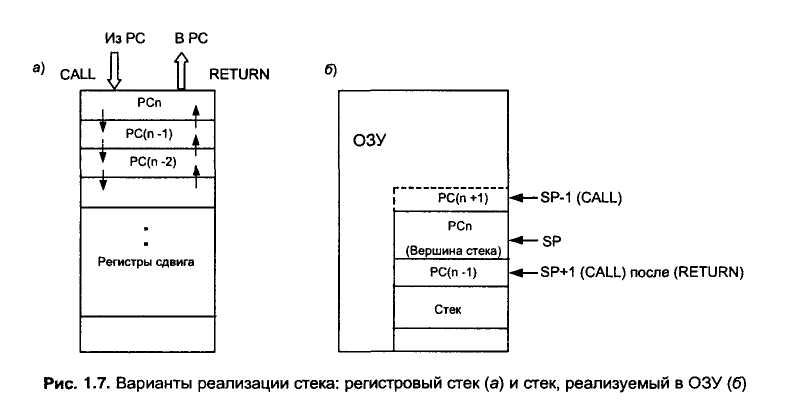

Регистровый стек (рисунок8.1.6.2, а) реализуется с помощью реверсивных сдвиговых регистров. Каждая команда CALL вызывает ввод в стек очередного содержимого PC. По команде RETURN направление сдвига изменяется и производится извлечение из стека последнего поступившего содержимого PC. Таким образом, обеспечивается выполнение вложенных подпрограмм. Возможное число вложенных подпрограмм определяется глубиной стека, т. е. разрядностью используемых регистров сдвига. Если число вложений превышает глубину стека, первые из введенных в стек значений PC теряются, т. е. возврат к основной программе не будет обеспечен. Поэтому при использовании регистрового стека необходим строгий контроль за числом вложений. Такая реализация стека применяется в системах, решающих задачи с ограниченным числом вложенных подпрограмм (обычно не более 10-20).

Значительно более широкие возможности вложения подпрограмм обеспечивает реализация стека в ОЗУ (рисунок8.1.6.2, б). В этом случае часть ОЗУ выделяется для работы в качестве стека. Адресация к ячейкам стека производится с помощью специального регистра – указателя стека SP (Stack Pointer), который вводится в состав УУ процессора. Регистр SP содержит адрес верхней заполненной ячейки стека, в которой хранится значение PC, записанное при выполнении команды CALL. При поступлении новой команды CALL содержимое SP авоматически уменьшается на 1, адресуя следующую, еще незаполненную ячейку стека Полученный адрес SP-1 выдается на шину А, а на шину D поступает содержимое PC, которое должно сохраняться в стеке. Таким образом, производится последовательное заполнение ячеек стека «снизу-вверх», при этом SP всегда адресует вершину стека. По команде RETURN текущее содержимое SP выдается на шину А, и по шине D производится считывание с вершины стека последнего записанного значения PC. После этого содержимое SP увеличивается на 1, адресуя предыдущее значение PC, хранящееся в стеке. Так как ОЗУ обычно имеет значительный объем, то для размещения стека можно выделить достаточно большое количество ячеек памяти, обеспечивая необходимый уровень вложения подпрограмм.

Рисунок8.1.6.2 Варианты реализации стека: регистровый стек (а) и стек, реализуемый в ОЗУ (б).

8.1.7 Функционирование МПС при обслуживании прерываний и исключений

При работе микропроцессорной системы часто возникают ситуации, когда требуется прервать выполнение текущей программы и перейти к подпрограмме, обеспечивающей необходимую реакцию системы на создавшиеся обстоятельства. Такие ситуации называются прерываниями или исключениями в зависимости от причин, вызывающих их возникновение.

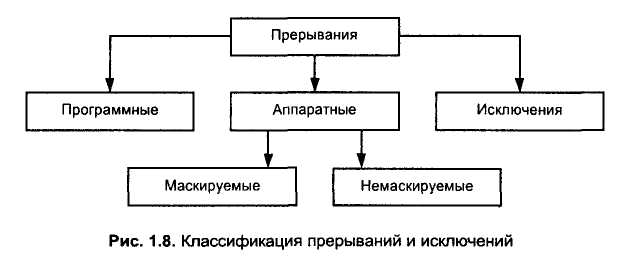

Прерываниями (interruption) являются ситуации, возникающие при поступлении соответствующих команд (программные прерывания) или сигналов от внешних устройств (аппаратные прерывания). Исключениями (exception) являются нештатные ситуации (ошибки), возникающие при работе процессора. При выявлении таких ошибок соответствующие блоки, контролирующие работу процессора, вырабатывают внутренние сигналы запроса, обеспечивающие вызов необходимой подпрограммы обслуживания. Классификация прерываний и исключений приведена на рисунке 8.1.7.1.

Рисунок 8.1.7.1. Классификация прерываний и исключений

Во всех этих ситуациях микропроцессор завершает выполнение очередной команды и заносит в стек текущее содержимое программного счетчика PC, которое является адресом возврата к прерванной программе после реализации подпрограммы обслуживания, и содержимое регистра состояний SR. Если запрос прерывания поступает от внешнего устройства, то процессор формирует сигнал подтверждения прерывания, который информирует это устройство, что начато обслуживание данного запроса. Затем в PC загружается из памяти вектор прерывания Ve – начальный адрес соответствующей подпрограммы обслуживания. Эти вектора являются входами в подпрограммы обслуживания и хранятся в таблице векторов прерываний, которая обычно записывается в ОЗУ. Размер таблицы зависит от числа типов обслуживаемых прерываний и исключений. В простейших микропроцессорах это число составляет несколько единиц, а для микропроцессоров семейства Pentium или MC68000 обеспечивается возможность реализации до 256 различных подпрограмм обслуживания.

Завершается подпрограмма обслуживания специальной командой возврата из прерывания IRET, которая выбирает из стека хранившееся содержимое PC и SR и загружает его обратно в эти регистры, обеспечивая возвращение к выполнению прерванной программы.

Программные прерывания реализуются при поступлении специальных команд (INTn, INT3, INTO для микропроцессоров Pentium). Эти команды вызывают переход к выполнению стандартных подпрограмм обслуживания, для размещения которых выделяются определенные позиции в ОЗУ. Таким образом, при вызове подпрограмм обслуживания реализуется обращение к фиксированным адресам.

Причинами аппаратных прерываний являются запросы от различных внешних (периферийных) устройств системы. Эти запросы поступают на внешние выводы микропроцессора или формируются периферийными устройствами, размещенными на одном кристалле с процессором. Аппаратные прерывания могут быть маскируемые или немаскируемые.

Запросы маскируемых прерываний обслуживаются только в том случае, если соответствующий бит управления I в регистре состояния SR, который называется маской прерываний, имеет значение 1. В процессорах Pentium это бит IF в регистре EFLAGS. С помощью специальных команд значение этого бита может быть установлено в 1 или сброшено в 0. Таким образом, можно разрешить или запретить обслуживание поступивших аппаратных прерываний при выполнении определенных программ или их фрагментов. При одновременном поступлении нескольких запросов обслуживание реализуется в соответствии с их приоритетом. В ряде микропроцессорных систем для обеспечения приоритетного обслуживания запросов от многих внешних устройств включаются специальные микросхемы – контроллеры прерываний. Некоторые типы микропроцессоров имеют внутренние контроллеры для организации приоритетных прерываний.

Немаскируемые запросы прерывания обслуживаются в первоочередном порядке и не могут быть маскированы. Обычно микропроцессор имеет один вход для подачи немаскируемых запросов, которые формируются при возникновении каких-либо аварийных ситуаций. Чаще всего этот вход используется для контроля напряжения питания. Если напряжение питания выходит за допустимые пределы, то специальный датчик вырабатывает немаскируемый запрос прерывания, поступающий в микропроцессор. При этом источник питания должен некоторое время (порядка 10 мс) сохранять необходимый уровень напряжения питания, в течение которого микропроцессор выполняет подпрограмму перезаписи на магнитный диск информации, достаточной для продолжения прерванной программы после восстановления нормального режима питания.

Для передачи сигналов запроса и подтверждения прерывания между микропроцессором и внешними устройствами или контроллером прерываний используются соответствующие линии шины управления С.

Причинами исключений могут быть различные ошибки и нештатные ситуации, возникающие при работе системы. Различные типы микропроцессоров контролируют разные варианты такого рода ситуаций. Типичными причинами исключений являются, например, использование нулевого делителя при выполнении команды деления (деление на 0), выборка неправильного кода команды, выход за границы разрешенного фрагмента памяти; поступление команд, выполнение которых запрещено при данном режиме функционирования микропроцессора и ряд других.

8.1.8 Функционирование МПС в режиме прямого доступа к памяти

Режим прямого доступа к памяти DMA (Direct Memory Access) используется, если необходимо произвести пересылку значительного массива информации между ОЗУ и каким-либо внешним устройством, которое подает в систему соответствующий запрос. Реализация такой пересылки с помощью соответствующей программы обмена требует выполнения отдельной команды пересылки для передачи каждого байта или слова. При этом необходим определенный объем памяти для хранения программы и требуется значительное время для ее выполнения.

В большинстве современных микропроцессорных систем пересылка массивов информации обеспечивается с помощью специальных устройств - контроллеров DMA, которые реализуют режим прямого доступа к памяти. При поступлении запроса от внешнего устройства контроллер выдает соответствующий сигнал микропроцессору. Получив этот сигнал, микропроцессор завершает очередной цикл обмена по системной шине и отключается от нее, то есть переводит свои выводы, подключенные к шинам A, D и линиям управления ОЗУ и внешними устройствами, в отключенное (высокоимпедансное) состояние. При этом микропроцессор выдает контроллеру DMA сигнал разрешения на реализацию прямого доступа. Получив этот сигнал, контроллер принимает на себя управление системой. Он выдает на шину А адреса ячеек ОЗУ, с которыми выполняется текущий цикл обмена, формирует необходимые сигналы, определяющие режим работы ОЗУ (запись или считывание) и интерфейсного устройства, через которое производится пересылка информации (ввод или вывод).

Передача сигналов запроса и подтверждения прямого доступа к памяти между микропроцессором и контроллером DMA производится по соответствующим линиям шины управления С.

Предварительно контроллер DMA программируется для выполнения указанных функций. В него вводятся начальные адреса массивов памяти в ОЗУ, с которых начинается процесс обмена, и размеры массивов, подлежащего пересылке. Обычно контроллер DMA обслуживает запросы от нескольких внешних устройств, поэтому он программируется на реализацию определенного приоритета их обслуживания в случае одновременного поступления нескольких запросов. Программирование контроллера производится путем посылки ему необходимых управляющих сообщений. Эти сообщения обычно предварительно вводятся в контроллер от микропроцессора, когда он выполняет специальную программу инициализации контроллера DMA.