Асинхронные последовательные счетчики

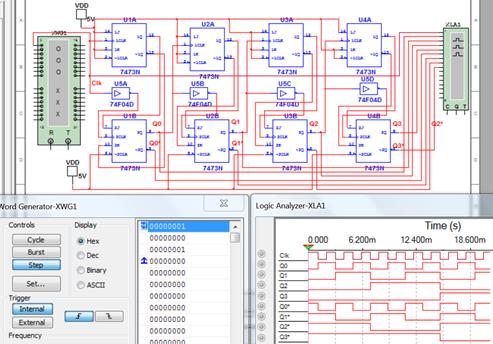

Асинхронные счетчики строятся в виде цепочки триггеров со счетным входом (Т- вход для Т – триггера; С – вход для JK - триггера при J=K=1; C – вход для D – триггера, при этом D вход соединен с инверсным выходом триггера). Счетный вход каждого последующего триггера счетчика подключается к выходу Q предыдущего или последующего триггера, что зависит как от направления счета, так и от фронта тактирующего входа, который переключает триггер счетчика в новое состояние. Основной недостаток последовательных счетчиков заключается в том, что из-за последовательного переключения триггеров, в счетчике возникает на короткие промежутки времени много других состояний. На рис.2.10.1. приведен асинхронный суммирующий счетчик, построенный на четырех двухтактных JK- триггерах и временная диаграмма его работы. Двухтактные триггеры построены на двух однотактных.

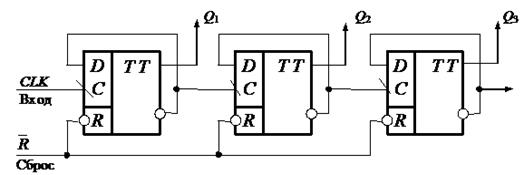

Рис.2.10 1. Схема и временные диаграммы работы асинхронного счетчика с последовательным переносом

Счетчик, изображенный на рис. 1 называют последовательным, так как каждый триггер переключается выходным сигналом предыдущего. Эти счетчики отличаются простой схемой, но недостатком является их низкое быстродействие в режиме регистрации выходных сигналов, так как в этом режиме нельзя подавать очередной входной сигнал, пока не зафиксировано предыдущее состояние счетчика. Время установления нового состояния счетчика равно tуст = nt зд. тр, где t зд. тр - время задержки переключения триггера. Очевидно, что максимальная частота входных сигналов в режиме регистрации составляет fмакс.рег=1/tуст. Каждый триггер счетчика делит частоту поступающих на его вход импульсов на 2. Можно установить любой коэффициент деления в счетчике, осуществляя его сброс при заданном количестве поступающих импульсов.

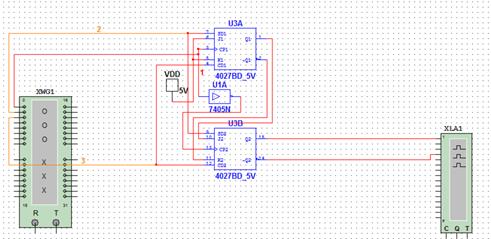

Построим двухтактный Т триггер со счетным входом на двух однотактных JK- триггерах (как на рис. 2.10.1) и создадим иерархический блок T-flip-flop (рис.2.10.2), который будет удобно использовать для построения счетчиков.

Рис. 2.10.2. Двухтактный Т-триггер

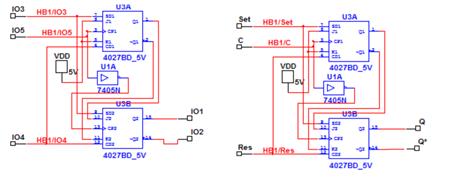

Перейдем к редактированию созданного блока, переименуем входы и выходы схемы (рис. 2.10.3).

Рис 2.10.3. Редактирование блока T-flip-flop

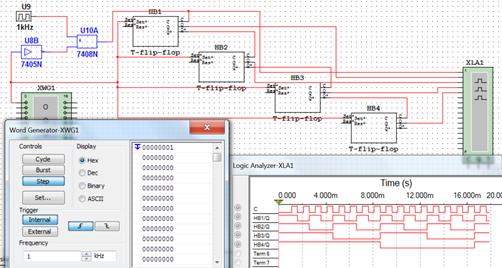

Построим последовательный вычитающий счетчик на созданных нами двухтактных Т-триггерах (рис. 2.10.4). Переключение каждого триггера осуществляется по спаду импульса синхронизации.

Рис 2.10.4. Последовательный вычитающий счетчик на двухтактных Т – триггерах со счетным входом

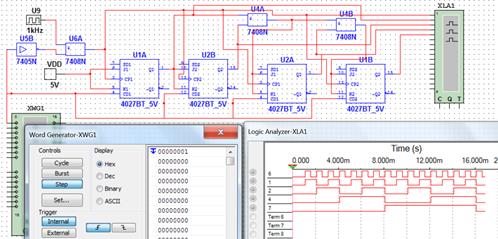

Счетные импульсы поступают с генератора U9. Для первоначальной установки всех триггеров счетчика в состояние 1 собрана схема, включающая инвертор U8, на который подается «1» на первом шаге моделирования.

Логический элемент «И» объединяет два сигнала: сигнал установки триггера и сигнал от генератора счетных импульсов. В начале моделирования следует установить курсор генератора слов на строку с нулевым адресом и осуществить установку триггера.

На рисунке 2.10.5 показанпоследовательный вычитающий счетчик на двухтактных D-триггерах

Рис. 2. 10. 5 Последовательный вычитающий счетчик на двухтактных D-триггерах

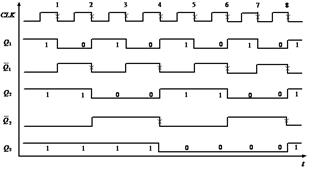

На рис. 2.10.6. показаны временные диаграммы работы вычитающего счетчика на двухтактных D-триггерах.

Рис. 2.10.6. Временная диаграмма работы асинхронного вычитающего счетчика на D- триггерах

Для устранения недостатков счетчика с последовательным переносом используют синхронные счетчики.

На рис. 2.10.7. показана схема синхронного счетчика с параллельным переносом и временные диаграммы его работы.

Рис. 2.10.7. Синхронный суммирующий, построенный на однотактных JK- триггерах и временная диаграмма его работы.

В схеме организован параллельный перенос. Переключение каждого последующего триггера осуществляется (по фронту счетных импульсов), если все предыдущие установлены в «1».

По сигналу синхронизации все триггеры переключаются одновременно, поэтому состояние триггера устанавливается за время переключения одного триггера.