Схемотехника интегральных операционных усилителей

Высокая точность выполнения той или иной функции устройством на основе ОУ определяется высоким входным сопротивлением, большим коэффициентом усиления, малым уровнем шумов, высокой степенью подавления синфазного сигнала, широкой полосой пропускания. Эти качества ОУ в значительной степени определяются свойствами его входного каскада. Поэтому в качестве входных каскадов всех ОУ используются дифференциальные усилители.

Повышение входного сопротивления и уменьшение входных токов ОУ достигаются тем, что транзисторы входного дифференциального каскада работают в режиме микроамперных токов эмиттера. Но при этом сужается полоса пропускания, что ухудшает усиление в области высоких частот. Для повышения коэффициента усиления применяются динамические нагрузки, а также используются каскадные схемы и составные транзисторы (схема Дарлингтона). С этой же целью во входных ДУ применяются супербета-транзисторы, у которых h21э ≥ 5000. При этом удается уменьшить входной ток ОУ до 1...2 нА. Еще меньший входной ток (т. е. более высокое входное сопротивление) можно получить при использовании во входном каскаде полевых транзисторов (до десятых долей наноампера).

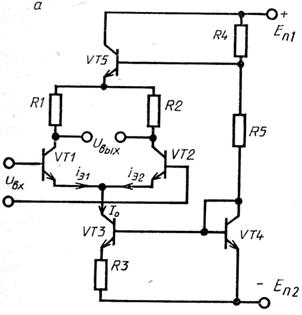

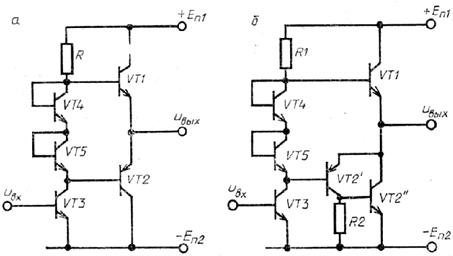

Одна из типовых и наиболее простых конструкций входного ДУ показана на рис. 7.15, а. Непосредственно

Рис. 7.15. Схемы входных каскадов интегральных ОУ

ДУ выполнен на биполярных транзисторах VT1 и VT2. На БТ VT3 и VT4 выполнен ГСТ по схеме отражателя тока. При токе I0 = 20...40 мкА эмиттерные токи транзисторов VT1 и VT2 составляют 10...20 мкА. Малые значения токов транзисторов VT1 и VT2 требуют принятия специальных мер для уменьшения потенциалов их коллекторов при наличии резисторов с не очень большими сопротивлениями R1 и R2. Это достигается включением в коллекторные цепи транзисторов VT1 и VT2 дополнительного транзистора VT5. Режим работы этого транзистора и напряжение Uкэ определяются делителем, состоящим из R4, R5 и VT4.

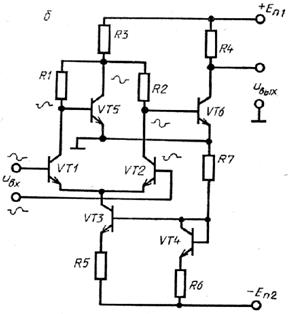

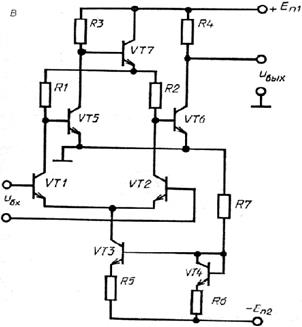

Рассмотренный ДУ позволяет получить Ky u = 30...100, поэтому после него необходимо включить еще один усилительный каскад. Если вход второго каскада симметричный, то подключение его к симметричному выходу входного ДУ позволяет полностью использовать усилительные свойства входного каскада. В то же время второй каскад должен иметь несимметричный выход, выполненный таким образом, чтобы не происходило потери усиления. Схема усилителя, отвечающего этим требованиям, приведена на рис. 7.15, б. Он отличается от ранее рассмотренного наличием двух дополнительных инвертирующих усилителей, выполненных на транзисторах VT5 и VT6 с нагрузками R3 и R4 соответственно. Напряжение, снимаемое с коллектора VT1, инвертируется первым усилителем и с коллектора VT5 через резистор R2 подается на базу транзистора VT6 в фазе с напряжением, снимаемым с коллектора VT2. Благодаря этому на базу VT6 поступает полный усиленный дифференциальный сигнал, который после дополнительного усиления выдается на несимметричный выход. Через резистор R3 протекают коллекторные токи трех транзисторов — VT1, VT2 и VT5, поэтому его сопротивление невелико. Это снижает общий коэффициент усиления дифференциального сигнала и коэффициент ослабления синфазного сигнала. Для устранения указанных недостатков резистор R3 включается в коллекторную цепь только усилителя на транзисторе VT5, а резисторы R1 и R2 подключаются к выходу эмиттерного повторителя на транзисторе VT7, как показано на рис. 7.15, в.

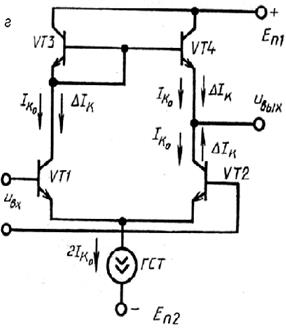

Для увеличения коэффициента усиления дифференциального и коэффициента подавления синфазного сигналов во входных ДУ широко используются динамические, или активные, нагрузки. Пример построения ДУ с динамической нагрузкой дан на рис. 7.15, г. Непосредственно ДУ выполнен на транзисторах VT1 и VT2, коллекторными нагрузками которых являются ветви токового зеркала, выполненного на транзисторах VT3 и VT4. В режиме покоя через транзисторы VT1 и VT2 и ветви токового зеркала протекают одинаковые коллекторные токи iк1, = iк2 = = iк0. При поступлении на базы транзисторов VT1 и VT2 дифференциальных сигналов коллекторные токи этих транзисторов принимают значения iк1 = Iк0 + ΔIк и iк2 = Iк0 – ΔIк. Поскольку токи левой и правой ветвей токового зеркала должны быть одинаковыми, то через нагрузку, подключаемую к выходу ДУ, должен протекать ток 2ΔIк, равный сумме приращений токов левого и правого плеч ДУ. В таком ДУ переход от симметричного входа к несимметричному выходу происходит с сохранением полного дифференциального сигнала.

Непосредственная связь между каскадами в многокаскадных усилителях приводит к тому, что все каскады оказываются связанными по постоянному току и напряжению. При последовательном включении нескольких каскадов уровень выходного напряжения нарастает от каскада к каскаду, приближаясь к уровню напряжения источника питания. Это ограничивает рабочую область последних каскадов, уменьшает их коэффициент усиления и вызывает искажение сигнала вследствие амплитудного ограничения в последних каскадах. Для исключения этого явления в многокаскадных усилителях применяются схемы сдвига уровней напряжения, а питание ИМС осуществляется от двухполярных источников. Это позволяет обеспечить нулевые потенциалы на входе первого и выходе последнего каскадов.

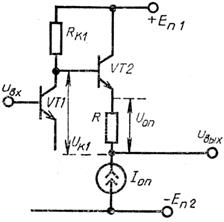

В качестве каскада сдвига уровня часто применяют эмиттер-ный повторитель с ГСТ в цепи эмиттера (рис. 7.16).

Рис. 7.16. Схема каскада сдвига уровня напряжения

Для получения Uвых = 0 должно быть выполнено условие

.

.

Благодаря высокому динамическому сопротивлению ГСТ уменьшение коэффициента усиления в таком каскаде, вызываемое падением части выходного напряжения на резисторе R,мало.

Выходной каскад не должен снижать усиления, достигнутого во входном и промежуточном каскадах, и в связи с этим должен обладать высоким входным сопротивлением. Необходимо также, чтобы выходной каскад не ухудшал частотных свойств ОУ и был экономичным.

Наиболее распространенными выходными каскадами ОУ являются разновидности эмиттерных повторителей, приспособленные для удовлетворения вышеперечисленных требований.

Основная (однотактная) схема эмиттерпого повторителя удовлетворяет многим требованиям, предъявляемым к выходным каскадам, но потребляет повышенный ток покоя и не имеет защиты транзистора при коротком замыкании в нагрузке.

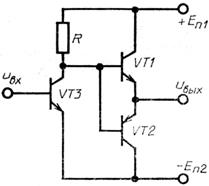

Для уменьшения потребляемой и рассеиваемой мощности в большинстве ОУ применяются двухтактные каскады, работающие в режиме В (рис. 7.17) или АВ (рис. 7.18, а).

Интегральные р — п — р-транзисторы обладают меньшим значением коэффициента h21э и худшими частотными свойствами

Рис. 7.17. Схема двухтактного выходного каскада

Рис. 7.18. Схемы двухтактных выходных каскадов с повышенной линейностью

по сравнению с п — р— n-транзисторами. Это приводит к увеличению нелинейных искажений выходного напряжения. Для исключения такого нежелательного явления в качестве р — п — р-транзистора применяют составной транзистор (VT2' и VT2" на рис. 7.18, б).

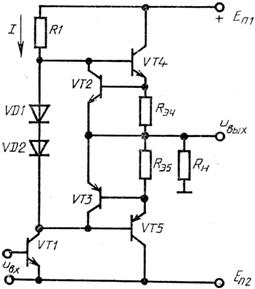

Недостатком рассмотренных двухтактных схем является отсутствие защиты от короткого замыкания в нагрузке. Для защиты транзисторов выходного каскада от перегрузок по току, т. е. предотвращения выхода транзисторов из строя, который может произойти при увеличении тока в нагрузке, схема выходного каскада строится так. как показано на рис. 7.19. При коротком замыкании в нагрузке произойдет увеличение тока, протекающего через транзистор VT4 или VT5, в зависимости от полярности входного напряжения. При этом увеличится падение напряжения соответственно на резисторе Rэ4или Rэ5,

Рис. 7.19. Схема выходного каскада интегрального ОУ с защитой выходных

транзисторов от перегрузок по току

и транзистор VT2 (или VT3)окажется в режиме насыщения. Увеличение коллекторных токов этих транзисторов приведет к уменьшению токов баз транзисторов VT4 и VT5, в результате уменьшатся их коллекторные и эмиттерные токи и будет предотвращен выход транзисторов VT4 и VT5 из строя вследствие перегрева.

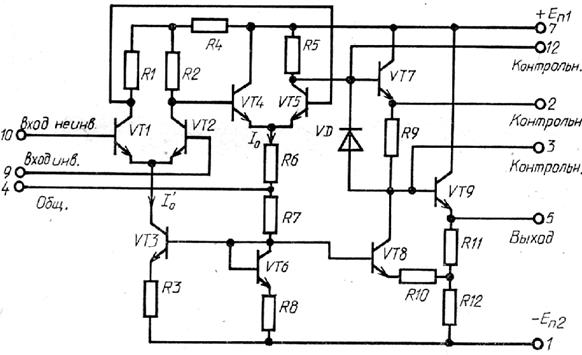

На рис. 7.20 показана принципиальная схема ОУ типа К140УД1. На транзисторах VT1 и VT2 выполнен входной ДУ. Усилительный каскад на транзисторах VT4 и VT5 обеспечивает переход от симметричного выхода к несимметричному. В эмиттерные цепи первого и второго каскадов включены большие динамические нагрузки, которые образованы ГСТ, выполненными на диодно-тран-зисторных структурах VT3 и VT6. Ток I0` ГСТ первого

Рис. 7.20. Схема интегрального ОУ К140УД1

каскада задается нелинейным делителем R6R7VT6R8,обладающим термостабилизирующими свойствами.

Усиленное напряжение с коллектора транзистора VT5 поступает на базу транзистора VT7, на котором выполнен каскад сдвига уровня, представляющий собой эмиттерный повторитель с ГСТ на транзисторе VT8.

Напряжение с динамической нагрузки каскада сдвига уровня (коллектора VT8)поступает на базу транзистора VT9, образующего с резисторами R11, R12 и R10 выходной эмиттерный повторитель. Чтобы компенсировать ослабление напряжения, усиливаемого каскадом сдвига уровня, в выходной эмиттерный повторитель введена цепь ПОС, позволяющая получить коэффициент передачи этого повторителя, больший единицы (примерно 1,5). Действие ПОС проявляется следующим образом.

Часть выходного напряжения, снимаемая с резистора R12, через резистор R10 подается в эмиттерную цепь транзистора VT8. По отношению к этому напряжению транзистор VT8 образует усилитель с ОБ. Так как усилитель с ОБ входной сигнал не инвертирует, то в его коллекторной цепи создается дополнительное напряжение, совпадающее по фазе с основным напряжением. Благодаря этому на базе транзистора VT9 и на его эмиттере создается напряжение, которое несколько превышает напряжение, снимаемое с коллектора VT5.

Диод VD, работающий при обратном смещении, используется в качестве конденсатора, обеспечивающего дополнительный фазовый сдвиг в целях повышения устойчивости ОУ.

Рассмотренный операционный усилитель относится к ОУ первого поколения. . Для его питания требуется двухполярный источник питания с напряжениями ±6,3 В (К140УД1А) и ±12,6 В (К140УД1Б). Основные параметры ОУ типа К140УД1Б: Uсм= ±7мВ; Iвх≤9мкА; ΔIвх≤ ±2,5мкА; Куи = 1350...8000; f1≥5 МГц; tу≤1,5 мкс; Uвх max= ±1,2 В.