Параллельно-последовательные и реверсивные регистры.

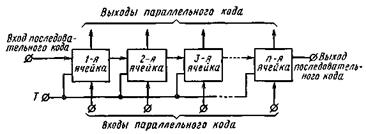

В параллельно-последовательных регистрах (рис.4.5) сочетаются свойства регистров параллельного и последовательного действия. Они позволяют осуществлять запись информации как в последовательном, так и параллельном коде, в связи с чем могут быть использованы для преобразования кодов из последовательного в параллельный и обратно. Эти регистры допускают однотактный и многотактный принципы построения. Для преобразования последовательного кода в параллельный серией тактовых импульсов в регистр записывается информация (число) последовательного кода. Выходы разрядов регистра при этом представляют ту же информацию в параллельном коде. Для обратного преобразования информация в регистр вводится по входам параллельного кода. Посредством серии тактовых импульсов с выхода последнего разряда регистра информация считывается в последовательном коде.

|

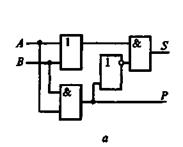

Рис.4.5. Структурная схема параллельно-последовательных регистров

Реверсивные регистры предназначены для осуществления сдвига кода числа в сторону как старшего, так и младшего разрядов. Регистр содержит связи последовательной передачи информации в направлении от младших разрядов к старшим, а также от старших разрядов к младшим. Прямой или обратный сдвиг кода осуществляют управляющим сигналом, вводящим в действие либо прямую, либо обратную связи между разрядами.

§4.2. Коммутаторы: мультиплексоры, распределители

Существует два вида коммутаторов: мультиплексоры и демуль-типлексоры (распределители).

Мультиплексор — коммутатор с одного из нескольких информационных входов на единственный выход. Выбор того или иного входа определяется кодом, устанавливаемым на адресных входах мультиплексора. Это позволяет при смене кодов передавать на выход цифровую информацию то с одного, то с другого входного канала.

Распределитель — это устройство, передающее импульс, поступивший на его вход, на один из выходов в зависимости от управляющего сигнала, заданного двоичным кодом. Распределитель — коммутатор единственного информационного входа на один из нескольких выходов.

Выбор того или иного выхода определяете кодом на адресных входах распределителя. Таким образом, распределитель решает задачу, обратную мультиплексору: при смене кодов он может передавать цифровую информацию то в один, то в другой канал с одного входа.

Распределители.

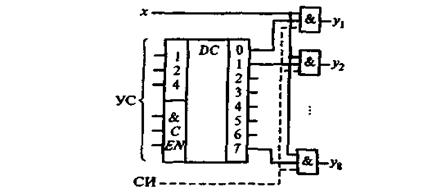

Распределитель выполняется на основе дешифратора (рис.4.6). Управляющий сигнал УС в виде параллельного двоичного кода подается на входы дешифратора, выходы которого соединены со средними входами конъюнкторов, составляющих выходную часть схемы.

Рис.4.6. Распределитель на восемь выходов

На входах С и EN поддерживается логическая «1». На верхние входы конъюнкторов поступает входной импульс, который пройдет лишь через тот конъюнктор, на который от дешифратора подается разрешающий единичный сигнал. Пусть, например, единичный сигнал поддерживается на выходе 0 дешифратора. Тогда импульсы линии х будут передаваться через верхний конъюнктор на выход у1. Если управляющий код изменится, и единичный сигнал появится, например, на выходе 7 дешифратора, то входные импульсы х будут передаваться через нижний конъюнктор на выход 8 распределителя.

Такой распределитель может быть выполнен синхронным. Для этого могут быть использованы либо входы С и EN дешифратора, либо третьи (на рис.7 — нижние) входы конъюнкторов, на которые подаются сигналы синхронизации СИ.

Мультиплексоры.

Мультиплексор — это устройство, подключающее единственный выходной канал к одному из входов в зависимости от управляющего сигнала, заданного двоичным кодом. Мультиплексор решает задачу, обратную распределителю. Иными словами, мультиплексор позволяет производить прием сигналов с различных направлений. Разрядность n управляющего сигнала определяет количество входов 2n, с которых мультиплексор позволяет осуществлять прием информации.

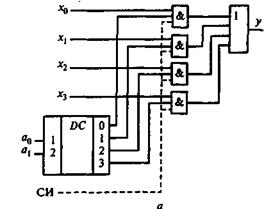

На рис.7, а приведена функциональная схема мультиплексора на четыре входа х0-х3, управляемая двухразрядным кодом a0a1 — адресом выбираемого входа.

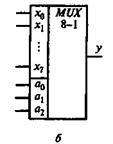

Управляющий сигнал, распознаваемый дешифратором, формирует единичный сигнал на одном из его выходов, который, поступая на нижний вход одной из схем И, пропускает на выход у (через дизъюнктор ИЛИ) импульсы с той входной линии, которая подключена к верхнему входу данной схемы И. Мультиплексор может быть синхронизирован подачей на конъюнкторы синхроимпульсов, как показано пунктиром на рис.4.7,а. Условное обозначение мультиплексора на восемь входов приведено на рис.4.7,б.

Рис.4.7. Мультиплексор: а - функциональная схема; б - условное обозначение

§4.3. Сумматоры: одноразрядные, многоразрядные: параллельные

И последовательные

Общие сведения.

Основным действием над двоичными числами является сложение. Оно используется само по себе, в операциях вычитания, а также составляет основу умножения и деления чисел. Многоразрядные сумматоры организуются на одноразрядных, суммирующих одноименные разряды чисел.

По принципу обработки разрядов чисел различают последовательные и параллельные сумматоры. В последовательных сумматорах сложение чисел осуществляется поразрядно, последовательно; в параллельных — все разряды обрабатываются одновременно, параллельно. Классификация сумматоров, описанных в данной главе, приведена на рис.4.8.

Одноразрядный сумматор.

Сложение одноразрядных двоичных чисел осуществляется по следующим правилам сложения чисел в двоичной системе.

Рис.4.8. Классификация сумматоров

В таблице истинности (табл.4.1) приведены все случаи сложения одноразрядных двоичных чисел A и В. По таблице можно установить следующие логические выражения, связывающие выходы S (цифра в данном разряде) и Р (единица переноса в следующий разряд) с входами А и B:

; (4.1)

; (4.1)

Р=AВ. (4.2)

Таблица 4.1

Таблица истинности сложения двух чисел

| Слагаемое | Результат в данном разряде (S) | Перенос в следующий разряд(P) | ||||||

| А | В | |||||||

Формула (4.1) представляет собой выражение неравнозначности (функция исключающее ИЛИ), которая обозначена значком  , а формула (4.2) — конъюнкция одноразрядных чисел А и В. По этим выражениям может быть синтезирован полусумматор — устройство, реализующее сложение двух одноразрядных чисел. В соответствии с выражениями (4.1), (4.2) схема полусумматора содержит шесть элементов. Для ее минимизации прибавим к функции S слагаемые

, а формула (4.2) — конъюнкция одноразрядных чисел А и В. По этим выражениям может быть синтезирован полусумматор — устройство, реализующее сложение двух одноразрядных чисел. В соответствии с выражениями (4.1), (4.2) схема полусумматора содержит шесть элементов. Для ее минимизации прибавим к функции S слагаемые  и

и  , каждое из которых равно 0. При этом

, каждое из которых равно 0. При этом

.

.

По теореме де Моргана  . Но АВ=Р, поэтому

. Но АВ=Р, поэтому  .

.

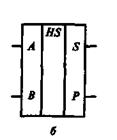

Выражения  и Р=AВ реализует схема, представленная на рис.4.9,а. В нее входит на два элемента меньше, чем в схему, составленную непосредственно по выражениям (4.1), (4.2). Условное изображение полусумматора приведено на рис.4.9,б.

и Р=AВ реализует схема, представленная на рис.4.9,а. В нее входит на два элемента меньше, чем в схему, составленную непосредственно по выражениям (4.1), (4.2). Условное изображение полусумматора приведено на рис.4.9,б.

Рис.4.9. Полусумматор: а) – схема; б) – условное графическое изображение

Полусумматор не имеет входа, на который можно было бы передавать перенос с предыдущего разряда, поэтому его можно использовать только для суммирования младших разрядов чисел.

Многоразрядный сумматор.

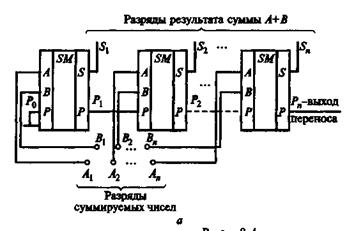

Суммирование одноименных разрядов многоразрядных чисел может осуществляться параллельно и: последовательно. Сумматор параллельного действия (рис.4.10,а) состоит из полных одноразрядных сумматоров, количество которых равно числу разрядов складываемых чисел.

Ввод слагаемых чисел и вывод результата осуществляется всеми разрядами одновременно в параллельной форме. Перенос с выхода сумматора одного разряда передается на вход переноса сумматора следующего разряда. Поэтому быстродействие сумматора определяется временем распространения сигнала переноса вдоль цепи одноразрядных сумматоров. Для повышения быстродействия используют, в частности, параллельное формирование переносов в специальном блоке ускоренного переноса. Условное изображение многоразрядного сумматора приведено на рис.4.10,б.

Рис.4.10. Параллельный сумматор (а), его графическое

условное обозначение (б)

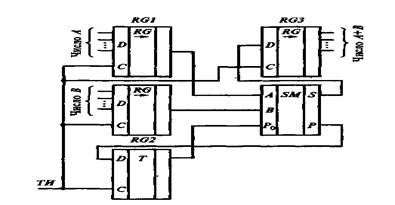

При последовательном суммировании каждое число представляется в последовательной форме, и одноименные разряды чисел, начиная с младших, синхронно вводятся в полный одноразрядный сумматор. По тактовым импульсам ТИ (рис.4.11) из сдвигающих регистров RG1 и RG2 на входы А и В сумматора попарно последовательно поступают разряды чисел. С выхода Р сигнал переноса запоминается в триггере и задерживается на входе Р0 до поступления следующей пары разрядов, с которой он складывается. Затем новый сигнал переноса заносится в триггер. Тактовыми импульсами ТИ разряды суммы последовательно вдвигаются в регистр RG3 по входу D, на выходах регистра результат А+В представляется в параллельной форме. Так как до суммирования Р=0, то суммирование следует начинать с младших разрядов, сумма которых определяется только их значениями. Достоинством сумматора последовательного действия является простота схемы, а недостатком — сравнительно низкое быстродействие.

Рис.4.11. Последовательный сумматор

Цифровые компараторы.

Цифровой компаратор предназначен для сравнения двух двоичных чисел (компарировать — сравнивать). Он имеет две группы входов. На одну из них поступают разряды первого числа А, на другую группу — разряды второго числа В. Появление лог.1 на одном из трех выходов компаратора фиксирует результат сравнения. На одном выходе она устанавливается при равенстве чисел (А=В), на другом — при А>В, на третьем — при А<В.

Сравнение одноразрядных чисел на равенство может осуществлять элемент «Равнозначность», а на неравенство — элемент «Неравнозначность». Для сравнения многоразрядных чисел они дополняются элементами других типов.

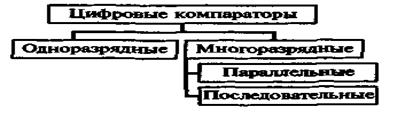

Цифровой компаратор можно использовать, например, в системах автоматического контроля и регулирования. При этом число А является параметром некоторого процесса, а число В — порогом (уставкой), которого (в соответствии с условиями задачи) этот параметр не должен превосходить или опускаться ниже его. На рис.4.12 приведена классификация цифровых компараторов. Наряду с цифровыми существуют и аналоговые компараторы.

Рис.4.12. Классификация компараторов

Структура компаратора.

В табл.4.2 показана связь между сигналами на выходах и входах компаратора при сравнении одноразрядных чисел а и в, которые могут быть равны единице или нулю. На соответствующем выходе появляется лог.1, когда в должном соотношении находятся коды на входах. Так, если а=1, b=1 (числа одинаковы), то функция, характеризующая равенство чисел, Fa=b=1, а функции, характеризующие их неравенство, Fa>b=0 и Fa<b=0.

Таблица 4.2

Связь между входными и выходными сигналами компаратора

| Входы | Выходы | |||

| A | B | Fa>b | Fa=b | Fa<b |

Аналогично заполняются другие строки таблицы. По правилам алгебры логики из табл.4.2 можно записать следующие логические функции, характеризующие соотношения одноразрядных чисел:

;

;  ;

;  .

.

Если значения а и b таковы, что правые части функций равны 1, то соотношения, указанные в индексах левых частей, выполняются. Если правые части функций равны 0, то соотношения между а и в противоположны указанным.

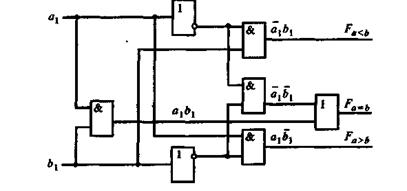

Схема одноразрядного компаратора, реализующая приведенные функции, изображена на рис.4.13.

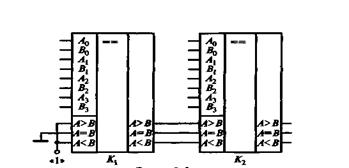

На рис.414 приведены условное обозначение компараторов и способ наращивания их разрядности. Каждый из изображенных компараторов предназначен для сравнения двух 4-разрядных слов и имеет выходы А>В, А=В и А<В. Аналогичные входы служат для наращивания разрядности компараторов. Результат сравнения младших разрядов отражается на выходах компаратора К1: на одном из них появляется единица, на других присутствуют нули.

Рис.4.13. Схема одноразрядного компаратора

Компаратор К2 воспринимает этот результат как единую пару младших разрядов, с учетом которой формируется окончательный результат сравнения. Подобным образом можно осуществлять дальнейшее наращивание разрядности. Указанные потенциалы на входах компаратора К1 младших разрядов обеспечивают правильное функционирование многокаскадного компаратора на данных микросхемах.

Рис.4.14. Условное обозначение компараторов и способ

наращивания их разрядности

Вопросы для самоконтроля

1. Приведите определения регистра.

2. Приведите классификацию регистров.

3. Расскажите об устройстве и принципе действия параллельного регистра. Приведите его условное графическое изображение.

4. Расскажите об устройстве и принципе действия последовательного регистра. Приведите его условное графическое изображение.

5. Расскажите об устройстве и принципе действия параллельно-последовательного и реверсивного регистра.

6. Дайте определение распределителя и мультиплексора и классификацию коммутаторов.

7. Расскажите об устройстве и принципе действия распределителя и мультиплексора. Приведите условное графическое изображение мультиплексора.

8. Дайте классификацию сумматоров и расскажите об их назначении.

9. Расскажите об устройстве и принципе действия одноразрядного сумматора.

10. Расскажите об устройстве и принципе действия многоразрядных сумматоров.

11. Расскажите о назначении компараторов и их классификацию.

12.. Расскажите об устройстве и принципе действия одноразрядного и много разрядного компараторов.