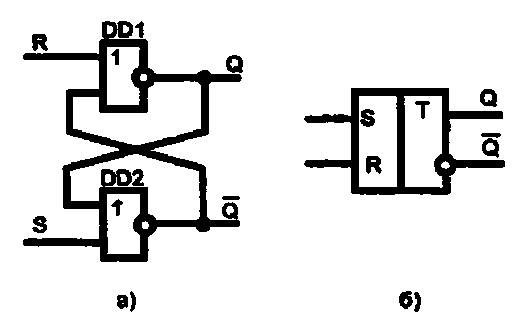

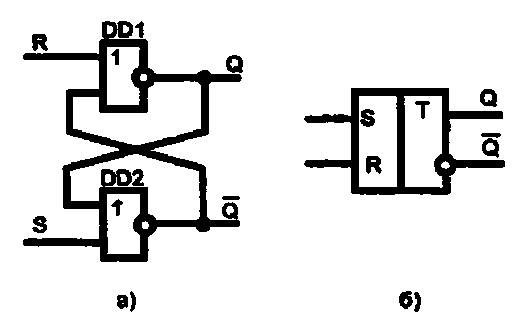

Асинхронный RS-триггер с прямыми входамина логических элементах 2ИЛИ-НЕ представлен на рисунке 1.

Рис.1.

Логические элементы ИЛИ-НЕ с инвертированием сигнала образуют петлю положительной обратной связи. При таком соединении логическая единица на выходе одного логического элемента (ЛЭ) поступает на вход другого ЛЭ и обеспечивает логический ноль (инвертирование) на его выходе. Логический ноль на выходе ЛЭ, поступая на вход другого, при инвертировании дает логическую 1. Таким образом, выходы Q и всегда находятся в противоположных состояниях. Соединение элементов по данной схеме позволяет получить цепь с двумя устойчивыми состояниями.

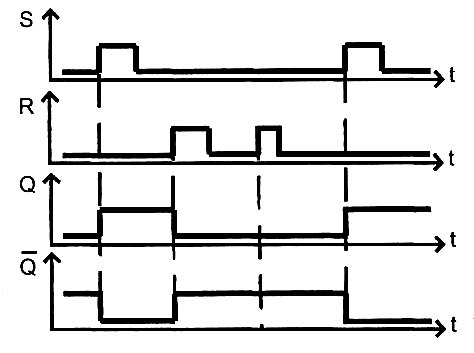

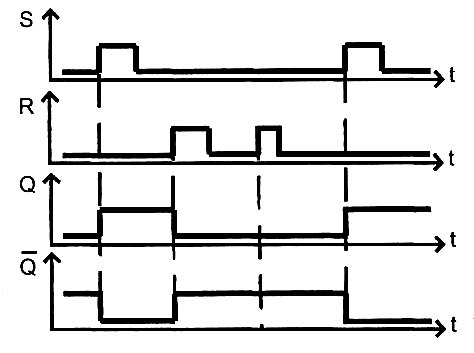

Временные диаграммы, характеризующие работу асинхронного RS-триггера с прямыми входами, показаны на рис. 2.

Рис.2

Для элементов ИЛИ-НЕ активным является высокий уровень — логическая 1, поэтому в режиме хранения данных на входы этого триггера подаются нулевые значения R=S=0. Установка триггера в нужное состояние производится подачей на соответствующий вход активного уровня единицы. Одновременная подача единицы на оба входа (RиS) приводит к неопределенности. На обоих выходахQ ипоявляются единицы, а после отключения входов (S=R=0) может установиться любое состояние. Такая ситуация неопределенности не допустима, поэтому комбинацияS=R=1 считается запрещенной.

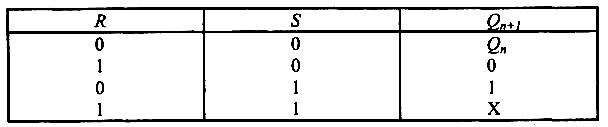

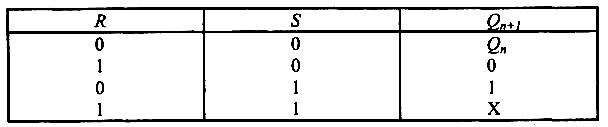

Функционирования триггера с прямыми входами на элементах 2ИЛИ-НЕ может быть отражено таблицей истинности

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

7. Назначение триггера

Триггерами называют большой класс электронных устройств, обладающих способностью длительно находиться в одном их двух или более устойчивых состояний и чередовать их под воздействием внешних сигналов.

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений). В соответствии с этим триггер имеет два состояния: одно из них обозначается как состояние лог. 0, другое - состояние лог. 1.

Воздействуя на входы триггера, его устанавливают в нужное состояние.

Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

Простейшая схема, позволяющая запоминать двоичную информацию, может быть построена на двух инверторах, охваченных положительной обратной связью. Эта схема приведена на рисунке 1.

Рисунок 1. Схема простейшего триггера, построенного на инверторах

В этой схеме может быть только два состояния - на выходе Q присутствует логическая единица и на выходе Q присутствует логический ноль. Если логическая единица присутствует на выходе Q, то на инверсном выходе будет присутствовать логический ноль, который после очередного инвертирования подтверждает уровень логической единицы на выходе Q. И наоборот, если на выходе Q присутствует логический ноль, то на инверсном выходе будет присутствовать логическая единица.

Такая ситуация будет сохраняться до тех пор пока включено питание. Но вот вопрос — а как записывать в такой триггер информацию? Нам потребуются входы записи нуля и записи единицы. Триггер с подобной возможностью получил название RS триггер.

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

8. Типы триггеров

Понятие «триггер» охватывает много устройств, которые существенно различаются между собой по выполняемым функциям, способам управления, по электрическим и конструктивным параметрам. Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации. Под памятью триггера подразумевают способность оставаться в одном из двух состояний после прекращения действия переключающего сигнала. Приняв одно из состояний за 1, а другое за 0, можно считать, что триггер хранит (помнит) один разряд числа, записанного в двоичном коде.

Триггеры подразделяются на две большие группы – динамические и статические. Названы они так по способу представления выходной информации. Динамические триггеры в настоящее время имеют ограниченное применение. К статическим триггерам относят устройства, каждое состояние которых характеризуется неизменными уровнями выходного напряжения (выходными потенциалами): высоким – близким к напряжению питания и низким – около нуля.

Статические (потенциальные) триггеры, в свою очередь, подразделяются на две неравные по практическому значению группы – симметричные и несимметричные триггеры. Оба класса реализуются на двухкаскадном усилителе с положительной обратной связью, а названием своим они обязаны способам организации внутренних электрических связей между элементами схемы.

Симметричные триггеры отличает симметрия схемы и по структуре, и по параметрам элементов обоих плеч. Для несимметричных триггеров характерна неидентичность параметров элементов отдельных каскадов, а также и связей между ними.

Симметричные статические триггеры составляют основную массу триггеров, используемых в современной радиоэлектронной аппаратуре, и именно они рассматриваются в данном разделе.

Классификация триггеров проводится по признакам логического функционирования и способу записи информации.

По логическому функционированию различают триггеры типов RS, D, T, JK и др. Кроме того, используются комбинированные триггеры, в которых совмещаются одновременно несколько типов, и триггеры со сложной входной логикой (группами входов, связанных между собой логическими зависимостями).

В комбинированных триггерах совмещаются несколько режимов. Например, триггер типа RST — счетный триггер, имеющий также входы установки сброса.

По способу записи информации различают асинхронные (нетактируемые) и синхронные (тактируемые) триггеры. Будет ли триггер синхронным или асинхронным, зависит от схемы управляющего устройства.

У асинхронных триггеров имеются только информационные (логические) входы. Асинхронные триггеры отличает свойство срабатывать сразу после изменения сигналов на входах, не считая короткого времени задержки распространения в элементах, образующих триггер.

У синхронных триггеров смены сигналов на информационных входах еще недостаточно для срабатывания. Необходим дополнительный командный импульс, который подается на синхронизирующий, или, как его чаще называют, тактирующий вход.

Синхронизирующие (тактирующие) сигналы вырабатываются специальным генератором тактовых импульсов, которые и задают частоту смены информации в дискретном времени t1, t2, …, tn-1, tn, tn+1. В эти моменты обновляется информация на выходах триггера, которая поступает на входы последующих устройств.

Синхронизация обеспечивает привязку ко времени и объединяет в общем ритме работу многих узлов аппаратуры, что позволяет во многих случаях ее существенно упростить.

Для асинхронного триггера тактом считается интервал времени между очередными сменами входных сигналов, причем длительность тактов не регламентируется. Асинхронные триггеры воспринимают непрерывный входной сигнал (1 или 0), независимо от его длительности, как один сигнал. В случае синхронного триггера входной сигнал неизменного уровня, длящийся n тактов, обрабатывается как последовательность нескольких n отдельных сигналов одного знака. Например, код 11001, поступающий последовательно на вход синхронного триггера, за счет тактирования будет так и воспринят. Этот же код на входах асинхронного триггера будет воспринят как 101, так как без временной привязки последовательность логических 1 или 0 не отличить от одиночных логических 1 и 0.

Синхронные триггеры, сравнительно с асинхронными, обладают также более высокой помехоустойчивостью. Опрокидывание синхронных триггеров происходит только при участии тактовых импульсов, длительность которых намного меньше периода следования. В остальное время входные сигналы, равно как и помехи различного происхождения, на триггер не влияют. В случае же асинхронного управления опрокидывание может произойти в любой момент времени, будь то полезный сигнал на входе или помеха.

По способу восприятия тактовых сигналов триггеры делятся на управляемые уровнем и управляемые фронтом. Управление уровнем означает, что при одном уровне тактового сигнала триггер воспринимает входные сигналы и реагирует на них, а при другом не воспринимает и остается в неизменном состоянии При управлении фронтом разрешение на переключение дается только в момент перепада тактового сигнала (на его фронте или спаде). В остальное время независимо от уровня тактового сигнала триггер не воспринимает входные сигналы и остается в неизменном состоянии. Триггеры, управляемые фронтом, называют также триггерами с динамическим управлением.

Динамический вход может быть прямым или инверсным. Прямое динамическое управление означает разрешение на переключение при изменении тактового сигнала с нулевого значения на единичное, инверсное – при изменении тактового сигнала с единичного значения на нулевое.

По характеру процесса переключения триггеры делятся на одноступенчатые и двухступенчатые.

В одноступенчатом триггере переключение в новое состояние происходит сразу, в двухступенчатом – по этапам. Двухступенчатые триггеры состоят из входной и выходной ступеней. Переход в новое состояние происходит в обеих ступенях поочередно. Один из уровней тактового сигнала разрешает прием информации во входную ступень при неизменном состоянии выходной ступени. Другой уровень тактового сигнала разрешает передачу нового состояния из входной ступени в выходную.

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

9. Назначение суммирующих, вычитающих и реверсивных счетчиков.

Счетчиком называется типовой узел ЭВМ, предназначенный для подсчета числа входных сигналов (импульсов). По целевому назначению счетчики подразделяются на суммирующие, вычитающие и реверсивные.

Суммирующий счетчик предназначен для выполнения счета импульсов в прямом направлении, т.е. для сложения. С приходом очередного импульса на вход счетчика его содержимое увеличивается на единицу.

Вычитающий счетчик предназначен для выполнения счета в обратном направлении, т.е. в режиме вычитания. Каждый импульс, поступающий на вход такого счетчика, уменьшает его содержимое на единицу.

Реверсивными называются такие счетчики, которые могут работать как в режиме сложения, так и в режиме вычитания.

По способу построения цепей сигналов переноса различают счетчики с одновременным, групповым, сквозным и последовательным переносами.

Основными характеристиками счетчиков являются:

1. Быстродействие, оцениваемое максимальной частотой поступления входных импульсов F=1/T , T – период следования счетных импульсов.

2. Модуль счета или коэффициент пересчета К.

Коэффициент пересчета К характеризует число устойчивых состояний счетчика, т.е. предельное число импульсов, которое может быть сосчитано счетчиком. Например, при К=12 счетчик будет иметь 12 состояний. И каждый двенадцатый импульс будет возвращать его в начальное состояние. Если счетчик имеет nразрядов, то K=2n. Каждому состоянию соответствует n разрядное двоичное число (от 0 до 2n-1), а всего таких чисел 2n.

При построении схем счетчиком могут быть использованы методы синтеза конечных автоматов, рассмотренные ранее.

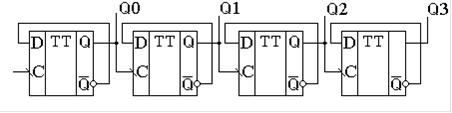

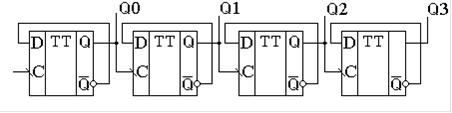

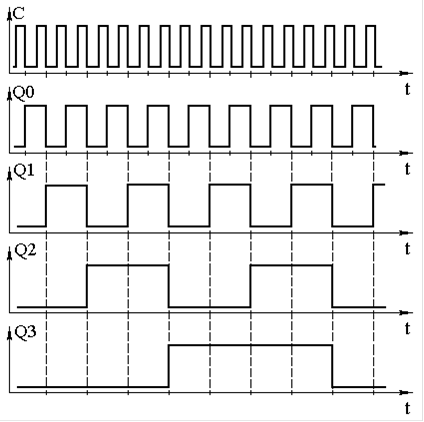

В простейшем случае двоичный счетчик может быть образован из асинхронных Т-триггеров, соединенных последовательно. При этом сигналы счета a поступают на вход Т-триггера младшего разряда счетчика. Прямой выход Q триггера каждого разряда соединен со входом Т соседнего триггера более старшего разряда. Поскольку в процессе счета переключение триггеров отдельных разрядов в этом счетчике осуществляется последовательно разряд за разрядом, такой счетчик носит название счетчика с последовательным переносом. Для ликвидации неустойчивых состояний используются двухступенчатые триггера. Схема счетчика имеет следующий вид:

Числа, формируемые счетчиком, могут быть выведены из него в параллельной форме посредством одновременного опроса состояния всех разрядов счетчика.

Счетчики обычно строятся на синхронных или асинхронных двухступенчатых Т-триггерах.

В асинхронном Т-триггере смена состояний происходит по заднему фронту входного сигнала, поскольку двухступенчатый триггер можно рассматривать как схему, состоящую из двух триггеров:

В синхронном триггере смена состояний происходит по заднему фронту синхроимпульсов С:

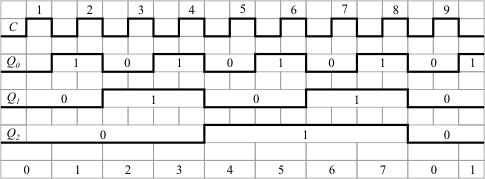

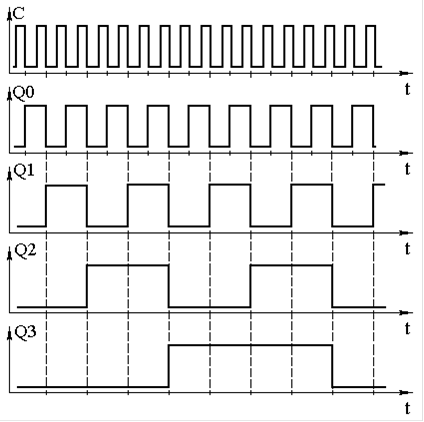

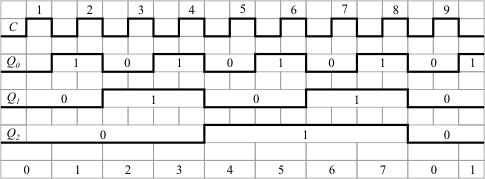

Временная диаграмма работ трех разрядного асинхронного суммирующего счетчика с последовательным переносом имеет вид.

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

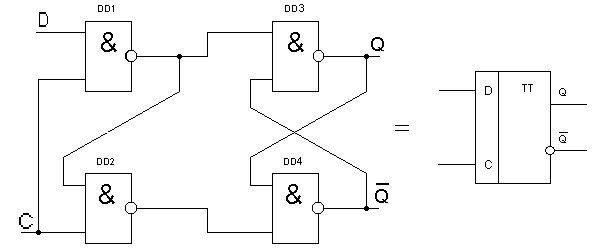

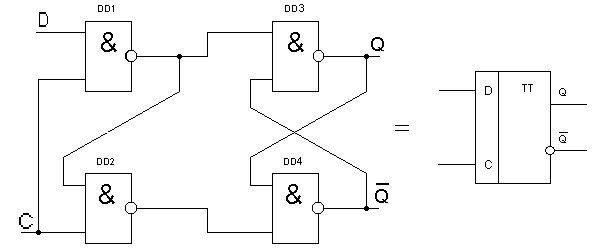

10. D триггер или триггер задержки

Триггер задержки, который используют для создания регистров сдвига и регистров хранения, неотъемлемая часть любого микропроцессора.

Рис. 1. Схема D-тригера

Имеет два входа – информационный и синхронизации. При состоянии С=0 тригер устойчив и при этом сигнал на выходе не зависит от сигналов, поступающих на информационный вход. При С=1 на прямом выходе информация будет точно повторять ту информацию, которая подается на вход D. На временной диаграмме приведен принцип работы D-триггера

Рис.2. D-триггер. а) схематическое изображение б) временная диаграмма работы

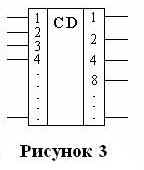

Рис. 3 Таблица истинности D-триггера:

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

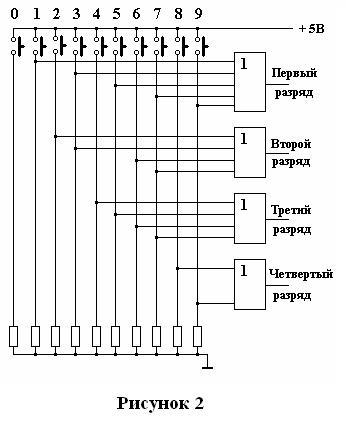

11. Шифратор. Назначение, применение.

Современный компьютер может обрабатывать, как мы уже знаем, числовую, текстовую, графическую и звуковую информацию.

Современный компьютер может обрабатывать, как мы уже знаем, числовую, текстовую, графическую и звуковую информацию.

Информация для обработки должна быть представлена в виде понятной компьютеру.

Мы также назвали устройства, с помощью которых информация вводится в компьютер. Это, прежде всего клавиатура. Рассмотрим, как преобразуется информация, прежде чем появиться на мониторе.

Из схемы, показанной на рис. 1 видно, что процессор компьютера обрабатывает информацию, только представленную в виде двоичных чисел и внутренних кодов.

Информация с клавиатуры, прежде чем попасть на обработку в процессор поступает на кодирующее устройство - шифратор.

Название “шифратор” связано с тем, что первые коды (шифры) появились еще в глубокой древности и использовались для засекречивания важных сообщений от тех, кому они не были предназначены.

В задачу нашего кодирования входит не засекречивание сообщений, а иная цель: преобразовать входную информацию в вид понятный компьютеру. Предназначенное для этой цели кодирующее устройство (шифратор) сопоставляет каждому символу исходного текста определенное двоичное число (код). Далее информация в виде двоичного кода поступает на обработку в процессор. После обработки информация через дешифратор (устройство для обратного преобразования) поступает на устройство вывода.

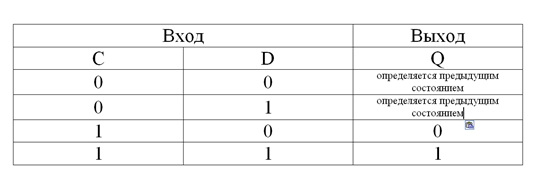

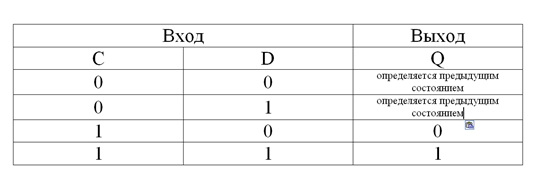

Рассмотрим более подробно устройство для кодирования числовой информации. Для ввода числовой информации в компьютер может быть использована обыкновенная клавиатура, которая содержит десятичные цифры.

Как известно, основанием системы счисления является число знаков или символов, используемых для изображения цифр в данной системе счисления. Для десятичной системы счисления число таких символов десять, это - 0,1,2,3,4,5,6,7,8,9. В двоичной системе счисления таких знаков два – 0 и 1. Следовательно, кодирующее устройство (шифратор) должно преобразовать входную информацию в виде десятичного числа в двоичное число, т.е. каждой цифре десятичной системе счисления поставить в соответствие определенный код двоичного числа.

Мы с вами знакомы с правилами перевода чисел из десятичной системы счисления в двоичную систему счисления. Также нам известно, что для представления цифры 9 в двоичной системе счисления необходимо четырехразрядное двоичное число. Составим таблицу истинности.

Таблица 1

| Десятичное число | Двоичный код числа |

| Четвертый разряд | Третий разряд | Второй разряд | Первый разряд |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

В таблице записаны десятичные числа и им поставлены в соответствие двоичные. Проанализировав таблицу, можно сделать следующие выводы, необходимые для построения кодирующего устройства. Входное устройство должно содержать десять клавиш, от 0 до 9. На выходе устройства будет четырехразрядный двоичный код. Причем, на выходе первого разряда информация (логическая 1) будет, в случае если нажаты клавиши 1,3,5,7,9. На выходе второго разряда 1 будет в случае, когда нажаты клавиши 2,3,6,7. На выходе третьего разряда 1 будет в случае, когда нажаты клавиши 4,5,6,7. На выходе четвертого – когда нажаты клавиши 8 или 9. Для построения устройства нам необходимы логические элементы ИЛИ, которые объединят информацию с клавиш и выдадут ее на соответствующий разряд.

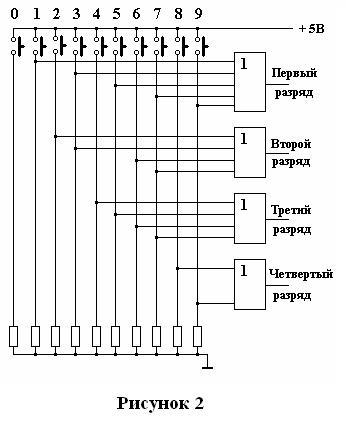

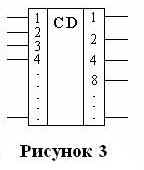

Схема такого устройства изображена на рисунке 2. Условное изображение шифратора, используемое на логических схемах, изображено на рисунке 3.

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

12. Классификация регистров

Регистры классифицируются по следующим видам:

· накопительные (регистры памяти, хранения);

· сдвигающие или сдвиговые.

В свою очередь сдвигающие регистры делятся:

· по способу ввода-вывода информации:

Ø параллельные: запись и считывание информации происходит одновременно на все входы и со всех выходов;

Ø последовательные: запись и считывание информации происходит в первый триггер, а та информация, которая была в этом триггере, перезаписывается в следующий — то же самое происходит и с остальными триггерами;

Ø комбинированные;

· по направлению передачи информации:

Ø однонаправленные;

Ø реверсивные.

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

13. Асинхронный трехразрядный двоичный суммирующий счетчик

Счетчиком называется электронная схема, предназначенная для подсчета числа сигналов, поступающих на его счетный вход. Счетчики используются в устройстве управления компьютера при построении распределителей импульсов и организации циклов, в счетчиках команд для формирования адреса выполняемой команды при естественном порядке выполнения и в некоторых других устройствах ЭВМ. Также счетчики широко применяются в качестве самостоятельных узлов в различных системах цифровой автоматики.

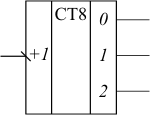

Суть работы счетчика заключается в изменении на единицу зафиксированного в нем значения с приходом каждого счетного сигнала. Счетчики принято подразделять на суммирующие, вычитающие и реверсивные. Суммирующие счетчики увеличивают свое значение, вычитающие – уменьшают, а реверсивные могут работать как на прибавление, так и на вычитание в зависимости от сигналов управления. Параметром, определяющим информационную емкость счетчика, является модуль пересчета, равный числу внутренних состояний. Это значение проставляется на УГО после аббревиатуры CT.

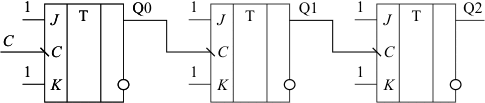

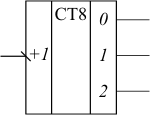

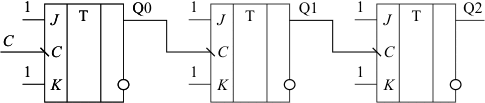

Пример асинхронного трехразрядного двоичного суммирующего счетчика приведен на рис. 1, а его условно-графическое обозначение – на рис. 2. Для построения этого счетчика использованы JK-триггеры с динамической синхронизацией по спаду синхросигнала. Каждый JK-триггер в счетчикевключен в режим инвертирования своего состояния при переключении синхросигнала с высокого уровня на низкий (см. табл. 1). Идеализированная временная диаграмма работы этого счетчика показана на рис. 3.

Рис. 1. Схема асинхронного трехразрядного счетчика

Рис. 2. Условно-графическое обозначение

трехразрядного суммирующего счетчика

Рис. 3. Временная диаграмма работы счетчика

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

14. Дешифратор, назначение, применение

Для обратного преобразования двоичных чисел в небольшие по значению десятичные числа используются дешифраторы (называемые так же декодерами). Входы дешифратора предназначаются для подачи двоичных чисел, выходы последовательно нумеруются десятичными числами. При подаче на входы двоичного числа появляется сигнал на определенном выходе, номер которого соответствует входному числу.

Дешифраторы имеют широкое применение. В частности, они используются в устройствах, печатающих на бумаге выводимые из цифрового устройства числа или текст. В таких устройствах двоичное число, поступая на вход дешифратора, вызывает появление сигнала на определенном его выходе. С помощью этого сигнала производится печать символа, соответствующего входному двоичному числу.

Дешифраторы (наряду с дешифраторами, мультиплексорами, демультиплексорами – все они относятся к классу схем двойного назначения) широко используются для коммутации в устройствах процессорной техники, и вычислительной технике.

Дешифраторы относятся к той же группе, только работают с точностью до наоборот. Они преобразуют параллельный двоичный код в позиционный десятичный. Условное графическое обозначение на схеме может быть таким.

Если говорить о дешифраторах более полно, то стоит сказать, что они могут преобразовывать двоичный код в разные системы счисления (десятичную, шестнадцатиричную и пр.). Всё зависит от конкретной цели и назначения микросхемы.

Простейший пример. Вы не раз видели цифровой семисегментный индикатор, например, светодиодный. На нём отображаются десятичные цифры и числа к которым мы привыкли с детства (1, 2, 3, 4...). Но, как известно, цифровая электроника работает с двоичными числами, которые представляют комбинацию 0 и 1. Что же преобразовало двоичный код в десятичный и подало результат на цифровой семисегментный индикатор? Наверное, вы уже догадались, что это сделал дешифратор.

Работу дешифратора можно оценить вживую, если собрать несложную схему, которая состоит из микросхемы-дешифратора К176ИД2 и светодиодного семисегментного индикатора, который ещё называют «восьмёркой». Взгляните на схему, по ней легче разобраться, как работает дешифратор. Для быстрой сборки схемы можно использоватьбеспаечную макетную плату.

Для справки. Микросхема К176ИД2 разрабатывалась для управления 7-ми сегментным светодиодным индикатором. Эта микросхема способна преобразовать двоичный код от 0000до 1001, что соответствует десятичным цифрам от 0 до 9 (одна декада). Остальные, более старшие комбинации просто не отображаются. Выводы C, S, K являются вспомогательными.

У микросхемы К176ИД2 есть четыре входа (1, 2, 4, 8). Их ещё иногда обозначают D0 – D3. На эти входы подаётся параллельный двоичный код (например, 0001). В данном случае, двоичный код имеет 4 разряда. Микросхема преобразует код так, что на выходах (a – g) появляются сигналы, которые и формируют на семисегментном индикаторе десятичные цифры и числа, к которым мы привыкли. Так как дешифратор К176ИД2 способен отобразить десятичные цифры в интервале от 0 до 9, то на индикаторе мы увидим только их.

Ко входам дешифратора К176ИД2 подключены 4 тумблера (S1 - S4), с помощью которых на дешифратор можно подать параллельный двоичный код. Например, при замыкании тумблераS1 на 5 вывод микросхемы подаётся логическая единица. Если же разомкнуть контакты тумблера S1 – это будет соответствовать логическому нулю. С помощью тумблеров мы сможем вручную устанавливать на входах микросхемы логическую 1 или 0. Думаю, с этим всё понятно.

На схеме показано, как на входы дешифратора DD1 подан код 0101. На светодиодном индикаторе отобразится цифра 5. Если замкнуть только тумблер S4, то на индикаторе отобразится цифра 8. Чтобы записать число от 0 до 9 в двоичном коде достаточно четырёх разрядов: a3* 8 + a2* 4 + a1* 2 + a0* 1, где a0 – a3, - это цифры из системы счисления (0 или 1).

Представим число 0101 в десятичном виде 0101 = 0*8 + 1*4 + 0*2 + 1*1 = 4 + 1 = 5. Теперь взглянем на схему и увидим, что вес разряда соответствует цифре, на которую умножается 0 или 1 в формуле.

Дешифратор на базе технологии ТТЛ - К155ИД1 использовался в своё время для управления газоразрядным цифровым индикатором типа ИН8, ИН12, которые были очень востребованы в 70-е годы, так как светодиодные низковольтные индикаторы ещё были очень большой редкостью.

Всё изменилось в 80-е годы. Можно было свободно приобрести семисегментные светодиодные матрицы (индикаторы) и среди радиолюбителей прокатился бум сборки электронных часов. Самодельные электронные часы не собрал для дома только ленивый.

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

15. Чем характеризуются асинхронные и синхронные триггеры

Триггеры широко используются для создания различных счетчиков и делителей частоты. На них строятся элементы памяти, такие как ОЗУ или регистры.

Изучение работы триггеров начнем с простейшего триггера, который называется RS триггер.

RS триггер получил название по названию своих входов. Вход S (Set — установить англ.) позволяет устанавливать выход триггера Q в единичное состояние (записывать единицу). Вход R (Reset — сбросить англ.) позволяет сбрасывать выход триггера Q (Quit — выход англ.) в нулевое состояние (записывать ноль).

Для реализации RS триггера воспользуемся логическими элементами "2И-НЕ". Его принципиальная схема приведена на рисунке 1.

Рисунок 1. Схема простейшего rs триггера на схемах "2И-НЕ". Входы R и S инверсные (активный уровень'0').

Асинхронные триггеры имеют только информационный вход и срабатывают непосредственно за изменением сигналов на входе.

У синхронных триггеров смены информации на информационных входах недостаточно для срабатывания. Необходим дополнительный импульс, подаваемый на тактирующий вход.

Синхронные сигналы вырабатывают специальными генераторами тактирующих импульсов, которые задают частоту смены информации.

Основной недостаток – незащищенность перед опасными состязаниями сигналов, то есть возникновение временных сдвигов из-за различных задержек распространения сигнала, проходящего по различным цепям, низкая помехоустойчивость.

Срабатывание синхронных триггеров происходит при поступлении тактовых импульсов, длительность которых гораздо меньше их периода. В остальное время на входной сигнал триггер не реагирует, то есть, по сравнению с асинхронным, обладает более высокой помехоустойчивостью.

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

16. T триггер

T-триггер — это счетный триггер. У данного триггера имеется только один вход. Принцип работы T-триггера заключается в следующем. После поступления на вход T импульса, состояние триггера меняется на прямо противоположное. Счётным он называется потому, что T триггер как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние.

T-триггеры строятся только на базе двухступенчатых триггеров, подобных рассмотренному ранее D триггеру. Использование двух триггеров позволяет избежать неопределенного состояния схемы при разрешающем потенциале на входе синхронизации "C", так как счетные триггеры строятся при помощи схем с обратной связью

T триггер можно синтезировать из любого двухступенчатого триггера. Рассмотрим пример синтеза T триггера из динамического D триггера. Для того чтобы превратить D триггер в счётный, необходимо ввести цепь обратной связи с инверсного выхода этого триггера на вход, как показано на рисунке 1.

Рисунок 1. Схема T триггера, построенная на основе D триггера

Временная диаграмма T триггера приведена на рисунке 2. При построении этой временной диаграммы был использован триггер, работающий по заднему фронту синхронизирующего сигнала.

Рисунок 2. Временные диаграммы T триггера

Т-триггеры используются при построении схем различных счётчиков, поэтому в составе БИС различного назначения обычно есть готовые модули этих триггеров. Условно-графическое обозначение T триггера приведено на рисунке 3.

Рисунок 3. Условно-графическое обозначение T триггера

Существует еще одно представление T триггера. При разработке схем синхронных двоичных счетчиков важно осуществлять одновременную запись во все его триггеры. В этом случае вход T триггера служит только для разрешения изменения состояния на противоположное, а синхронизация производится отдельным входом "C". Подобная схема T триггера приведена на рисунке 4.

Рисунок 4. Схема синхронного T триггера, построенная на основе D триггера

Подобная схема счетного триггера может быть реализована и на JK триггере. Временная диаграмма синхронного T триггера приведена на рисунке 5, а его условно-графическое обозначение — на рисунке 6.

Рисунок 5. Временные диаграммы синхронного T триггера

Рисунок 6. Условно-графическое обозначение синхронного T триггера

Выводы T-триггеры широко применяются в схемах деления и умножения частоты. Без них было бы невозможна реализация синтезаторов частот, которые применяются в качестве задающих генераторов в передатчиках и гетеродинов в приемниках раций, мобильных телефонов или GSM навигаторов. Не менее важна роль T-триггеров в формировании тактовой частоты цифровых микросхем, таких как центральные процессоры компьютеров, планшетов или цифровых фотоаппаратов.

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

17. Трехразрядный peгистр со сдвигом вправо

Регистры с последовательным приемом или выдачей информации называются сдвиговыми регистрами или регистрами сдвига. Регистры сдвига могут выполнять функции хранения и преобразования информации. Они могут быть использованы для построения умножителей и делителей чисел двоичной системы счисления, т.к. сдвиг двоичного числа влево на один разряд соответствует умножению его на два, а сдвиг вправо - делению на два.

Наиболее простой схема регистра получается при использовании D-триггеров. В качестве примера рассмотрим трехразрядный регистр со сдвигом вправо, схема и условное графическое обозначение которого приведены на рис.1. Схема содержит три D-триггера с установочным R-входом.

Входом регистра является информационный вход триггера старшего разряда. Прямой выход триггера старшего разряда соединяется с информационным входом триггера следующего разряда. Синхровходы всех триггеров объединены и образуют синхровход регистра. Установочные входы всех триггеров также объединены и образуют установочный вход регистра. В качестве выхода регистра может быть использован любой прямой выход триггера и чаще всего прямой выход триггера младшего разряда. При таком соединении ввод кодовой комбинации должен начинаться с младшего разряда.

Входом регистра является информационный вход триггера старшего разряда. Прямой выход триггера старшего разряда соединяется с информационным входом триггера следующего разряда. Синхровходы всех триггеров объединены и образуют синхровход регистра. Установочные входы всех триггеров также объединены и образуют установочный вход регистра. В качестве выхода регистра может быть использован любой прямой выход триггера и чаще всего прямой выход триггера младшего разряда. При таком соединении ввод кодовой комбинации должен начинаться с младшего разряда.

Перед началом ввода подается импульс на вход R. При этом все триггеры переходят в состояние 0. Это исходное состояние регистра. Поскольку комбинация трехразрядная, то для её записи поразрядно потребуется три такта. В первом такте на информационный вход триггера прикладывается 1 младшего разряда и на синхровход подается первый тактовый импульс. По его окончании триггер Т2 переходит в состояние 1. Эта 1 с прямого выхода Т2 прикладывается к входу D триггера Т1, а на вход регистра подается следующий разряд кодовой комбинации 0. Поэтому при подаче второго тактового импульса триггер Т1 переходит в состояние 1, а Т2 в состояние 0. Теперь 1 прикладывается к входу триггера Т0, 0 - к входу Т1, а на вход триггера Т2 будет подаваться 1 старшего разряда. С приходом третьего тактового импульса триггер Т2 перейдет в состояние 1, Т1 - в состояние 0, а Т0 - в 1.

Таким образом, действительно за три такта исходная кодовая комбинация последовательно вводится в регистр, передвигаясь слева направо, т.е. со сдвигом вправо. Если теперь на вход регистра подать 0 и продолжить подачу тактовых импульсов, то на выходе Q0 последовательно появляется записанная кодовая комбинация, начиная с младшего разряда.

Необходимо заметить, что после третьего тактового импульса, когда вся кодовая комбинация записана в регистр, её можно считать в параллельном коде с выходов Q2, Q1, Q0, т.е. осуществить преобразование последовательного кода в параллельный. Если необходимо осуществить обратное преобразование параллельного кода в последовательный, то параллельную кодовую комбинацию следует подать на входы регистра D2, D1, D0 . Тогда тактовый импульс произведет её запись, а три последующих - её вывод на выходе Q0.

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

18. Счетчик. Применение, суть работы счетчика

Счётчики используются для построения схем таймеров или для выборки инструкций из ПЗУ в микропроцессорах. Они могут использоваться как делители частоты в управляемых генераторах частоты (синтезаторах). При использовании в цепи ФАП счётчики могут быть использованы для умножения частоты как в синтезаторах, так и в микропроцессорах.

Принцип работы счетчика

Счётчики используются для построения таймеров или для выборки инструкций из ПЗУ в микропроцессорах. Они могут использоваться как делители частоты в управляемых генераторах частоты (синтезаторах). При использовании в цепи ФАП счётчики могут быть использованы для умножения частоты как в синтезаторах, так и в микропроцессорах.

Простейший вид счётчика - двоичный может быть построен на основе T-триггера. T-триггер изменяет своё состояние на прямо противоположное при поступлении на его вход синхронизации импульсов. Счётчики могут не только увеличивать своё значение на единицу при поступлении на счётный вход импульсов, но и уменьшать его.

Схема счётчика, позволяющего посчитать любое количество импульсов, меньшее шестнадцати, приведена на рисунке 4. Количество поступивших на вход импульсов можно узнать, подключившись к выходам счётчика Q0 … Q3. Это число будет представлено в двоичном коде.

Рис. 4. Схема четырёхразрядного счётчика, построенного на универсальных D-триггерах

Для того чтобы разобраться, как работает схема двоичного счётчика, воспользуемся временными диаграммами сигналов на входе и выходах этой схемы, приведёнными на рисунке 5.

Рис. 5. Временная диаграмма четырёхразрядного счётчика

Пусть первоначальное состояние всех триггеров счётчика будет нулевым. Это состояние мы видим на временных диаграммах. Запишем его в таблицу 1. После поступления на вход счётчика тактового импульса (который воспринимается по заднему фронту) первый триггер изменяет своё состояние на противоположное, то есть единицу.

Запишем новое состояние выходов счётчика в ту же самую таблицу. Так как по приходу первого импульса изменилось состояние первого триггера, то этот триггер содержит младший разряд двоичного числа (единицы). В таблице поместим его значение на самом правом месте, как это принято при записи любых многоразрядных чисел. Здесь мы впервые сталкиваемся с противоречием правил записи чисел и правил распространения сигналов на принципиальных схемах.

Подадим на вход счётчика ещё один тактовый импульс. Значение первого триггера снова изменится на прямо противоположное. На этот раз на выходе первого триггера, а значит и на входе второго триггера сформируется задний фронт. Это означает, что второй триггер тоже изменит своё состояние на противоположное. Это отчётливо видно на временных диаграммах, приведённых на рисунке 5. Запишем новое состояние выходов счётчика в таблицу 1. В этой строке таблицы образовалось двоичное число 2. Оно совпадает с номером входного импульса.

Продолжая анализировать временную диаграмму, можно определить, что на выходах приведённой схемы счётчика последовательно появляются цифры от 0 до 15. Эти цифры записаны в двоичном виде. При поступлении на счётный вход счётчика очередного импульса, содержимое его триггеров увеличивается на 1. Поэтому такие счётчики получили название суммирующих двоичных счётчиков.

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

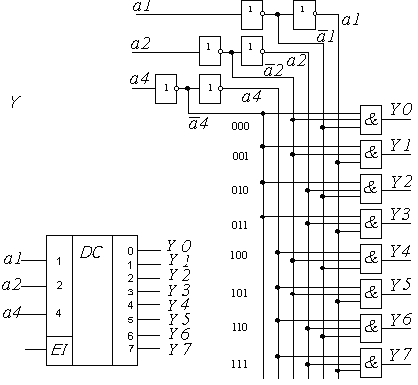

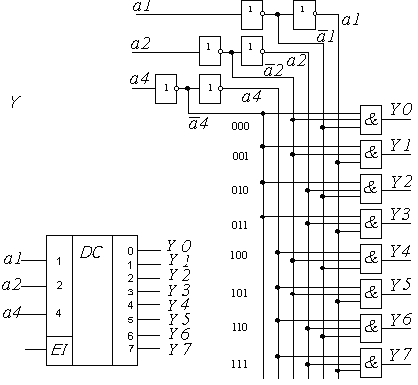

19. Описать работу дешифратора 3-8

Дешифраторы относятся к комбинационным схемам, которые предназначены для преобразования двоичного или двоично-десятичного кода в позиционный.

Дешифратор (декодер) – это комбинационное устройство с несколькими входами и выходами, у которого определенным комбинациям входных сигналов соответствует активное состояние одного из выходов. Дешифраторы преобразуют двоичный или двоично-десятичный код в унитарный код. Если декодер имеет nвходов,mвыходов и использует все возможные наборы входных переменных, тоm= 2n. Такой декодер называют полным. Если используется лишь часть наборов, то такой декодер называют неполным. Дешифраторы используют, когда нужно обращаться к различным цифровым устройствам, и при этом номер устройства (его адрес) представлен двоичным кодом.Входы декодера (адресные входы) часто номеруют не порядковыми номерами, а в соответствии с весами двоичных разрядов, т. е. не 1, 2, 3, 4, а 1, 2, 4, 8.

Формально описать работу дешифратора можно, задав список функций, отрабатываемых каждым из его выходов Yi

Разрешающий вход дешифратора может быть прямым или инверсным. У дешифраторов с прямым разрешающим входом активным уровнем является уровень логической единицы, у дешифраторов с инверсным входом – уровень логического нуля.

1.1 Функция алгебры логики дешифратора:

,

, ,

,

, ---------------------,

, ---------------------, ,

,

Рис 2. Линейный дешифратор 3-8 на элементах И с двойной инверсией входных переменных (а– условное обозначение; б– структура)

Современный компьютер может обрабатывать, как мы уже знаем, числовую, текстовую, графическую и звуковую информацию.

Современный компьютер может обрабатывать, как мы уже знаем, числовую, текстовую, графическую и звуковую информацию.

Входом регистра является информационный вход триггера старшего разряда. Прямой выход триггера старшего разряда соединяется с информационным входом триггера следующего разряда. Синхровходы всех триггеров объединены и образуют синхровход регистра. Установочные входы всех триггеров также объединены и образуют установочный вход регистра. В качестве выхода регистра может быть использован любой прямой выход триггера и чаще всего прямой выход триггера младшего разряда. При таком соединении ввод кодовой комбинации должен начинаться с младшего разряда.

Входом регистра является информационный вход триггера старшего разряда. Прямой выход триггера старшего разряда соединяется с информационным входом триггера следующего разряда. Синхровходы всех триггеров объединены и образуют синхровход регистра. Установочные входы всех триггеров также объединены и образуют установочный вход регистра. В качестве выхода регистра может быть использован любой прямой выход триггера и чаще всего прямой выход триггера младшего разряда. При таком соединении ввод кодовой комбинации должен начинаться с младшего разряда.

,

, ,

, , ---------------------,

, ---------------------, ,

,