Подключение оборудования к плате xilinx zynq zc702

ЦЕЛЬ

Используя “Zynq-7000 All Programmable SoC Video and Imagining Kit” изучить возможности фильтрации и вывода изображения с камеры VITA-2000 на FULL HD монитор.

ЗАДАЧИ

В рамках изучения встроенных методов фильтрации, выполнить следующие задачи:

1. Получить лицензию на использование IP core[1], далее IP ядро, для обработки видео изображения

2. Подготовить оборудование: SD карту, ПК под управлением ОС Windows, плату Xilinx Zynq ZC702 и камеру VITA-2000

3. Подключить оборудование к плате

4. Изучить процесс запуска проекта на плате

5. Ознакомиться со встроенными методами фильтрации

6. Ознакомиться с аппаратной и программной платформами

7. Получить искаженное изображение и отфильтровать его с помощью веб-интерфейса, предоставленного на сайте.

8. Вывести отфильтрованное изображение на Full HD монитор

ОБОРУДОВАНИЕ

1. Плата Xilinx XC7Z020 ZC702

2. Модуль Avnet FMC-IMAGEON

3. Модуль камеры VITA-2000

4. HDMI кабель

5. Карта памяти SD-MMC

6. Адаптер питания платы 12 вольт

7. Компьютер под управлением Windows

8.Сетевой роутер(Ethernet router)

ХОД РАБОТЫ

ПОЛУЧЕНИЕ ЛИЦЕНЗИИ

В данной работе используются проприетарные IP ядра, а именно Xilinx Video and Image Processing Pack IP cores. IP ядра представляют собой программную или аппаратную реализацию некоторого компонента системы и являются интеллектуальной собственностью компании.

При выполнения данной работы необходимо получить лицензию на использование IP ядер (данная лицензия бесплатна).

Для получения лицензии необходимо:

1. Посетить сайт Xilinx (необходима регистрация): http://www.xilinx.com/products/intellectual-property/ef-di-vid-img-ip-pack.html

2. Нажать кнопку Evaluate, расположенную в левом верхнем углу страницы и далее следовать предложенным инструкциям.

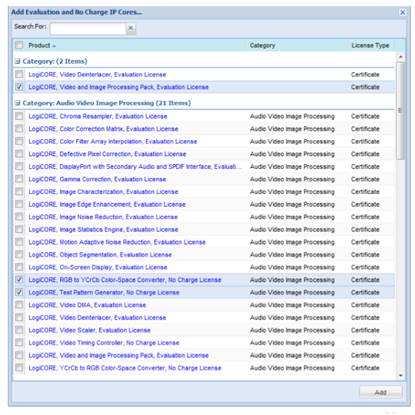

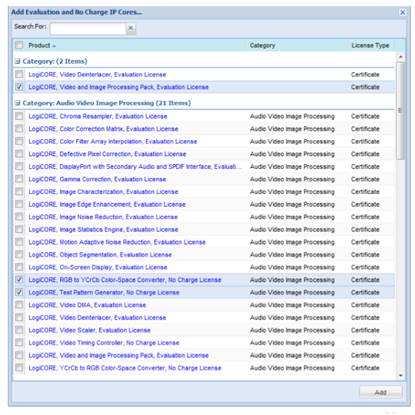

3. Выбрать Add Evaluation and No Change IP Cores и запросить лицензию на использование Xilinx Video and Image Processing Pack IP cores и пакетов Test Pattern Generator, RGB to YCrCb

Рис.1. Запрос лицензии

4. Нажать кнопку Add

5. Файлы лицензии будут отправлены на электронную почту, указанную при регистрации.

ПОДГОТОВКА ОБОРУДОВАНИЯ

ПОДГОТОВКА ПК

Для работы с веб-сервисом настройки камеры требуется сетевая карта компьютера, а также предполагается использование компьютером одной локальной сети с платой Xilinx Zynq ZC702.[2] Использование полного функционала ПО подразумевает установку программ Xilinx SDK и Putty. Компьютер должен иметь IP адрес, принадлежащий одной и той же сети, что и плата Xilinx Zynq ZC702.

ПОДГОТОВКА SD-КАРТЫ

Подготовить SD карту возможно несколькими способами:

1. С помощью программного пакета Vivado

2. Вручную

В данной работе будет рассмотрен второй метод.

Для подготовки SD карты вручную необходимо использовать компьютер под управлением Windows, оборудованный устройством для чтения/записи SD карт. В первую очередь, необходимо скачать файлы для работы с видео камерой на плате Xilinx Zynq ZC702.

Данные файлы доступны по ссылке: https://secure.xilinx.com/webreg/clickthrough.do?cid=199792.

Загруженные бинарные файлы будут доступны по следующему пути: ..\zc-702-zvic-camera\binaries\sd-content. Для корректной работы программы необходимо прописать в файле config_my_ip.sh IP-адрес сети.[3]

Необходимо заметить, что плата ZC702 работает только с протоколом TCP/IPv4, а также то, что SD карта должна быть отформатирована (FAT32). После форматирования все файлы из папки ..\zc-702-zvic-camera\binaries\sd-content должны быть скопированы на SD карту.

ПОДГОТОВКА КАМЕРЫ

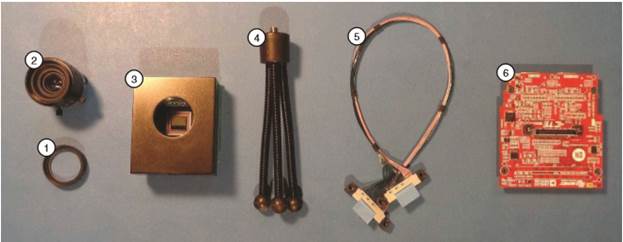

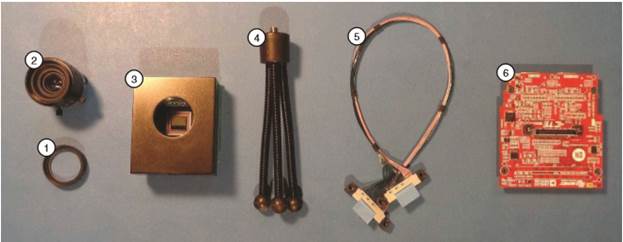

В комплект поставки камеры входят:

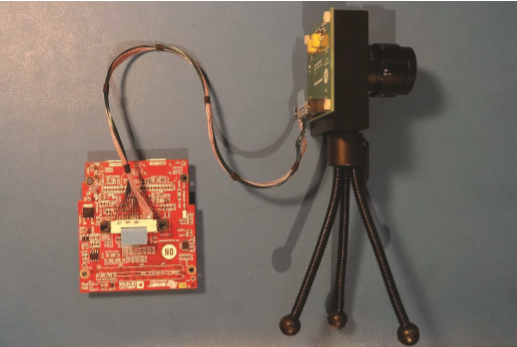

Рис. 2. Комплект поставки

1. ИК фильтр 2. Линзы 3. Модуль VITA-2000

4. Тренога 5. Кабель LCEDI 6. Плата Avnet FMC-IMAGEON

СБОРКА КАМЕРЫ

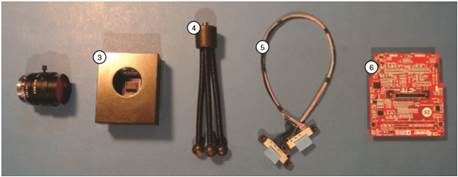

Для сборки камеры необходимо

1. Снять оба защитных колпачки с линз (деталь 2).

2. Присоединить фильтр ИК – частот (деталь 1) к линзам. Фильтр прикручивается.

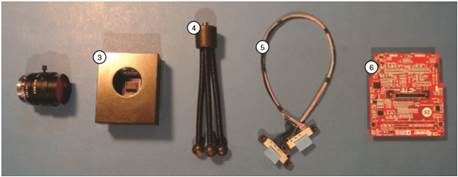

Рис. 3. Комплект поставки с собранным объективом

3. Прикрутить линзы, с установленным фильтром, к модулю VITA-2000(деталь 3).

4. Прикрутить треногу к модулю VITA-2000 (деталь 4).

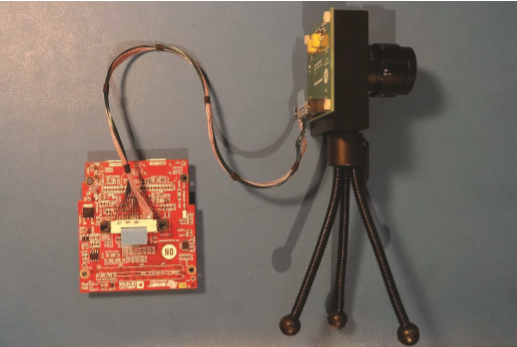

Рис. 4. Собранная камера

ПОДКЛЮЧЕНИЕ КАМЕРЫ К ПЛАТЕ AVNET FMC-IMAGEON

Для подключения камеры к плате Avnet FMC-IMAGEON требуется:

1. Присоединить кабель LCEDI (деталь 5) к разъёму, расположенному на задней панели модуля VITA-2000. Кабель LCEDI имеет одинаковые разъёмы с обеих сторон).

2. Присоединить второй конец кабеля LCEDI к плате FMC-IMAGEON(деталь 6)

Рис. 5. Плата, подключенная к камере

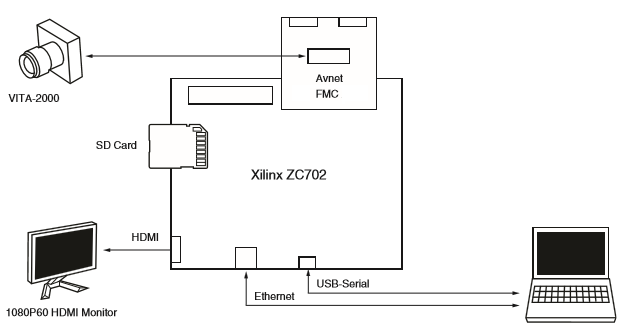

АППАРАТНАЯ ПЛАТФОРМА

Блок схема аппаратной платформы для работы с камерой приведена на рисунке 8.

Рис. 8. Блок схема аппаратной платформы

| Компонент FPGA | Всего доступно | Использовано | % Использования |

| I/O s | |||

| LUTs | 53,200 | 30,614 | |

| Регистры | 106,400 | 38б316 | |

| DSP48s | |||

| Блоки памяти | |||

| RAMB36E1/FIFO36E1s | |||

| RAMB18E1/FIFO18E1s |

Таблица 1. Использование аппаратной платформы

ПРОЦЕССОРНАЯ СИСТЕМА

· Два процессора ARM Cortex процессора, обладающий 32 Кб кэша для инструкций и 32 Кб для данных и сопроцессором NEON

· ARM процессор 800 МГц

· Кэш второго уровня 512 кб

· Оперативная память на чипе 256 кб

· Постоянная память на 128 кб

· Шина AMBA AXI

· Контроллер DDR DRAM 32-бит

· DDR3 DRAM 533 МГц

· Стандартные интерфейсы для периферийных устройств, включая USB, Ethernet, UART, l2C и т.д.

· Высокоскоростная шина для работы с ПЛИС

· Независимое от ПЛИС питание

ПРОГРАММИРУЕМАЯ ЛОГИКА

· Одна шина AXI 64 бит (148,5 МГц)

· Одна шина AXI 32 бит (50 МГц)

· Интерфейса для серийного порта LVDS

· Поток обработки видео

· Графический буфер(AXI-VDMA)

· Интерфейс выхода HDMI

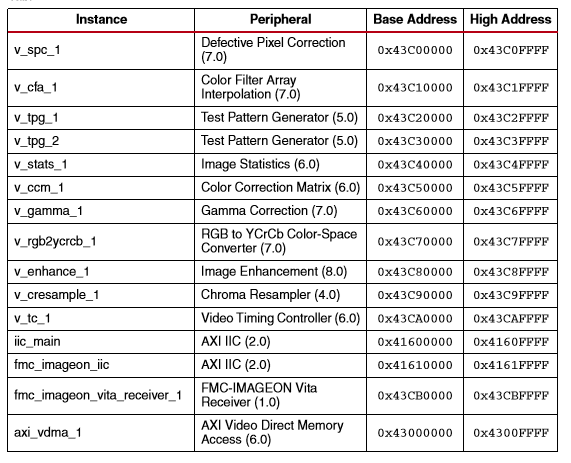

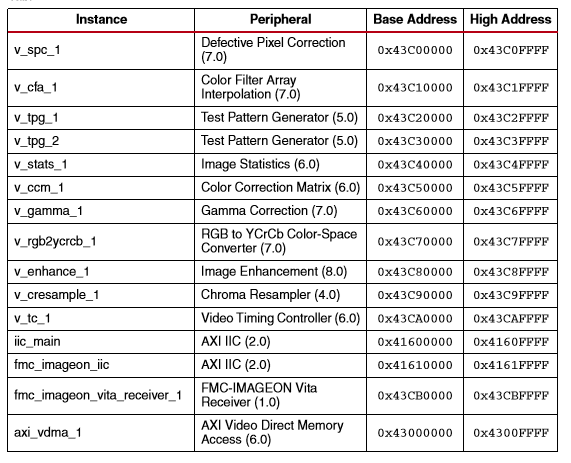

АДРЕСНАЯ КАРТА УСТРОЙСТВ

Таблица 2. Адресная карта устройств

СИСТЕМНАЯ КОНФИГУРАЦИЯ

ТАЙМЕРЫ

В проекте программируемой логики доступно два типа таймеров: AXI4-Lite (регистровый интерфейс) и видео счётчик. Видео счётчик управляет AXI4 (реализован в памяти), AXI4-Stream (потоковые) внешними устройствами, и выходными видео интерфейсами. Они работают на частотах 50 и 148,5 МГц соответственно.

Модуль генерации таймера(отсчётов) принимает входной сигнал на частоте 148,5 МГц от внешнего генератора сигналов, расположенного на карте Avnet FMC-IMAGEON, создаёт синхрочастоту 37,125 МГц для сенсора изображений VITA, и распространяет дальше сигнал частоты 148,5 МГц в качестве видео синхросигнала.

Вычислительная система генерирует AXI4-Lite сигнал частотой 50 МГц и использует опорный 200 МГц сигнал для десериализации видеоданных с приёмника VITA.

| Имя сигнала | Источник | Частота (МГц) | Назначение |

| clk_50MHz | PS – FCLK0 | Таймер шины AXI4-Lite | |

| clk_200MHz | PS – FCLK1 | Таймер синхросигналов для десериализации в видеоприёмнике VITA | |

| fmc_imageon_video_clk1 | Внешний видео-синхросигнал, приходит из синтезатора на модуле FMC | 148,5 | Генератор отсчётов из внешнего таймера |

| vid_out_clk | Генератор сигналов – МСС[4] | 148,5 | Сигнал для видеовхода, выхода, цепи видеообработки и шины AXI4 |

| vita_clk_ref | Генератор сигналов – МСС | 37,125 | Синхросигнал для сенсора изображений VITA |

Таблица 3. Системные таймеры

ШИНЫ AXI

В проекте программируемой логики есть одна шина для доступа к ведущему узлу - AXI4, и одна шина для регистрового интерфейса AXI4-Lite.

Шина AXI4 подключена к ведущему узлу – AXI VDMA. Она также соединена с ведомым узлом – портом HP0 вычислительной системы системы-на-кристалле Zynq-7000 AP. Эта шина работает на частоте 148,5 МГц и имеет разрядность 64 бита. Буферы приёма и выдачи для чтения/записи выставлены в 16. Они нужны для улучшения скорости работы системы. Порт вычислительной системы HP может держать в очереди 16 элементов.

Эти особенности чтения/записи при приёме/передаче налагают ограничения на минимальную пропускную способность приёма для каждого ведущего узла в многоузловой системе. Оптимальная настройка передачи и приёма уменьшает нагрузку на шину и компенсирует большие задержки.

Регистровый интерфейс AXI4-Lite работает на частоте 50 МГц. Порт GP0 системы выступает в роли ведущего узла этой шины, у других подсоединённых ведомых узлов есть карты регистров. AXI CFA и AXI VTC – примеры ведомых узлов, подключённых по этой шине. Операции потока видеообработки контролируются регистрами внутри каждого IP-ядра. В зависимости от того, требуется ли поток данных в потоке видеообработки, процессор устанавливает эти регистры через шину AXI4-Lite. Шина AXI4-Lite принимает запросы на чтение и запись от процессора, производит декодирование адресов, выбирает необходимого ведомого (получателя) и устанавливает канал соединения между процессором и целевым устройством-получателем.

КОНФИГУРАЦИЯ ВИДЕО СИСТЕМЫ

AXI VDMA

AXI VDMA имеет два интерфейса – AXI-Stream (потоковый) и AXI4, и два канала – MM2S и S2MM. Канал MM2S не реализован в данном проекте.

Канал S2MM принимает данные от ведущего узла, подключенного через потоковый интерфейс. Параметр C_S_AXIS_S2MM_TDATA_WIDTH определяет ширину канала потокового интерфейса, параметр C_M_AXIS_S2MM_TDATA_WIDTH определяет ширину интерфейса данных в памяти и C_S2MM_MAX_BURST_LENGTH управляет длиной очереди на транзакции на запись.

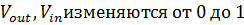

КОРРЕКЦИЯ ГАММЫ (КГ)

Рис. 20. Расположение КГ на потоке обработки видео

IP-ядро коррекции гаммы используется для создания таблиц.

Данные таблицы используются для преобразования линейного спектра RGB изображения окружающей среды, в нелинейные характеристики дисплея. В лучшем случае гамма коррекция выглядит следующим образом:

, где значения

На рисунке приведен пример коррекции гаммы:

Рис. 21. Пример коррекции гаммы

ПРЕОБРАЗОВАНИЕ ПРОСТРАНСТВА ЦВЕТОВ (ППЦ)

Рис. 22. Расположение ППЦ на потоке обработки видео

IP-ядро преобразования пространства цветов используется для перевода изображения из пространства цветов RGB в пространство цветов YCrCb.

УЛУЧШЕНИЕ ИЗОБРАЖЕНИЯ (УИ)

Рис. 23. Поток обработки видео

IP-ядро улучшения изображения используется для уменьшения шумов на изображении, выделения контуров изображения, подавления ореола, а также строит карту контуров, которая необходима для корректной работы шумоподавления. С помощью карты контуров контролируется сила и направление шумоподавления.

После выполнения выделения контуров по карте и шумоподавления, запускается опциональный модуль подавления ореола.

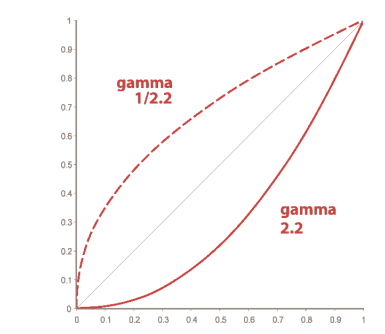

ПРОГРАММНАЯ ПЛАТФОРМА

Программная платформа написана для ОС Linux с ядром версии 3.x. Платформа представляет собой многопоточное приложение для обработки видео. Приложение также отвечает за соединение с ПК через USB или веб - интерфейс.

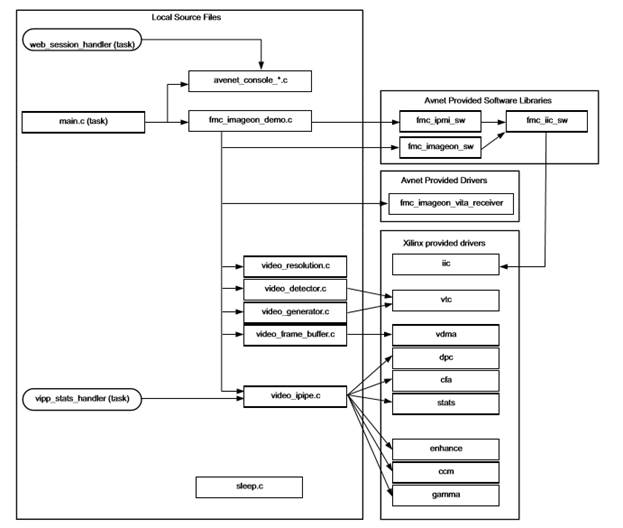

На блок схеме изображена архитектура приложения:

Рис. 24. Архитектура приложения

Программа состоит из трех основных процессов:

1. Процесса Main (main.c)

2. Процесса обработки видео(vipp_stats_handler)

3. Процесса управления веб-сессией

Следующая блок схема показывает файлы исходного кода для работы с видео камерой:

Рис. 25. Файлы исходного кода для работы с видео камерой

Файл fmc_imageon_demo.c включает в себя практически весь высокоуровневый код для инициализации камеры. Файлы avnet_console_* отвечают за работу с текстовым командным интерфейсом. Они используются для предоставления пользователю контроля через стандартные потоки ввода/вывода (STDIN, STDOUT). Этот интерфейс также используется для общения веб-интерфейса с приложением.

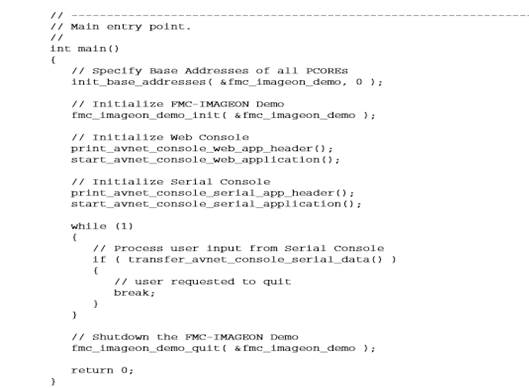

ПРОЦЕСС MAIN

Главный метод модуля Main – main(), который инициализирует основные компоненты программы. Он также инициализирует графический сенсор VITA, потоковую обработку изображения и графический буфер, а также запускает процессы управления веб-сессией и обработки видео.

Как только инициализация завершена, пользователю становится доступна работа с программой через стандартные потоки ввода-вывода(STDIN, STDOUT).

Исходный код файла main.c выглядит следующим образом:

Рис. 26. Исходный код файла main.c

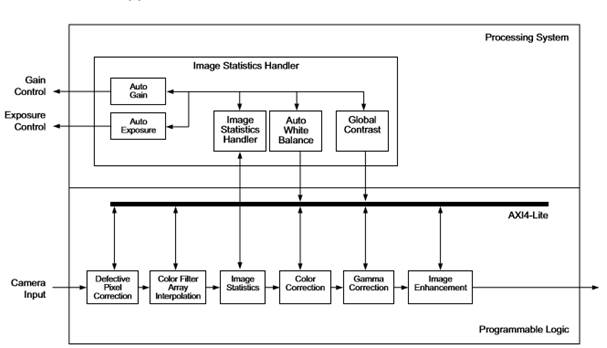

ПРОЦЕСС ОБРАБОТКИ ВИДЕО

Процесс обработки видео запускается сразу же после инициализации потока обработки видео. Данный процесс периодически считывает статистику изображения с сенсора и производит следующие операции:

1. Автоматическую коррекцию коэффициента усиления

2. Автоматическую коррекцию экспозиции

3. Автоматический выбор настроек баланса-белого

4. Автоматические настройки контраста

Блок - схема, показывающая как обработчик видео изображения взаимодействует с потоком обработки видеоизображения приведена ниже:

Рис. 27. Взаимодействие обработчика видео изображения с потоком обработки

Поток обработки видеоизображения состоит из следующих частей (IP-ядер):

1. Коррекции битых пикселей

2. Цветовой фильтрации

3. Сбора статистики по изображению

4. Цветовой коррекции

5. Коррекции гаммы

6. Улучшения изображения

IP-ядро сбора статистики напрямую связывается с программой Linux Image Statistics Handler. Оно собирает статистические данные об изображении, поступающие с камеры, включая гистограммы интенсивности уровня цветности сигнала, использующиеся для автоматической подгонки изображения для улучшения качества.

Процесс обработки видео изображения предоставляет несколько примеров для обработки изображения, основанных на работе с IP-ядрами, а именно:

1. Автокоррекцию баланса белого

2. Автоматическую коррекцию коэффициента усиления

3. Автоматическую коррекцию экспозиции

4. Автоматическую настройку контраста

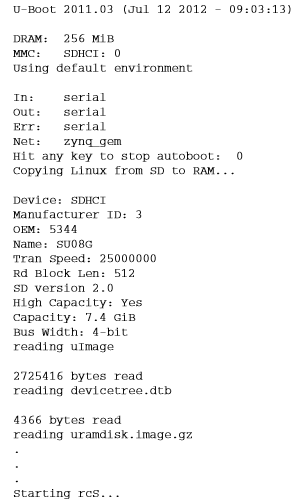

ЗАГРУЗКА ПЛАТЫ

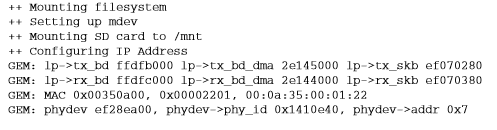

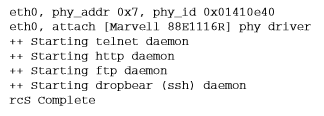

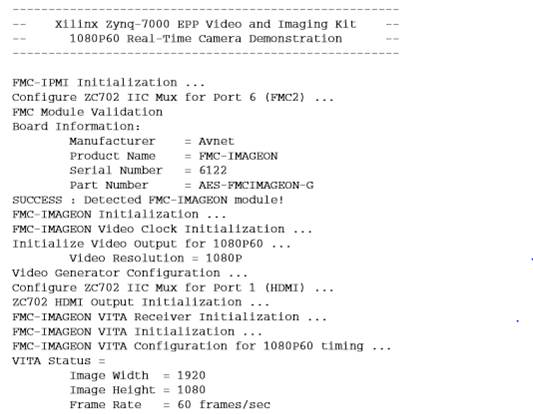

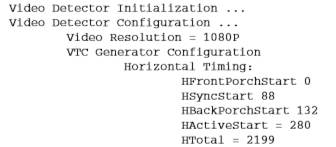

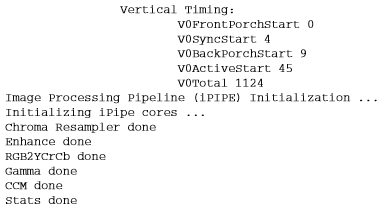

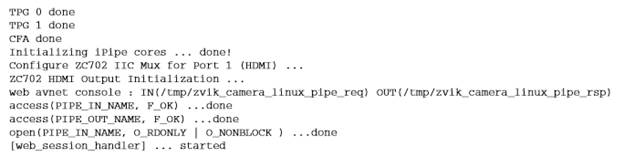

После включения платы, запускается процесс загрузки, который выглядит следующим образом:

1. Плата ZC702 включается

2. Светодиод DONE выключен

3. Производится загрузка ПЛИС, во время которой настраивается работа с камерой. На это требуется около 20 секунд

4. После завершения загрузки ПЛИС включается светодиод DONE

5. Загрузчик U-boot копирует Linux с SD карты в оперативную память платы ZC702. Данный процесс занимает примерно 30 секунд

6. Загрузчик загружает ядро Linux. На это требуется примерно 15 секунд

7. Скрипт загрузки ПО, для работы с камерой, загружает необходимые данные. Это занимает примерно 5 секунд

8. Скрипт для включения веб - интерфейса ПО разворачивает веб-сервер через порт 80. Это занимает около 40 секунд

В общей сложности загрузка до появления изображения на экране занимает около 70 секунд, а до возможности работать с веб-интерфейсом 110 секунд.

Процесс загрузки можно наблюдать через терминал, входящий в пакет Xilinx SDK.

При просмотре процесса загрузки через серийный порт можно увидеть следующую информацию:

ОТЛАДКА ПРИЛОЖЕНИЯ

Для отладки приложения необходимо:

1. Сменить перспективу ( перспектива отладки) в SDK (Window -> Perspective-> Debug Perspective, C/C++(Default)).

2. Выбрать приложение zvic_camera_linux_app, щёлкнув по нему правой кнопкой мыши, а затем выберать Debug as-> Debug Configuration

3. В окне настроек конфигурации отладки выбрать Remote ARM Linux Application

4. Ввести адрес платы, например, 192.168.70.153

5. В поле абсолютный удаленный путь ввести /tmp/zvik_camera_linux_app.elf

6. Нажать “Применить”

7. Нажать “Debug”

8. Нажать “Yes”.

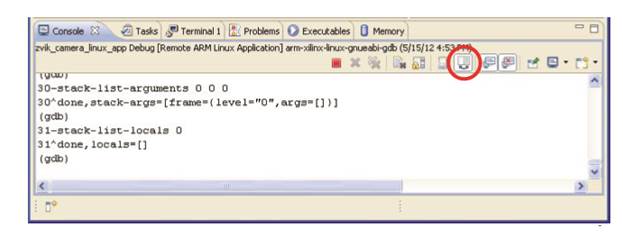

9. В консоли включить “verbose console mode”

Рис 32. Расположение“verbose console mode”

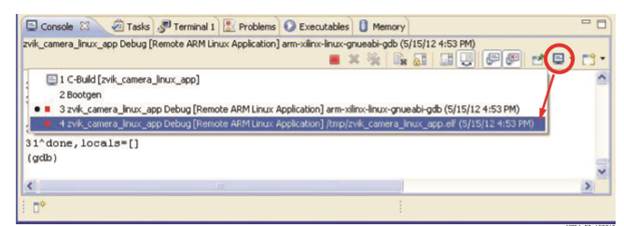

10. Выбрать zvik_camra_linux_app.elf

Рис 31. Расположение zvik_camra_linux_app.elf

11. Нажать F8

УСТАНОВКА ТОЧЕК ОСТАНОВКИ

Для установки точки остановки в файле avnet_console.c, на функции avnet_console_record_command, необходимо:

1. Выбрать Window-> Open Perspective -> C/C++

2. Выбрать файл avnrt_console.c

3. Поставить точку у функции avnet_console_record_command.

4. Вернуться в перспективу отладки.

5. В терминале ввести команду rec /mnt/image1.bmp .

6. Отладчик остановится на команде avnet_console_record_command. Нажать кнопку F8.

7. Перейти в перспективу Remote System Explorer

8. Перейти в директорию /mnt/

9. Нажать обновить, созданный bmp файл будет виден в обозревателе.

10. Нажать F8.

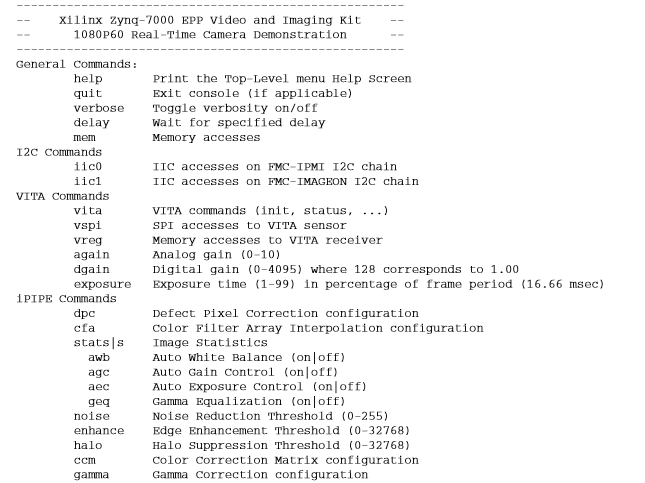

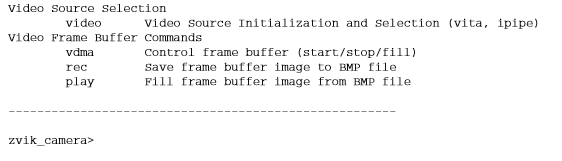

ПРОГРАММНОЕ ОБЕСПЕЧЕНИЕ ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЯ (КОМАНДНАЯ СТРОКА)

Для подключения к плате мы использовали терминал программы Xilinx SDK. После подключения через терминал становится доступной командная строка. В данной командной строке можно использовать команды для настройки камеры, настройки изображения, настройки фильтрации, удаления шумов, настройки источника изображения, управления видео буфером.

Рассмотрим несколько команд:

help – выводит полный список доступных команд

<команда> help – выводит описание конкретной команды

rec <имя файла> – сохраняет изображение из видео буфера в файл

play <имя файла> - записывает изображение из файла в видео буфер

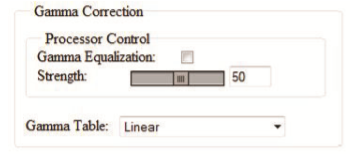

НАСТРОЙКА КОРРЕКЦИИ ГАММЫ

Рис. 38. Панель Gamma Correction

| Настройка | Описание |

| Linear | Коррекция отключена |

| Compression Table 1/2.2 | Коррекция включена (гамма =1/2.2) |

| Compression Table 1/1.6 | Коррекция включена (гамма =1/1.6) |

| Expansion Table 1.6 | Коррекция включена (гамма =1/1.6) |

| Expansion Table 2.2 | Коррекция включена (гамма =1/2.2) |

Таблица 12. Значения меню «таблица гаммы»

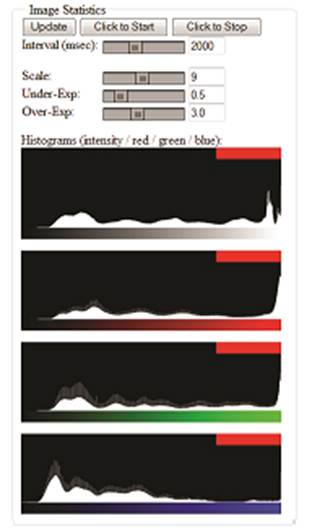

СТАТИСТИКА ИЗОБРАЖЕНИЯ

Рис. 39. Панель статистики изображения

ЗАХВАТ ИЗОБРАЖЕНИЯ

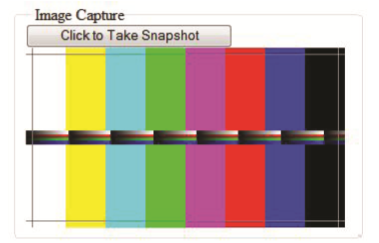

Рис. 40. Панель захвата изображения

Для захвата изображения необходимо нажать на кнопку Click to Take Snapshot. После захвата изображение возможно сохранить на компьютер. Изображение будет иметь формат BMP и разрешение Full HD.

ФИЛЬТРАЦИЯ ИЗОБРАЖЕНИЯ

В данной работе мы получили засвеченное изображение с битыми пикселями, шумами, не четкими контурами.

Рис. 41. Демонстрация исходного изображения

С помощью изменения настроек в веб-интерфейсе нам удалось избавиться от битых пикселей и увеличить четкость контуров на изображении, а также убрать шумы и отрегулировать яркость изображения.

Рис. 42. Демонстрация улучшения изображения

Отфильтрованное изображение было выведено на Full HD телевизор

Рис. 43. Вывод улучшенного изображения на Full HD телевизор

ВЫВОДЫ

В ходе данной работы мы изучили встроенные методы фильтрации, доступные на плате Xilinx Zynq ZC702. К ним относятся шумоподавление, выделение контуров, подавление ореола, коррекция гаммы.

Мы научились подготавливать оборудование, а именно настраивать компьютер, плату Xilinx Zynq ZC702, собирать и подключать камеру VITA-2000, разобрались с правилами подключения оборудования к плате Xilinx Zynq ZC702. Изучили аппаратную и программные платформы, в деталях разобрали поток обработки видео, выяснили для чего необходимо каждое из IP-ядер. Проверили несколько методов для подключения к плате через SSH: через терминал Putty, через терминал, входящий в SDK. Разобрались в процессе создания битового потока, создания приложения, а также в процессе отладки приложения непосредственно на плате(через SDK). Определили процесс запуска готового проекта на плате, выяснили, что в среднем запуск проекта занимает около 70 секунд, а запуск Веб интерфейса – около 110 секунд. Мы получили зашумлённое изображение с ошибками обработки и помощью внутренних методов фильтрации и очистили его от различного вида помех. Вывели отфильтрованное изображение на Full HD телевизор, и убедились, что методы фильтрации и улучшения изображения прекрасно справляются с подавлением шума, избавлением от битых пикселей, а также с определением гаммы и необходимого коэффициента усиления.

ПРИЛОЖЕНИЕ 1 ИСХОДНОЕ ИЗОБРАЖЕНИЕ

ПРИЛОЖЕНИЕ 2 ОБРАБОТАННОЕ ИЗОБРАЖЕНИЕ

[1] Intellectual property core - ядро, находящееся в интеллектуальной собственности

[2] В данной работе использовался адрес 192.168.70.153 с маской подсети 255.255.255.0.

[3] В данной работе использовался IP адрес 192.168.70.153 с маской подсети 255.255.255.0

[4] МСС – менеджер смешанных синхросигналов

[5]В данном случае 192.168.70.153

ЦЕЛЬ

Используя “Zynq-7000 All Programmable SoC Video and Imagining Kit” изучить возможности фильтрации и вывода изображения с камеры VITA-2000 на FULL HD монитор.

ЗАДАЧИ

В рамках изучения встроенных методов фильтрации, выполнить следующие задачи:

1. Получить лицензию на использование IP core[1], далее IP ядро, для обработки видео изображения

2. Подготовить оборудование: SD карту, ПК под управлением ОС Windows, плату Xilinx Zynq ZC702 и камеру VITA-2000

3. Подключить оборудование к плате

4. Изучить процесс запуска проекта на плате

5. Ознакомиться со встроенными методами фильтрации

6. Ознакомиться с аппаратной и программной платформами

7. Получить искаженное изображение и отфильтровать его с помощью веб-интерфейса, предоставленного на сайте.

8. Вывести отфильтрованное изображение на Full HD монитор

ОБОРУДОВАНИЕ

1. Плата Xilinx XC7Z020 ZC702

2. Модуль Avnet FMC-IMAGEON

3. Модуль камеры VITA-2000

4. HDMI кабель

5. Карта памяти SD-MMC

6. Адаптер питания платы 12 вольт

7. Компьютер под управлением Windows

8.Сетевой роутер(Ethernet router)

ХОД РАБОТЫ

ПОЛУЧЕНИЕ ЛИЦЕНЗИИ

В данной работе используются проприетарные IP ядра, а именно Xilinx Video and Image Processing Pack IP cores. IP ядра представляют собой программную или аппаратную реализацию некоторого компонента системы и являются интеллектуальной собственностью компании.

При выполнения данной работы необходимо получить лицензию на использование IP ядер (данная лицензия бесплатна).

Для получения лицензии необходимо:

1. Посетить сайт Xilinx (необходима регистрация): http://www.xilinx.com/products/intellectual-property/ef-di-vid-img-ip-pack.html

2. Нажать кнопку Evaluate, расположенную в левом верхнем углу страницы и далее следовать предложенным инструкциям.

3. Выбрать Add Evaluation and No Change IP Cores и запросить лицензию на использование Xilinx Video and Image Processing Pack IP cores и пакетов Test Pattern Generator, RGB to YCrCb

Рис.1. Запрос лицензии

4. Нажать кнопку Add

5. Файлы лицензии будут отправлены на электронную почту, указанную при регистрации.

ПОДГОТОВКА ОБОРУДОВАНИЯ

ПОДГОТОВКА ПК

Для работы с веб-сервисом настройки камеры требуется сетевая карта компьютера, а также предполагается использование компьютером одной локальной сети с платой Xilinx Zynq ZC702.[2] Использование полного функционала ПО подразумевает установку программ Xilinx SDK и Putty. Компьютер должен иметь IP адрес, принадлежащий одной и той же сети, что и плата Xilinx Zynq ZC702.

ПОДГОТОВКА SD-КАРТЫ

Подготовить SD карту возможно несколькими способами:

1. С помощью программного пакета Vivado

2. Вручную

В данной работе будет рассмотрен второй метод.

Для подготовки SD карты вручную необходимо использовать компьютер под управлением Windows, оборудованный устройством для чтения/записи SD карт. В первую очередь, необходимо скачать файлы для работы с видео камерой на плате Xilinx Zynq ZC702.

Данные файлы доступны по ссылке: https://secure.xilinx.com/webreg/clickthrough.do?cid=199792.

Загруженные бинарные файлы будут доступны по следующему пути: ..\zc-702-zvic-camera\binaries\sd-content. Для корректной работы программы необходимо прописать в файле config_my_ip.sh IP-адрес сети.[3]

Необходимо заметить, что плата ZC702 работает только с протоколом TCP/IPv4, а также то, что SD карта должна быть отформатирована (FAT32). После форматирования все файлы из папки ..\zc-702-zvic-camera\binaries\sd-content должны быть скопированы на SD карту.

ПОДГОТОВКА КАМЕРЫ

В комплект поставки камеры входят:

Рис. 2. Комплект поставки

1. ИК фильтр 2. Линзы 3. Модуль VITA-2000

4. Тренога 5. Кабель LCEDI 6. Плата Avnet FMC-IMAGEON

СБОРКА КАМЕРЫ

Для сборки камеры необходимо

1. Снять оба защитных колпачки с линз (деталь 2).

2. Присоединить фильтр ИК – частот (деталь 1) к линзам. Фильтр прикручивается.

Рис. 3. Комплект поставки с собранным объективом

3. Прикрутить линзы, с установленным фильтром, к модулю VITA-2000(деталь 3).

4. Прикрутить треногу к модулю VITA-2000 (деталь 4).

Рис. 4. Собранная камера

ПОДКЛЮЧЕНИЕ КАМЕРЫ К ПЛАТЕ AVNET FMC-IMAGEON

Для подключения камеры к плате Avnet FMC-IMAGEON требуется:

1. Присоединить кабель LCEDI (деталь 5) к разъёму, расположенному на задней панели модуля VITA-2000. Кабель LCEDI имеет одинаковые разъёмы с обеих сторон).

2. Присоединить второй конец кабеля LCEDI к плате FMC-IMAGEON(деталь 6)

Рис. 5. Плата, подключенная к камере

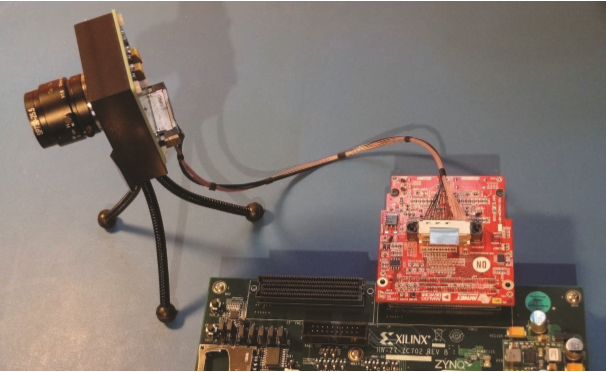

ПОДКЛЮЧЕНИЕ ОБОРУДОВАНИЯ К ПЛАТЕ XILINX ZYNQ ZC702

На рис.5 показано подключение оборудования к плате

Рис. 6. Схема подключения оборудования к плате

Подключение оборудования производится в следующем порядке.

1. Производится отключение питания платы

2. Производится отсоединение кабеля питания от платы

3. Плата Avnet FMC-IMAGEON подключается к слоту FMC #2 на плате ZC702

4. Камера VITA-2000 соединяется с платой Avnet с помощью кабеля LCEDI

Рис. 7. Подключение оборудования к плате AVENT

5. Full HD HDMI монитор(телевизор) подключается к HDMI порту платы ZC702

6. USB UART кабелем USB mini-B на USB-A подключается к плате и к компьютеру Ethernet кабель от роутера/маршрутизатора подключается к Ethernet разъёму на плате ZC702

7. SD карта вставляется в разъем для SD карт на плате ZC702

8. Переключатель SW16 переводится в следующее положение

Рис. 7. Переключатель SW 16

9. Производится подключение кабеля питания 12 вольт к плате

10. Производится включение платы

АППАРАТНАЯ ПЛАТФОРМА

Блок схема аппаратной платформы для работы с камерой приведена на рисунке 8.

Рис. 8. Блок схема аппаратной платформы

| Компонент FPGA | Всего доступно | Использовано | % Использования |

| I/O s | |||

| LUTs | 53,200 | 30,614 | |

| Регистры | 106,400 | 38б316 | |

| DSP48s | |||

| Блоки памяти | |||

| RAMB36E1/FIFO36E1s | |||

| RAMB18E1/FIFO18E1s |

Таблица 1. Использование аппаратной платформы

ПРОЦЕССОРНАЯ СИСТЕМА

· Два процессора ARM Cortex процессора, обладающий 32 Кб кэша для инструкций и 32 Кб для данных и сопроцессором NEON

· ARM процессор 800 МГц

· Кэш второго уровня 512 кб

· Оперативная память на чипе 256 кб

· Постоянная память на 128 кб

· Шина AMBA AXI

· Контроллер DDR DRAM 32-бит

· DDR3 DRAM 533 МГц

· Стандартные интерфейсы для периферийных устройств, включая USB, Ethernet, UART, l2C и т.д.

· Высокоскоростная шина для работы с ПЛИС

· Независимое от ПЛИС питание

ПРОГРАММИРУЕМАЯ ЛОГИКА

· Одна шина AXI 64 бит (148,5 МГц)

· Одна шина AXI 32 бит (50 МГц)

· Интерфейса для серийного порта LVDS

· Поток обработки видео

· Графический буфер(AXI-VDMA)

· Интерфейс выхода HDMI

АДРЕСНАЯ КАРТА УСТРОЙСТВ

Таблица 2. Адресная карта устройств

СИСТЕМНАЯ КОНФИГУРАЦИЯ

ТАЙМЕРЫ

В проекте программируемой логики доступно два типа таймеров: AXI4-Lite (регистровый интерфейс) и видео счётчик. Видео счётчик управляет AXI4 (реализован в памяти), AXI4-Stream (потоковые) внешними устройствами, и выходными видео интерфейсами. Они работают на частотах 50 и 148,5 МГц соответственно.

Модуль генерации таймера(отсчётов) принимает входной сигнал на частоте 148,5 МГц от внешнего генератора сигналов, расположенного на карте Avnet FMC-IMAGEON, создаёт синхрочастоту 37,125 МГц для сенсора изображений VITA, и распространяет дальше сигнал частоты 148,5 МГц в качестве видео синхросигнала.

Вычислительная система генерирует AXI4-Lite сигнал частотой 50 МГц и использует опорный 200 МГц сигнал для десериализации видеоданных с приёмника VITA.

| Имя сигнала | Источник | Частота (МГц) | Назначение |

| clk_50MHz | PS – FCLK0 | Таймер шины AXI4-Lite | |

| clk_200MHz | PS – FCLK1 | Таймер синхросигналов для десериализации в видеоприёмнике VITA | |

| fmc_imageon_video_clk1 | Внешний видео-синхросигнал, приходит из синтезатора на модуле FMC | 148,5 | Генератор отсчётов из внешнего таймера |

| vid_out_clk | Генератор сигналов – МСС[4] | 148,5 | Сигнал для видеовхода, выхода, цепи видеообработки и шины AXI4 |

| vita_clk_ref | Генератор сигналов – МСС | 37,125 | Синхросигнал для сенсора изображений VITA |

Таблица 3. Системные таймеры

ШИНЫ AXI

В проекте программируемой логики есть одна шина для доступа к ведущему узлу - AXI4, и одна шина для регистрового интерфейса AXI4-Lite.

Шина AXI4 подключена к ведущему узлу – AXI VDMA. Она также соединена с ведомым узлом – портом HP0 вычислительной системы системы-на-кристалле Zynq-7000 AP. Эта шина работает на частоте 148,5 МГц и имеет разрядность 64 бита. Буферы приёма и выдачи для чтения/записи выставлены в 16. Они нужны для улучшения скорости работы системы. Порт вычислительной системы HP может держать в очереди 16 элементов.

Эти особенности чтения/записи при приёме/передаче налагают ограничения на минимальную пропускную способность приёма для каждого ведущего узла в многоузловой системе. Оптимальная настройка передачи и приёма уменьшает нагрузку на шину и компенсирует большие задержки.

Регистровый интерфейс AXI4-Lite работает на частоте 50 МГц. Порт GP0 системы выступает в роли ведущего узла этой шины, у других подсоединённых ведомых узлов есть карты регистров. AXI CFA и AXI VTC – примеры ведомых узлов, подключённых по этой шине. Операции потока видеообработки контролируются регистрами внутри каждого IP-ядра. В зависимости от того, требуется ли поток данных в потоке видеообработки, процессор устанавливает эти регистры через шину AXI4-Lite. Шина AXI4-Lite принимает запросы на чтение и запись от процессора, производит декодирование адресов, выбирает необходимого ведомого (получателя) и устанавливает канал соединения между процессором и целевым устройством-получателем.

КОНФИГУРАЦИЯ ВИДЕО СИСТЕМЫ

AXI VDMA

AXI VDMA имеет два интерфейса – AXI-Stream (потоковый) и AXI4, и два канала – MM2S и S2MM. Канал MM2S не реализован в данном проекте.

Канал S2MM принимает данные от ведущего узла, подключенного через потоковый интерфейс. Параметр C_S_AXIS_S2MM_TDATA_WIDTH определяет ширину канала потокового интерфейса, параметр C_M_AXIS_S2MM_TDATA_WIDTH определяет ширину интерфейса данных в памяти и C_S2MM_MAX_BURST_LENGTH управляет длиной очереди на транзакции на запись.