Типовые узлы комбинационного типа

Дешифраторы.Дешифраторы ДС имеют несколько входов (п) и несколько выходов (N) и предназначены для преобразования входного кода в сигнал только на одном из выходов. Обычно N = 2". Такие дешифраторы называются полными. Входной сигнал рассматривается как двоичное число. При поступлении числа на входы дешифратора только на одном его выходе, номер которого равен числу на входе, выдается сигнал «1», а на остальных выходах — сигнал «0». Нумерация выходов начинается с «0». Например, если дешифратор имеет три входа и на него поступает сигнал «101», то на пятом выходе возникнет сигнал «1», а на остальных выходах – «0». Дешифраторы используются, например, в устройствах памяти для выбора заданной ячейки по ее адресу.

Наличие инверсных выходов означает что на одном из выходов дешифратора сигнал равен нулю, а на всех остальных единице.

Такой дешифратор состоит из нескольких одинаковых схем, не связанных между собой, и называется линейным. При большом числе входов дешифраторы имеют более сложную структуру (пирамидальные и ступенчатые дешифраторы).

Из дешифраторов с некоторым числом входов можно построить дешифратор на большее число входов. Входы синхронизации являются инверсными, т.е. при С=1 на всех выходах дешифраторасигналы равны единице, а при С=0 только на одном из выходов сигнал равен нулю, так как дешифратор имеет инверсные выходы.

Одноразрядный сумматор.Сумматоры выполняют арифметическое сложение чисел, которое производится начиная с младших разрядов чисел. В каждом разряде сумматора выполняются одинаковые действия, т.е. суммируются две двоичные цифры в coответствии с правилами сложения двоичных цифр. При сложении двух единиц возникает единица переноса в старший разряд, которую нужно учесть при сложении цифр следующего разряда. Taким образом, сумматор для сложении многоразрядных чисел можно построить из одинаковых схем, каждая из которых выполняет сложение двух цифр слагаемых и переноса из младшего разряда. Такая схема называется одноразрядным сумматором.

Полусумматор.Полусумматором, или одноразрядным сумматором на два входа, называется схема с двумя входами и двумя выходами. Полусумматоры могут быть использованы для построения схем одноразрядных сумматоров на три входа, а также схем ускорения умножения.

Многоразрядные сумматоры.Они строятся из одноразрядных сумматоров. Число одноразрядных сумматоров равно разрядности слагаемых. При этом одноразрядные сумматоры связаны между собой только цепями переносов. Сумматор с параллельными переносами состоит из схемы формирования суммы и схемы ускоренных переносов. Схема формирования суммы выдает сигналы разрядных сумм. Схема ускоренных переносов вырабатывает сигналы переноса одновременно во всех разрядах.

Двоично-десятичные сумматоры.При обработке больших массивов десятичных чисел значительная часть времени расходуется на перевод чисел из одной системы счисления в другую. И этом случае целесообразно выполнять обработку данных непосредственно в десятичной системе счисления. При этом для представления десятичных чисел используют различные двоично-десятичные коды. Десятичные цифры представляются двоичными тетрадами. Сложение тетрад выполняется с помощью двоично-десятичных сумматоров.

Двоично-десятичный сумматор строится на основе четырехразрядного двоичного сумматора, в котором перенос возникает, если значение суммы равно или больше 16. Но при сложении двух десятичных цифр перенос должен возникать, если их сумма равна или больше 10, поэтому для правильного сложения двоично-десятичных цифр двоичный сумматор дополняется схемой коррекции. Коррекция выполняется для каждой тетрады суммы отдельно. Правила коррекции зависят от используемого двоично-десятичного кода.

Одноразрядный двоично-десятичный сумматор содержит два четырехразрядных двоичных сумматора и схему коррекции. Первый двоичный сумматор выполняет сложение двоично-десятичных чисел. Схема коррекции формирует сигнал коррекции при возникновении переноса из тетрады или появления запрещенной комбинации в тетраде двоичной суммы.

Мультиплексоры.Мультиплексор представляет собой комбинационную схему с несколькими входами и одним выходом. Входы мультиплексора делятся па информационные и управляющие (адресные). Мультиплексор передает данные с одного из информационных входов на выход. Номер (адрес) подключаемого входазадается на управляющих входах Мультиплексор с k управляющими входами может иметь до 2k информационных входов. Для выбора подключаемого входа используется дешифратор.

Демультиплексоры.Демультиплексор представляет собой комбинационную схему с одним информационным входом, несколькими управляющими (адресными) входами и несколькими выходами. Демультиплексор передает сигнал с информационного входа на один из выходов, номер (адрес) которого задается сигналом на адресных входах. Таким образом, демультиплексор выполняет функцию, обратную но отношению к функции мультиплексора. Так как мультиплексор и демультиплексор выполняют функции, связанные с выбором одного из входов или выходов, их называют также селекторами. Максимальное число выходов демультиплексора составляет 2k, где А число адресных входов.

Регистры.Регистры предназначены для приема, временного хранения и выдачи данных. Чаще всего данные сохраняются в регистре на время выполнения одной или нескольких машинных команд. Кроме храпения данных регистры могут выполнять и другие операции (сдвиг данных, логические операции). Основу регистра составляют триггеры, число которых равно разрядности хранимых данных.

Данные из регистра с параллельной записью и входом установки в состояние «0» могут быть выданы в прямом или обратном (инверсном) коде.

Для выдачи данных из регистра в прямом или обратном коде подается соответствующий управляющий сигнал. Данные обычно выдаются из одного регистра и одновременно принимаются в другой.

| Передача данных между регистрами может выполняться как прямо, т.е. без изменения номеров разрядов, так и со сдвигом влево или вправо на один или несколько разрядов.

|

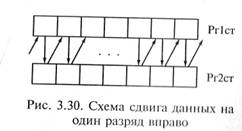

Для сдвига информации и пределах одного регистра используются сдвигающие регистры. Сложность сдвига заключается в том, что каждый разряд регистра должен одновременно принять новую и передать старую информацию. Для устойчивой работы сдвигающего регистра в каждом разряде используют два однотактных триггера или один двухтактный, т.е. сдвигающий регистр фактически состоит из двух регистров.

Сдвигающий регистр представляет собой сдвоенный регистр и состоит из регистров первой (Рг1ст) и второй (Рг2ст) ступеней, между которыми производится обмен данными.

Счетчики.Счетчики предназначены для подсчета числа входных сигналов. Обычно входными сигналами являются импульсы напряжения. Результат счета – это число, представленное в двоичной или двоично-десятичной системе счисления.

В зависимости от направления счета счетчики могут быть суммирующими, вычитающими и реверсивными. Суммирующие счетчики при поступлении каждого входного импульса увеличивают показания на единицу, вычитающие — уменьшают. Реверсивной счетчики могут работать как в режиме суммирования, так и в режиме вычитания.. Счетчики построены на двухтактных триггерах с дополнительными входами для установки счетчика в начальное состояние

В суммирующем и вычитающем счетчиках входной сигнал (и худшем случае) должен последовательно пройти через все триггеры. Такие счетчики называются счетчиками с последовательными переносами. Для повышения быстродействия используют схемы со сквозными или параллельными переносами.

Задание к практической работе

1 Изучить определение подсистемы и выбор кабелей подсистемы;

2 Ответить на контрольные вопросы.

Контрольные вопросы

1. Что представляет собой информация, хранящаяся в оперативной памяти?

2. Что понимают под сообщением?

3. Что служит алфавитом компьютера? Какие символы он содержит?

4. Дайте определение биту. Что такое байт? Сколько в нем бит?

5. Какова длина машинного слова современного компьютера? Какова длина команды в персональном компьютере?

6. Опишите состав процессора персонального компьютера.

7. Какие устройства входят в состав памяти машины? Что такое ПЗУ, ОЗУ, ВЗУ?

8.Что представляет собой BIOS и где находится эта программа?

9.Как производится начальная загрузка персонального компьютера?

10.Опишите действия, производимые в персональном компьютере при его включении.

11. Расскажите о назначении триггера, счетчика, регистра.

12. Каков состав ПО компьютера?

13. Как можно определить производительность и надежность компьютера?

14. Какие существуют методы повышения надежности компьютера?

15. Как добиться объединения ресурсов отдельных компьютеров? С какой целью производится такое объединение?

16. Когда и с какой целью были разработаны ЛВС?

17.Перечислите составные части компьютера в порядке уменьшения функциональной сложности.

18.Чем различаются узлы комбинационного и накаливающего типов?

19.Что такое логический элемент?

20.Что такое функционально полная система логических элементов?

21.Что такое состояние триггера?

22.Почему триггер имеет два устойчивых состояния?

23.Чем различаются асинхронный и синхронный триггеры?

24.В каких случаях используются двухтактные триггеры?

25.Что такое дешифратор?

26. Сколько входов и выходов имеет одноразрядный сумматор?

27. Почему для сложения тетрад двоично-десятичных чисел нельзя использовать обычный двоичный сумматор?

28. Как получить ДК отрицательного двоично-десятичного числа?

29. Для чего используют мультиплексоры?

30. Из каких элементов состоит регистр?

31.Почему для сдвига данных используют двухтактные триггеры?

32.В чем состоит отличие схем суммирующего и вычитающего счетчиков?