Экспериментальная часть. Моделирование комбинационных устройств

Моделирование комбинационных устройств

Цель работы – изучение форм представления чисел в цифровых устройствах и исследование схем комбинационных цифровых устройств – дешифраторов, мультиплексоров и сумматоров.

Рабочее задание

Задание

1.1 Перевести десятичное число, равное вашему номеру в журнале плюс десять, в следующие системы счисления: двоичную, восьмеричную, шестнадцатеричную.

1.2 Разработать и начертить схему электрическую функциональную полного линейного дешифратора двоичного кода в десятичный на три входа с использованием базовых логических элементов. Нарисовать временные диаграммы его работы.

1.3 Разработать и начертить схему электрическую функциональную мультиплексора на восемь входов с использованием базовых логических элементов. Нарисовать временные диаграммы его работы.

1.4 Разработать и начертить схему электрическую функциональную трехразрядного сумматора с последовательным переносом с использованием полусумматоров. Нарисовать временные диаграммы его работы.

Экспериментальная часть

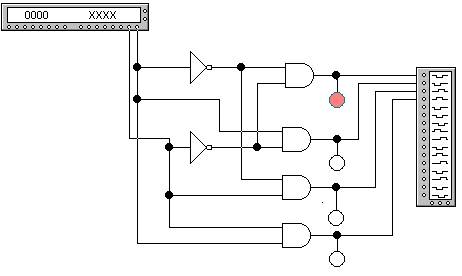

2.1 Смоделировать линейный дешифратор, разработанный в п. 1.2, в среде Electronics Workbench. Пример моделирования графической схемы линейного дешифратора двоичного кода в десятичный код с двумя входами в программе Electronics Workbench приведен на рисунке 1.

Для имитации работы спроектированной схемы подключить ее входы к генератору слов Word Generation, включив его в циклическом режиме Sycle.

2.2 Получить временные диаграммы выходных сигналов дешифратора на экране логического анализатора Logic Analizer. Убедиться в правильной работе шифратора по состоянию логических пробников на ее выходах, заполнив таблицу истинности.

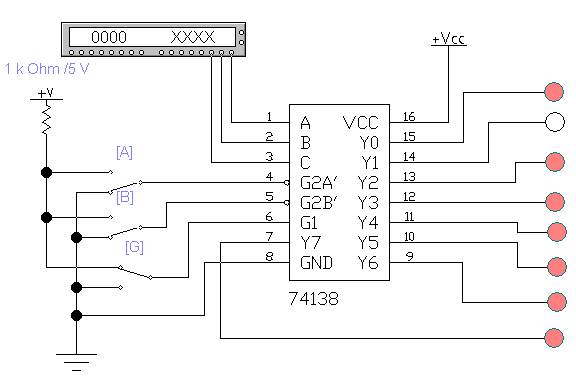

2.3 Собрать схему рисунок 2 и исследовать линейный дешифратор двоичного кода в десятичный на три входа в среде Electronics Workbench с использованием гибридной интегральной микросхемы (ГИС) 74138.

Чтобы посмотреть назначение выводов микросхемы, щелкните по ней и выберите команду Help из контекстного меню.

Установить генератор слов в пошаговом режиме Step. С помощью соответствующих ключей задать следующие состояния управляющих входов микросхемы: G1=1, G2A=G2B=0. Убедиться в правильной работе шифратора по состоянию логических пробников на его выходах и составьте соответствующую таблицу истинности.

Рисунок 1

Рисунок 2

2.4 Смоделировать мультиплексор, разработанный в п. 1.3, в среде Electronics Workbench. Для имитации работы спроектированной схемы подключить ее адресные входы к генератору слов Word Generation, включив его в ручном режиме Step. Задать с помощью ключей управляющий код на шине данных D, соответствующий заданному преподавателем номеру варианта.

2.5 Получить временные диаграммы информационных, адресных и выходных сигналов мультиплексора на экране логического анализатора Logic Analizer.

2.6 Повторить п.п. 2.4-2.5, используя в качестве мультиплексора ГИС 74151.

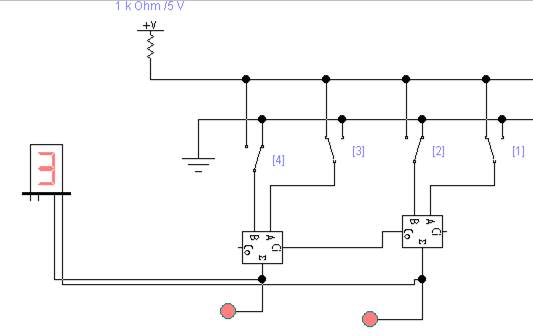

2.7 Смоделировать трехразрядный сумматор, разработанный в п. 1.4, в среде Electronics Workbench. Пример моделирования графической схемы двухразрядный сумматор в программе Electronics Workbench приведен на рисунке 3.

Рисунок 3

Поочередно подавая все возможные комбинации входных сигналов с помощью соответствующих ключей, убедиться в правильной работе сумматора по состоянию логических пробников на его выходах и наблюдая за изменением показаний Decoded Seven-Segment Display (семисегментного индикатора с двоично-десятичным дешифратором на входе), подключенного к его выходам. Составить соответствующую таблицу истинности.