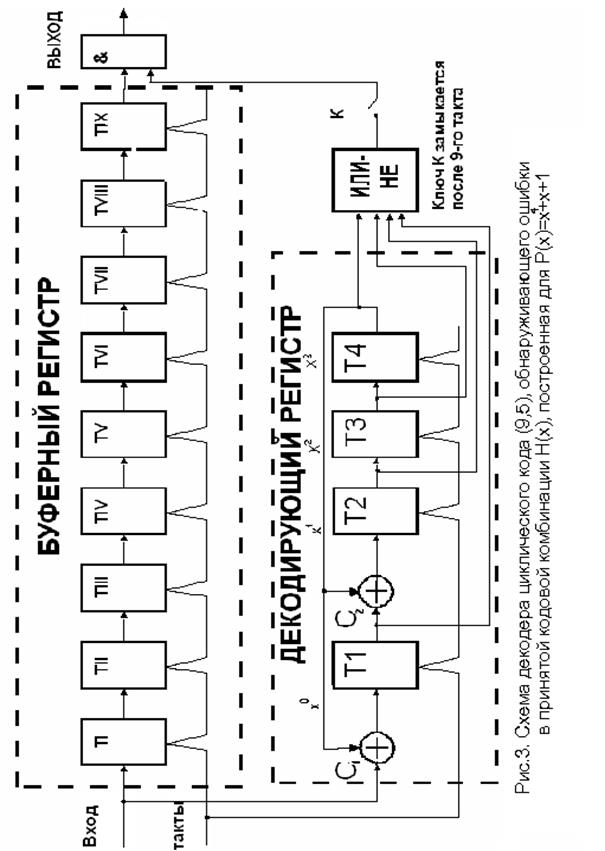

Декодирующее устройство циклического кода (9,5), обеспечивающее обнаружение ошибок

Структурная схема декодера, точнее- его декодирующего регистра, строится по тем же правилам, что и кодера. В состав декодера циклического кода (9,5), обнаруживающего все однократные и двукратные, а также ряд ошибок более высокой кратности в принятой кодовой комбинации Н(х), входят: буферный регистр на 9 разрядов, декодирующий регистр (регистр-делитель), схема ИЛИ–НЕ, схема И, а также – управляющее устройство, замыкающее ключ К после 9го такта (на схеме устройство не показано) (рис.3). На вход декодирующего регистра поступает кодовая комбинация H(x), которая делится на порождающий многочлен P(x).По окончании деления, после 9ти тактов, в триггерах Т1¸Т4 декодирующего регистра декодера записывается и остаток от деления. Если при этом хотя бы один из триггеров Т1¸Т4 находится в единичном состоянии, то это означает, что в принятой кодовой комбинации Н(х) имеется ошибка. Для обнаружения ошибки деление продолжается до 14го такта включительно, но уже “быстрыми” тактовыми импульсами  и на каждом из этих тактов сигналы с выходов триггеров Т1¸Т4 поступают на вход схемы ИЛИ–НЕ. На выходе схемы ИЛИ–НЕ формируется нулевой сигнал, который при замкнутом ключе К поступает на второй вход схемы И. На первый же вход этой схемы И поступает кодовая комбинация Н(х) из буферного регистра декодера циклического кода. Под действием нулевого сигнала с выхода схемы ИЛИ-НЕ схема И запирается и кодовая комбинация Н(х) не поступает из буферного регистра на выход схемы декодера.

и на каждом из этих тактов сигналы с выходов триггеров Т1¸Т4 поступают на вход схемы ИЛИ–НЕ. На выходе схемы ИЛИ–НЕ формируется нулевой сигнал, который при замкнутом ключе К поступает на второй вход схемы И. На первый же вход этой схемы И поступает кодовая комбинация Н(х) из буферного регистра декодера циклического кода. Под действием нулевого сигнала с выхода схемы ИЛИ-НЕ схема И запирается и кодовая комбинация Н(х) не поступает из буферного регистра на выход схемы декодера.

Если же все триггеры Т1¸Т4 декодирующего регистра декодера обнулены после 9го такта, то на выходе схемы ИЛИ–НЕ с 10го по 14й такт имеет место единичный сигнал. Тогда схема И пропускает на выход декодера безошибочно принятую (или с необнаруженными ошибками) кодовую комбинацию из буферного регистра, причем потребителю направляются первые пять разрядов, составляющих информационную кодовую комбинацию G(х).

Наглядной иллюстрацией работы декодирующего регистра декодера могут служить таблицы состояний его триггеров. В качестве примера такие таблицы даны для комбинации циклического кода F(х)=101101111 в случае, когда ошибок нет (табл.2); и в случае, когда ошибка произошла во 2ом разряде (табл.3); - во 2м и 3м разрядах (табл.4);- в 1м , 3м и 5м разрядах (табл.5) и- в 1м ,4м и 5м разрядах (табл.6).

H(x)=101101111; E(x)=000000000 Таблица 2

| Такты(1-9) и “быстрые” такты (10-14) | Информация на входе декодера Н(х) | Состояние триггеров декодирующего регистра |  Информация на Информация на выходе схемы выходе декодера ИЛИ-НЕ после 9-го такта Информация на Информация на выходе схемы выходе декодера ИЛИ-НЕ после 9-го такта | ||||

| Т1 | Т2 | Т3 | Т4 | ||||

| |||||||

| – | |||||||

| – | |||||||

| – | |||||||

| – | |||||||

| – |

Таким образом, как видно из табл.2, в случае отсутствия ошибок в принятой кодовой комбинации H(x), на выходе декодера формируется пятиразрядная кодовая комбинация G(x).

Примечание.После записи входной кодовой комбинации в буферный регистр, на вход кодера, с 10ого по 14й такты, включительно, поступает логический ноль.

H(x)=111101111; E(x)=010000000 Таблица 3

| Такты(1-9) и “быстрые” такты (10-14) | Информация на входе декодера Н(х) | Состояние триггеров декодирующего регистра |  Информация на Информация на выходе схемы выходе декодера ИЛИ-НЕ после 9-го такта Информация на Информация на выходе схемы выходе декодера ИЛИ-НЕ после 9-го такта | ||||

| Т1 | Т2 | Т3 | Т4 | ||||

| |||||||

1 1 | |||||||

| – | – | ||||||

| – | – | ||||||

| – | – | ||||||

| – | – | ||||||

| – | – |

Итак, как видно из табл.3, декодер обнаруживает ошибку во 2ом разряде принятой кодовой комбинации H(x) (см. комбинацию синдрома ошибки S(x)=1011, зафиксированную на 9ом такте в декодирующем регистре), и блокирует выдачу информации потребителю из буферного регистра.

Примечание.Горизонтальная стрелка в таблице (здесь и в последующих таблицах) указывает направление от старшего к младшему разряду кодовой комбинации.

H(x) = 110101111; E(x) = 011000000 Таблица 4

| Такты(1-9) и “быстрые” такты (10-14) | Информация на входе декодера Н(х) | Состояние триггеров декодирующего регистра |  Информация на Информация на выходе схемы выходе декодера ИЛИ-НЕ после 9-го такта Информация на Информация на выходе схемы выходе декодера ИЛИ-НЕ после 9-го такта | ||||

| Т1 | Т2 | Т3 | Т4 | ||||

0 0 |   | ||||||

1 1 | |||||||

| – | – | ||||||

| – | – | ||||||

| – | – | ||||||

| – | – | ||||||

| – | – |

Из табл.4 следует, что декодер обнаруживает двукратную ошибку в принятой кодовой комбинации H(x) и блокирует выдачу информации потребителю из буферного регистра.

H(x)=000111111; E(x)=101010000 Таблица 5

| Такты(1-9) и “быстрые” такты (10-14) | Информация на входе декодера Н(х) | Состояние триггеров декодирующего регистра |  Информация на Информация на выходе схемы выходе декодера ИЛИ-НЕ после 9-го такта Информация на Информация на выходе схемы выходе декодера ИЛИ-НЕ после 9-го такта | ||||

| Т1 | Т2 | Т3 | Т4 | ||||

0 0 |   | ||||||

0 0 | |||||||

| – | – | ||||||

| – | – | ||||||

| – | – | ||||||

| – | – | ||||||

| – | – |

Как видно из табл.5, декодер обнаруживает данную трехкратную ошибку в принятой кодовой комбинации H(x) и блокирует выдачу информации потребителю из буферного регистра.

H(x)= 001011111; E(x)= 100110000 Таблица 6

|

| Такты(1-9) и “быстрые” такты (10-14) | Информация на входе декодера Н(х) | Состояние триггеров декодирующего регистра | Информация на Информация на выходе схемы выходе декодера ИЛИ-НЕ после 9-го такта | ||||

| Т1 | Т2 | Т3 | Т4 | ||||

0 0 |  |  | |||||

9 9 | |||||||

| – | |||||||

| – | |||||||

| – | |||||||

| – | |||||||

| – |

Таким образом, представленные в табл.6 данные свидетельствуют о том, что декодер не в состоянии обнаружить указанную трехкратную ошибку в принятой кодовой комбинации H(x) и выдаёт потребителю кодовую комбинацию со всеми ошибками, т.е. комбинацию 00101.