Счетчики по mod M. Реверсивные счетчики. Синтез последовательных схем

Счётчик числа импульсов — устройство, на выходах которого получается двоичный (двоично-десятичный) код, определяемый числом поступивших импульсов. Счётчики могут строиться на T-триггерах. Основной параметр счётчика — модуль счёта — максимальное число единичных сигналов, которое может быть сосчитано счётчиком. Счётчики обозначают через СТ (от англ. counter).

Счётчики классифицируют:

- по числу устойчивых состояний триггеров: на двоичных триггерах, на троичных триггерах, на n-ичных триггерах

- по модулю счёта: двоично-десятичные (декада): двоичные, с произвольным постоянным модулем счёта, с переменным модулем счёта;

- по направлению счёта: суммирующие, вычитающие, реверсивные;

- по способу формирования внутренних связей: с последовательным переносом, с параллельным переносом, с комбинированным переносом; кольцевые;

- по способу переключения триггера: синхронные; асинхронные.

Счетчик (Сч) - последовательностная схема, преобразующая поступающие на вход импульсы в код Q, пропорциональный их количеству. Большинство счетчиков снабжено выходом переноса CR. Для двоичного и двоично-десятичного кода, как впрочем и для других систем счисления, справедливы следующие соотношения:

- Q = (D + SUM(C)) mod M

- CR = (D + SUM(C)) \ M

В этих формулах: Q - код на выходах счетчика, D - начальное значение записанное в счетчик, SUM(C) - сумма импульсов поступивших на вход в процессе счета и M - модуль счета или число различных состояний счетчика (число импульсов поступивших на счетный вход, после которых счетчик возвращается в исходное состояние), CR - число импульсов переноса, возникающих при возврате счетчика в исходное состояние на одноименном выходе, mod - операция нахождения остатка при делении на M, \ - операция целочисленного деления . Если D = 0 и SUM(C) < M, то очевидно, что Q = SUM(C) и CR = 0. C приходом каждого M-ного импульса счетчик возвращается в исходное состояние.

Пример: пусть D =17, SUM(C) = 9, M = 8, тогда Q = 26 mod 8 = 2, а CR = 3.

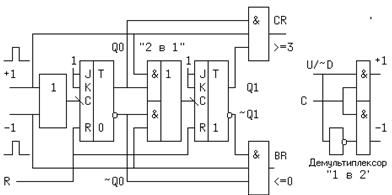

Реверсивный счетчик. Схема двухразрядного счетчика с общим входом сброса R, выходом переноса CR при суммировании и выходом переноса BR при вычитании приведена на рис. внизу.

Предположим, что начальное значение кода равно 2 (Q1 = 1 и Q0 = 0). Рассмотрим режим суммирования, когда на входе "-1" - действует ноль, а на вход "+1" приходит импульс. Отрицательный фронт входного импульса не пройдет через верхний канал мультиплексора "2 в 1", выполненного на элементе И-ИЛИ-НЕ, этому препятствует старое значение Q0=0. На входах нижнего канала действует конъюнкция единицы (~Q0 = 1) и нуля. Поэтому сигнал на выходе мультиплексора равен нулю и триггер T1 сохраняет старое значение.Через время, равное задержке элемента ИЛИ отрицательный фронт поступит на счетный вход триггера T0, и еще через время задержки триггера на его выходах установится новое значение Q0 = 1 (~Q0 = 0). При этом верхний канал открывается для прохождения отрицательного фронта счетного импульса, но т.к. длительность фронта t1,0 значительно меньше суммарного времени задержки tзд = tзд.р.ИЛИ + tзд.р.триггера, на входах "+1" и "-1" к этому времени действуют нули и выходной сигнал мультиплексора по прежнему равен 0. Триггер T1 остается в прежнем состоянии. Новый код на выходах счетчика увеличился на 1 и стал равен Q1Q0 = 11 = 3, до следующего импульса.

Рассмотрим режим вычитания, когда на входе "+1" - действует ноль, а на вход "-1" приходит импульс. Отрицательный фронт входного импульса беспрепятственно пройдет через нижний канал мультиплексора, т.к. ~Q0 = 1 и переключит триггер T1. Спустя время tзд новый код появится и на выходах триггера T0, но отрицательный перепад c выхода ~Q0 не пройдет на счетный вход триггера T1, по причине того, что сигнал на входе "-1" к этому времени уже равен нулю. Старый код 10 на выходах счетчика сменился кодом 01, т.е. уменьшился на 1.

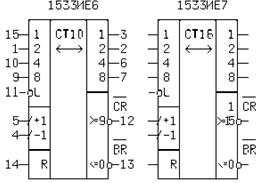

Примерно так выполнены счетчики типа 1533ИЕ6 и 1533ИЕ7, с дополнительным асинхронным входом ~L параллельной записи начального кода. Их обозначения приведены на рисунке.

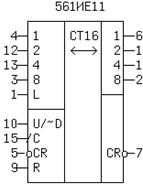

В некоторых счетчиках предпочтительней иметь один тактовый вход и вход управления направлением счета. Для этого к входам "+1" и "-1" подключают демультиплексор "1 в 2". В этом случае, если управляющий сигнал U/~D = (Up/~Down) = 1, тактовые импульсы C поступают на вход суммирования, а если он равен нулю - на вход вычитания. Счетчик такого типа приведен на рисунке внизу.

Основное преимущество счетчиков последовательного типа – простота схемы. Увеличение разрядности достигается подключением дополнительных триггеров к выходу последнего триггера. В суммирующем счетчике каждый входной импульс увеличивает на единицу число, записанное в счетчик. В вычитающем счетчике - каждый входной импульс уменьшает на единицу число, записанное в счетчик.