Основные узлы и функциональные блоки

Регистр сдвига. Регистр сдвига потребуется для преобразования последовательной передачи данных в параллельную передачу и наоборот. Эта операция характерна для физического уровня.

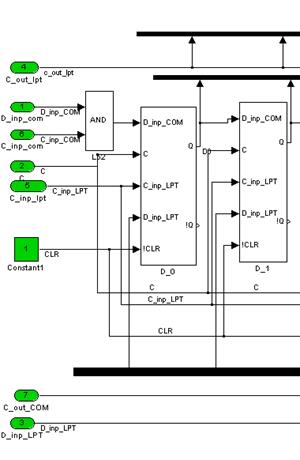

Рассмотрим пример создания универсального регистра. Пусть регистр обеспечивает ввод параллельных данных по входному порту D_inp_LPT, последовательных - по порту D_inp_COM, выходные порты соответственно позволяют снимать параллельные данные D_out_LPT и последовательные D_out_COM. Размер регистра принимаем 11 бит (по количеству бит одного символа, передаваемого в линии связи). Для управления работой регистра предусмотрены входы С_out_COM, C_out_LPT, C_inp_COM и С_inp_LPT. Каждый из перечисленных входов разрешает запись или чтение соответствующего порта данных. Сигнал синхронизации обозначим С. В качестве элемента памяти для хранения одного бита используем синхронизируемый D-триггер (D flip-flop block), модель которого приведена на рис.17.

Рассмотрим пример создания универсального регистра. Пусть регистр обеспечивает ввод параллельных данных по входному порту D_inp_LPT, последовательных - по порту D_inp_COM, выходные порты соответственно позволяют снимать параллельные данные D_out_LPT и последовательные D_out_COM. Размер регистра принимаем 11 бит (по количеству бит одного символа, передаваемого в линии связи). Для управления работой регистра предусмотрены входы С_out_COM, C_out_LPT, C_inp_COM и С_inp_LPT. Каждый из перечисленных входов разрешает запись или чтение соответствующего порта данных. Сигнал синхронизации обозначим С. В качестве элемента памяти для хранения одного бита используем синхронизируемый D-триггер (D flip-flop block), модель которого приведена на рис.17.

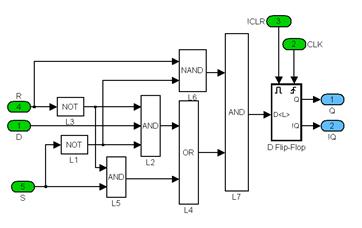

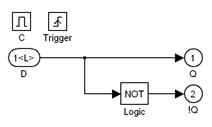

Внутренняя схема модели D-триггера представляет собой подсистему, имеющую два управляющих входа С (Enable) и Trigger. Для упрощения ввода параллельных данных дополним D-триггер установочными входами R и S. Желательно, что бы установочные входы работали независимо от входа синхронизации, но на первом этапе они выполнены синхронизируемыми (см. рис. 17 б).

а) б)

а) б)

Рис.17. Схема модели D-триггера

а – внутренняя схема, б – организация синхронизируемых R-S-входов

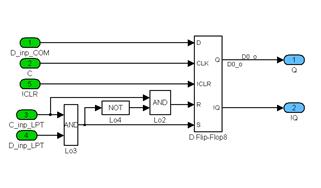

Подключение внешних информационных входов к R_S_D триггеру и образование ячейки регистра приведено на рис. 18 а). На рис. 18 б) показан фрагмент внутренней схемы регистра сдвига, построенного из полученных ячеек памяти. На входы !CLR всех ячеек подается постоянный разрешающий сигнал. Этот сигнал поступает на управляющий вход «С» модели D-триггера (см. рис. 17 а). Параллельные данные поступают на вход D_inp_LPT и демультиплексором распределяются по входам ячеек D_inp_LPT. Последовательные данные поступают на вход D_inp_COM первой ячейки регистра. Все последующие ячейки получают последовательные данные с Q-выходов предыдущих ячеек. Параллельный выход D_out_LPT образуется мультиплексором, подключенным к Q-выходам всех ячеек. Последовательный выход D_out_COM представляется Q-выходом последней ячейки. Управляющие входы регистра через логические схемы И (AND) контролируют прохождение информационных сигналов.

а) б)

а) б)

Рис. 18. Сдвигающий регистр

а – внутренняя схема ячейки регистра, б – фрагмент внутренней схемы регистра сдвига,

Для получения регистра, преобразующего параллельный код на входе, в последовательность бит на выходе, часть управляющих и информационных входов внутри схемы регистра подключаются к постоянным логическим сигналам 1 и 0. Таким образом, получен внешний вид модели регистра сдвига, примененного в модели физического уровня передающей станции.

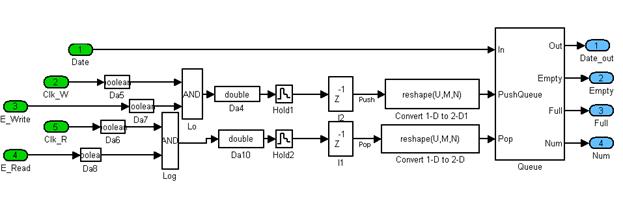

Очередь (Queue). Очередь может быть применена для организации взаимодействия двух частей модели функционирующих с различными частотами синхронизации (в общем случае не кратными друг другу). Библиотечный элемент Queue дополняется управляющими портами разрешения на запись E_Write и разрешения на чтение E_Read (рис. 19). Дополнительные преобразования типов данных потребовались для согласования управляющих сигналов с данными. Задержка на один такт введена для обеспечения считывания и записи в очередь после установления входных данных Date. Выходные порты с предупреждающими сигналами об опустошении очереди (Empty) и ее заполнении (Full) предусмотрены для последующей организации управления очередью. Порт с показаниями количества записей в очереди (Num) установлен для наблюдения за состоянием очереди в процессе отладки.

Рис. 19. Управляющие входы блока очередь

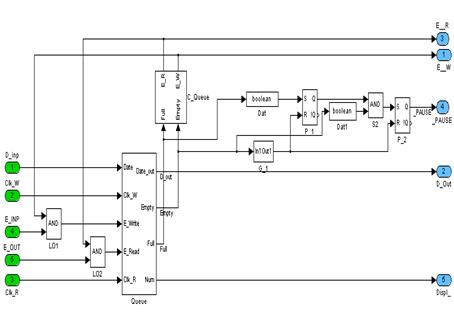

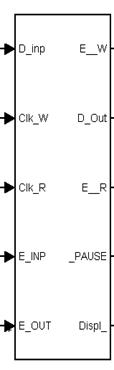

На рис. 20 показано использование очереди для организации следующего алгоритма. Входные данные записываются в очередь с частотой, определяемой портом clk_W. Разрешение на запись дается лишь при условии, что перед началом записи очередь опустошена. После заполнения очереди разрешение на запись снимается и выставляется разрешение на чтение E_R. Чтение из очереди производится с частотой, задаваемой портом clk_R. После опустошения очереди разрешение на чтение снимается и выставляется разрешение на запись E_W. Указанный алгоритм обеспечен блоком управления очередью C_Queue и логическими схемами LO1, LO2. Дополнительный порт _Pause выдает активный сигнал после завершения цикла запись-чтение очереди, что может использоваться для генерации сигнала паузы в линию связи.

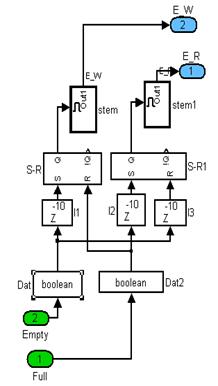

Блок управления очередью приведен на рис.21 а). Он представляет собой триггерные схемы, фиксирующие моменты опустошения и заполнения очереди. Временные задержки I1, I2, I3 введены для согласования работы блока с внешней схемой. Внешний вид построенной системы очередь приведен на рис. 21 б).

Рис. 20. Управление последовательностью записи-чтения очереди

а) б)

Рис. 21 Подсистема очередь

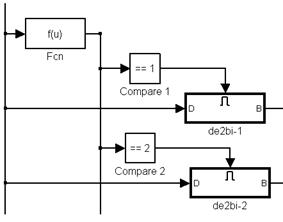

а – блок управления записью-чтением очереди, б – внешний вид подсистемы очередь Буфер (buffer). Буфер эффективен для преобразования входного потока в наборы данных, а также как средство хранения этих данных. Рассмотрим применение буфера для выделения из потока пронумерованных байт данных с фиксированными номерами. На рис. 22 приведено изображение рассматриваемой подсистемы Buf. Пусть система предназначена для выборки из входного потока наборов данных (D_inp) по их номерам (Indx). Для простоты рассмотрен случай, когда требуется выбрать два первых набора. Внутренняя схема подсистемы (рис.23) содержит два компаратора Compare1 и Compare 2, которые выбирают требуемые наборы данных. При срабатывании соответствующего компаратора разрешается работа контролируемого им буфера, в который и записываются выбранные данные. Записанные в буферы данные сохраняются для обеспечения их дальнейшей обработки, например, объединения в один массив блоком cat.

а – блок управления записью-чтением очереди, б – внешний вид подсистемы очередь Буфер (buffer). Буфер эффективен для преобразования входного потока в наборы данных, а также как средство хранения этих данных. Рассмотрим применение буфера для выделения из потока пронумерованных байт данных с фиксированными номерами. На рис. 22 приведено изображение рассматриваемой подсистемы Buf. Пусть система предназначена для выборки из входного потока наборов данных (D_inp) по их номерам (Indx). Для простоты рассмотрен случай, когда требуется выбрать два первых набора. Внутренняя схема подсистемы (рис.23) содержит два компаратора Compare1 и Compare 2, которые выбирают требуемые наборы данных. При срабатывании соответствующего компаратора разрешается работа контролируемого им буфера, в который и записываются выбранные данные. Записанные в буферы данные сохраняются для обеспечения их дальнейшей обработки, например, объединения в один массив блоком cat.

Рис. 23. Набор буферов для хранения данных

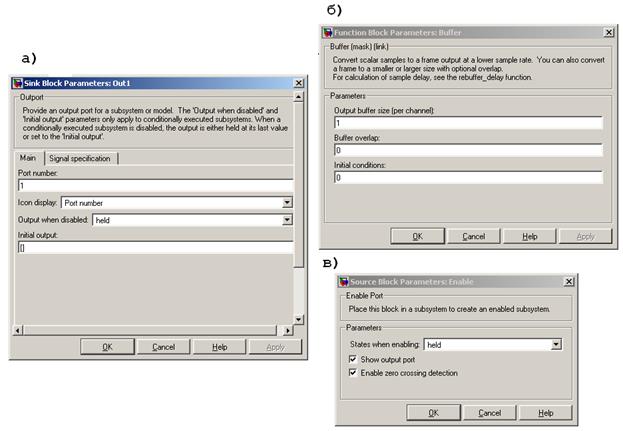

Элементы Bufer_1 и Bufer_2 представляют собой Enable-подсистемы (рис. 24) и содержат управляющий вход Enable, входной In1 и выходной Out1 порты, а также собственно буфер Buffer. Окна настройки буфера и его портов приведены на рис. 25. Настройка заключается в том, что выходные данные буфера объявляются доступными и после завершения интервала времени, в котором Enable-подсистема была активна. Их значение будет определяться теми данными, которые были введены в буфер в последний момент активности подсистемы (held). Размер буфера принят равным единице. Поскольку в условиях моделирования процессов, идущих с различной тактовой частотой и имеющих различное дискретное время, контролирование заполнения буфера с размером больше единицы затруднительно. Исследование буфера можно выполнить на основе файла buffer_.mdl, находящегося в папке подготовительных материалов проекта.

Элементы Bufer_1 и Bufer_2 представляют собой Enable-подсистемы (рис. 24) и содержат управляющий вход Enable, входной In1 и выходной Out1 порты, а также собственно буфер Buffer. Окна настройки буфера и его портов приведены на рис. 25. Настройка заключается в том, что выходные данные буфера объявляются доступными и после завершения интервала времени, в котором Enable-подсистема была активна. Их значение будет определяться теми данными, которые были введены в буфер в последний момент активности подсистемы (held). Размер буфера принят равным единице. Поскольку в условиях моделирования процессов, идущих с различной тактовой частотой и имеющих различное дискретное время, контролирование заполнения буфера с размером больше единицы затруднительно. Исследование буфера можно выполнить на основе файла buffer_.mdl, находящегося в папке подготовительных материалов проекта.

Рис. 25. Настройка буфера и его портов в Enable-подсистеме

а – настройка выходного порта подсистемы, б – настройка параметров порта,

в – настройка управляющего входа подсистемы

Функции Matlab. Функции Matlab используются при отсутствии требуемых готовых блоков в библиотеке Simulink и других библиотеках. Для применения функций пользователя предусмотрены шаблоны Fcn, и MATLAB Fcn и Embedded MATLAB Function в библиотеке раздела User-Defined Functions (рис.26). Схема для проверки работы блоков имеется в папке подготовительных материалов для курсового проекта (файл Fcns.mdl).

Функции Matlab. Функции Matlab используются при отсутствии требуемых готовых блоков в библиотеке Simulink и других библиотеках. Для применения функций пользователя предусмотрены шаблоны Fcn, и MATLAB Fcn и Embedded MATLAB Function в библиотеке раздела User-Defined Functions (рис.26). Схема для проверки работы блоков имеется в папке подготовительных материалов для курсового проекта (файл Fcns.mdl).

В рассматриваемой системе программирования различают два вида файлов, содержащих программные коды. Модель созданная в среде Simulink, хранится в S-файле. Модель, написанная на языке MATLAB, хранится в M-файле.

Рассмотрим применение блоков, определяемых пользователем для взаимного преобразования бинарного и десятичного представления чисел. Такая задача возникает при формировании контрольной суммы кадра передатчика и при проверке правильности контрольной суммы в приемнике.

Применение блока Fcn в рассмотренном случае нецелесообразно. Поскольку он не сможет возвратить векторную величину (бинарную последовательность).

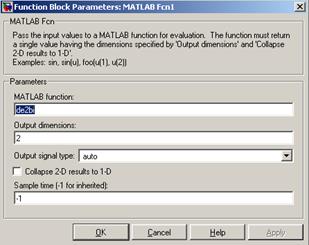

Блок MATLAB Fcn. Применение данного блока требует, что бы кроме указания самой используемой функции и передачи ей параметров, была указана размерность возвращаемого результата. В общем случае размерность может быть не известна заранее, а вычисляется в процессе моделирования.

Одно из решений заключается в применении Enable-блоков. В этом случае при передаче управления такому блоку размерность известна. На рис. 27 приведен фрагмент модели, реализующий рассмотренное решение. В блоке Fcn (рис. 27 г) вычисляется размерность ожидаемого результата преобразования

Expession = ceil(1.4427*log(u+eps)),

где ceil – функция вычисления целого,

u – значение величины, передаваемой на вход блока,

eps - точность вычисления в функциях MATLAB,

log - натуральный логарифм.

Применение в формуле логарифма по основанию 2 вместо натурального логарифма ограничено диагностической системой данного блока, но может быть использовано в блоках типа MATLAB Fcn.

Компараторы Compare 1, Compare 2 передают управления соответствующим триггерным блокам de2bi-1 и de2bi-2, в которых указана (рис.27 б) размерность (Output dimensions=2, для блока de2bi 2) ожидаемых результатов вычисления функции преобразования из десятичного представления числа в бинарную последовательность (MATLAB function=de2bi). Аргументом указанной функции служит входная величина блока (порт D) Справка по данной функции может быть получена в командном окне MATLAB по команде help de2bi.

Блок embedded MATLAB Function. Для использования данного блока необходимо написать текст программы на языке MATLAB. Пример функции op(), возвращающей номер пункта k, выбранного пользователем в меню приведен на рис.28.

а) б)

а) б)

в) г)

в) г)

Рис. 27. Применение функций пользователя

function [k] = op(str1,str2)

str3='КОНТРОЛИРУЕМЫЙ ПУНКТ_:';

str4='ОБЪЕКТ_______________:';

str5=strcat(str3,str2)

str6=strcat(str4,str1)

k=menu(strvcat(str5,str6),'VKL','OTK','CANCEL');

Рис. 28. Текст программы вызова меню

ниже. Этой функции передается название объекта str1 и контролируемого пункта str2. Внутри ее производится формирование сообщения для названия меню и вызов стандартной функции menu(). Наименование пунктов меню передается в качестве аргументов: ‘VKL’, ‘OTK’, ‘CANCEL’.