Комбинационные схемы. Дешифратор. Шифратор. Схемы сравнения

Обработка входной информации Х в выходную Y (см. рис. 2.1) в любых схемах ЭВМ обеспечивается преобразователями или цифровыми автоматами двух видов: комбинационными схемами и схемами с памятью.

Комбинационные схемы – это схемы, у которых выходные сигналы Y = (у1, у2, ..., уm) в любой момент дискретного времени однозначно определяются совокупностью входных сигналов Х = (х1, х2,..., хn), поступающих в тот же момент времени t.

Реализуемый в КС способ обработки информации называется комбинационным потому, что результат обработки зависит только от комбинации входных сигналов и формируется сразу при поступлении входных сигналов. Поэтому одним из достоинств комбинационных схем является их высокое быстродействие. Преобразование информации однозначно описывается логическими функциями вида Y=f(Х).

Логические функции и соответствующие им комбинационные схемы подразделяют на регулярные и нерегулярные структуры.

Регулярные структуры предполагают построение схемы таким образом, что каждый из ее выходов строится по аналогии с предыдущими.

В нерегулярных структурах такая аналогия отсутствует. Примером построения нерегулярной структуры может служить разработка схемы в примере 2.16.

Из регулярных комбинационных схем наиболее распространены дешифраторы, шифраторы, схемы сравнения, комбинационные сумматоры, коммутаторы и др. Рассмотрим принципы построения подобных регулярных структур.

Дешифраторы (ДШ) – это комбинационные схемы с п входами и m =2n выходами. Единичный сигнал, формирующийся на одном из т выходов, однозначно соответствует комбинации входных сигналов. Например, разработка структуры ДШ для п=3 согласно, изложенной ранее, методике позволяет получить таблицу истинности (табл. 3.1).

Таблица 3.1. Таблица истинности дешифратора

| Входы | Выходы | |||||||

| x1 | x2 | x3 | Y0 | Y1 | ... | Y5 | ... | Y7 |

| ... | ... | |||||||

| ... | ... | |||||||

| ... | ... | |||||||

| … | ... | |||||||

| ... | ... | |||||||

| ... | ... | |||||||

| ... | ... | |||||||

| ... | ... |

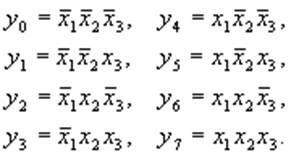

Дешифраторы широко используются в ЭВМ для выбора информации по определенному адресу, для расшифровки кода операции и др. Логические зависимости дешифратора:

На рис.3.2 представлены структурная схема ДШ, построенная в базисе (И, НЕ), и ее условное обозначение на принципиальных электрических схемах ЭВМ. Кружочки у линий, выходящих из логических элементов, указывают на инверсию функций, реализуемых элементами.

Рис.3.2.Структурная схема дешифратора (а) и обозначение дешифратора на принципиальных электрических схемах (б)

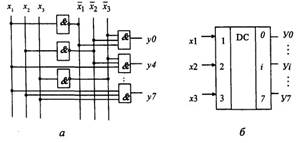

Шифратор (ШР) решает задачу, обратную схемам ДШ, т. е. по номеру входного сигнала формирует однозначную комбинацию выходных сигналов. Пример построения ШР иллюстрируется таблицей истинности (табл. 3.2) и схемами на рис. 3.3.

Таблица 3.2. Таблица истинности шифратора

| Входы | Выходы | ||||||||

| x1 | x2 | x3 | x4 | x5 | x6 | x7 | Y0 | Y1 | Y2 |

| … | … | ||||||||

| … | … | ||||||||

| … | … | ||||||||

| … | … | ||||||||

| … | … | ||||||||

| … | … | ||||||||

| … | … | ||||||||

| … | … |

Логические зависимости:

Рис. 3.3. Структурная схема шифратора (а) и обозначение шифратора на принципиальных электрических схемах (б)

Обратим внимание, что табл. 3.2 и 3.1 во многом похожи, входы и выходы в них поменялись местами. Состояния входов табл. 3.2 содержат только по одному единичному элементу. Другие произвольные комбинации входов недопустимы.

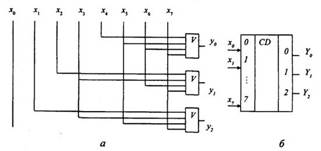

Схемы сравненияили компаратор обычно строятся как поразрядные. Они широко используются и автономно, и в составе более сложных схем, например при построении сумматоров.

Таблица истинности (табл.3.3) отражает логику работы 1-го разряда схемы сравнения при сравнении двух векторов А и В.

Таблица 3.3. Таблица истинности компаратора

| Входы | Выходы | |

| ai | bi | Yi |

Логическая зависимость:

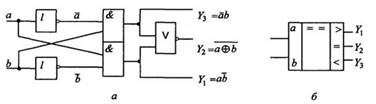

На рис. 3.4. показана структурная схема компаратора:

Рис.3.4. Структурная схема компаратора (а) и обозначение компаратора на принципиальных электрических схемах (б)

На рис. 3.4, помимо выхода Y2, фиксирующего равенство значений разрядов, показаны выходы Y1 и Y3 , соответствующие сигналам «больше» и «меньше».