Перечень используемой литературы

Практическое занятие № 9

Организация оперативной памяти ЭВМ

1 Цель занятия:понять организацию оперативной памяти при увеличении

разрядности и адресности модулей, а так же процесс записи и считывания информации.

Оборудование и программное обеспечение

2.1 Компьютер IBM PC.

2.2 Операционная система Windows-XP и выше.

2.3 Программа Macromedia Flash MX 2004.

Теоретические сведения

Рассмотрим упрощенную структурную схему модуля основной памяти при его матричной организации.

Куб памяти содержит набор запоминающих элементов – ячейки памяти.

Ячейки памяти организованны в матрицы, состоящие из строк и столбцов. Полный адрес ячеек данных включает два компонента – адрес строки и адрес столбца. Адрес ячейки, поступающий в Регистр адреса, например, по 20 разрядным кодовым шинам адреса (КША), делится на две десятиразрядные части, поступающие на Регистр адреса X и Регистр адреса Y.Из этих регистров, коды полуадресов поступают в Дешифраторы Х и У, каждый из которых в соответствии с полученным адресом выбирает одну из 1024 шин (210 = 1024). На пересечении горизонтальной и вертикальной шин будут находится выбираемые ячейки памяти. Таким образом, адресуется 106 (10242 = 1048576) ячеек памяти.

Считываемая или записываемая информация, поступает в Регистр данных, который непосредственно связан с кодовой шиной данных (КШД). Управляющие сигналы, определяющие, какую операцию следует выполнить, поступают по кодовым шинам инструкций (КШИ).

|

Структурная схема модуля оперативной памяти

ОЗУ предназначено для хранения информации (программ и данных) непосредственно участвующих в вычислениях в текущий интервал времени. Основу ОЗУ составляют микросхемы динамической памяти (DRAM). Это большие интегральные схемы, содержащие матрицы полупроводниковых запоминающих элементов – конденсаторов. Наличие заряда в конденсаторе означает «1», отсутствие заряда «0».

Структурная схема микросхемы памяти

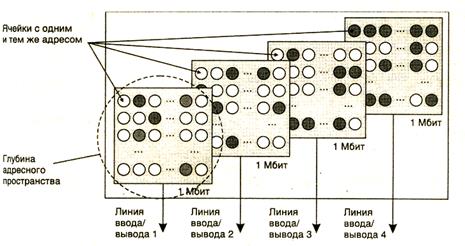

При поступлении на входы микросхемы памяти адреса ячейки производится одновременное чтение (запись) всех ячеек, находящихся по данному адресу, но в различных матрицах. В этом случае одновременно считывается, записывается сразу несколько бит информации. Например, если микросхема имеет 8 линий ввода/вывода (соответственно 8 матриц), то СРU может считывать (записывать) информацию побайтно. Количество линий ввода/вывода определяет разрядность шины ввода/вывода микросхемы. Количество бит информации, которое хранится в ячейках каждой матрицы, называется глубиной адресного пространства микросхемы памяти.

Таким образом, общая емкость микросхемы памяти определяется произведением глубины адресного пространства на количество линий ввода/вывода (разрядов). Например, емкость микросхемы памяти, имеющей глубину адресного пространства 1 Мбайт и 4 линии ввода/вывода (четырехразрядную шину ввода/вывода), составляет 1 Мбайт х 4 = 4 Мбайт. Такая микросхема обозначается 1x4, 1Мх4, хх4400 либо хх4401.

Задание

4.1 Для схемы с увеличенной разрядностью описать режим записи и чтения заполнив соответствующие графы таблицы 1.

4. 2 Для схемы с увеличенным числом ячеек памяти описать режим записи и чтения заполнив соответствующие графы таблицы 1.

4.3 Для схемы с увеличенной разрядностью и адресностью описать режим записи и чтения заполнив соответствующие графы таблицы 1.

Порядок выполнения

5.1 Познакомится с обозначением микросхемы памяти и назначением выводов.

Назначение выводов микросхемы:

– А0, А1, А2, А3 – адресные входы. Разрядность адреса определяется числом ячеек памяти, т.е. максимально возможным числом хранимых в микросхеме памяти слов. Адрес является номером ячейки, к которой идет обращение. Разрядность адреса n и число ячеек N связаны соотношением N=2n .

Микросхема ОЗУ

– CS- вход разрешения или запрета работы микросхемы;

– R/W- вход задающий вид выполняемой операции (при единичном

значении – чтение, при нулевом – запись);

–D0,D1,D2,D3 – входы или выходы для подключения шины данных.

Для микросхемы памяти характерна такая последовательность сигналов. Прежде всего, подается адрес ячейки, которую необходимо выбрать. Затем разрешается работа микросхемы сигналом CS и подается строб чтения/записи W/R (взаимное положение сигналов CS и W/R может быть различным).

5.2 Открыть папку «index». Выбрать пункт «Увеличение разрядности». Используя анимации рассмотреть режимы записи и чтения. Для одного из режимов по указанию преподавателя заполнить соответствующие графы таблицы 1.

5. 3 Выбрать пункт «Увеличение числа ячеек памяти». Используя анимации рассмотреть режимы записи и чтения. Для одного из режимов по указанию преподавателя заполнить соответствующие графы таблицы 1.

5.4 Выбрать пункт «Увеличение разрядности и адресности». По аналогии с предыдущими пунктами заполнить графы таблицы 1.

Содержание отчета

6.1Цель занятия.

6.2 Оборудование и программное обеспечение

6.3 Условное обозначение микросхемы с назначением выводов.

6.4 Заполненная таблица

6.5 Выводы по работе

Контрольные вопросы

7.1 Назначение регистров и дешифраторов в структурной схеме модуля

оперативной памяти.

7.2. Пояснить, что представляет собой куб памяти в структурной схеме модуля оперативной памяти.

7.3. Дать определение разрядности и глубины адресного пространства

микросхемы памяти.

7.4. Дать понятие банка памяти.

7.5. Назначение выводов микросхемы ОЗУ.

7.6 Пояснить включение микросхем для увеличение разрядности.

7.7 Пояснить включение микросхем для увеличение числа ячеек памяти.

7.8 Пояснить включение микросхем для увеличение разрядности и адресности.

Перечень используемой литературы

8.1 Инструкционная карта для выполнения практического занятия

8.2 Конспект теоретического занятия.

8.3 Максимов Н.В., Партыка Т.Л., Попов И.И. Архитектура ЭВМ и вычислительных систем.- Москва –ФОРУМ-ИНФА-М.2006 г.

8.4 Пескова С.А., Кузин А.В. Архитектура ЭВМ. – Москва ФОРУМ-ИНФА-М.

2006 г.

Таблица 1

| Режим | Число микро схем памяти | Разрядность ША//ШД | Код на ША | Код на ШД | Коды на выводах микросхем L1,L2,L3,L4 в которые произошла запись или из которых произошло считывание ( режимы записи 1, 2 и считывания 1, 2 ) | |||||||||||||||||||||||||

| __ CS | А0 А0 | А1 А1 | А2 А2 | А3 А3 | __ CS | А0 А0 | А1 А1 | А2 А2 | А3 А3 | __ W/R | D0 D0 | D1 D1 | D2 D2 | D3 D3 | D0 D0 | D1 D1 | D2 D2 | D3 D3 | ||||||||||||

| Увеличение разрядности кода данных | L1 | L2 | L1 | L2 | ||||||||||||||||||||||||||

| Увеличение числа ячеек памяти | L1 | L2 | L1 | L2 | ||||||||||||||||||||||||||

| Увеличение разрядности и адресности | L1 | L2 | L1 | L2 | ||||||||||||||||||||||||||

| L3 | L4 | L3 | L4 | |||||||||||||||||||||||||||