Студент Кравцов М.С. Группа А-09-08

Исходные данные

1. Емкость ЗУ 8K x 36

2. Тип БИС ЗУ , его организация КР537РУ13Б,

1Кх4; tA(A) ≤ 200 нс

3. Серия микросхем в схемах управления КР1554

4. Шины адреса Раздельно

Данных Общие

5. Входные управляющие сигналы MS,MR/MW

6. Время действия сигналов на шине адреса, 2 такта

на входе MS Tcy

7. Контроль по модулю 2 Есть

8. Температура окружающей среды от -10°С до +50°С

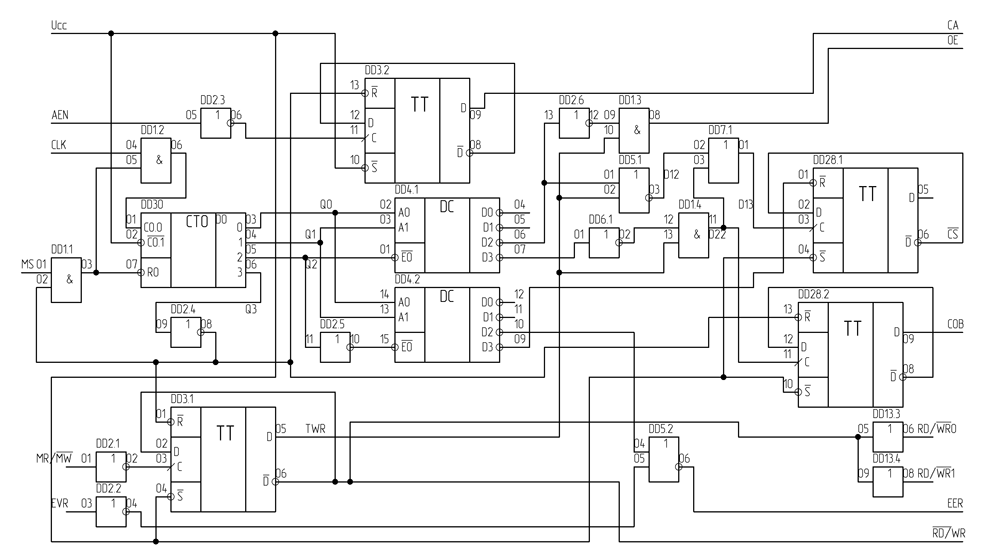

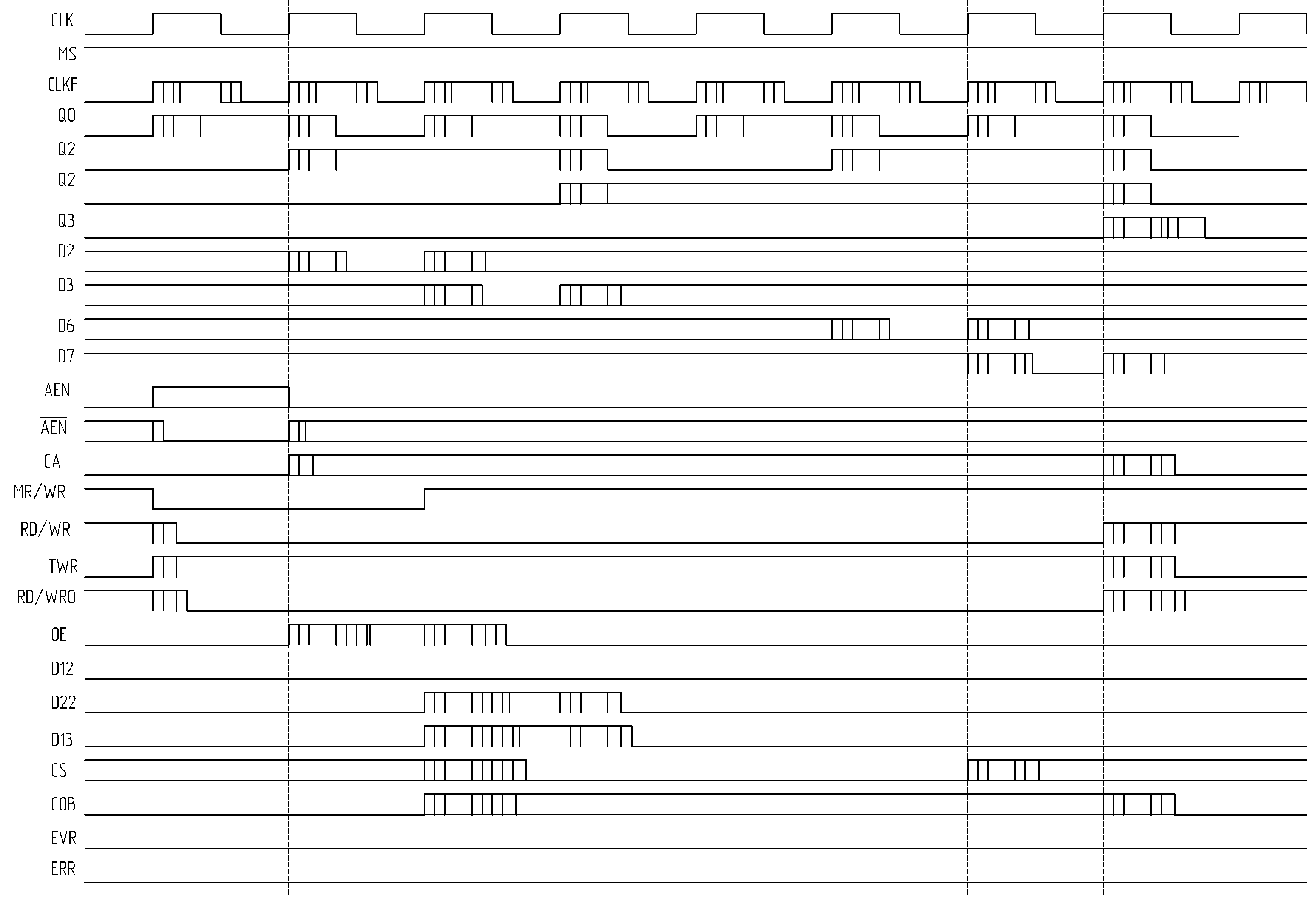

Схема устройства управления, разработанная на 3-м курсе

Его временная диаграммауправления,разработанная на 3-м курсе  ниже

ниже

Студент использовал самостоятельно разработанные функциональные модели микросхем

Текст модели УУ

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity CU is

Port ( CLK : in STD_LOGIC;

Ucc : in STD_LOGIC;

MSm : in STD_LOGIC;

AEN : in STD_LOGIC;

MR_MW : in STD_LOGIC;

EVR : in STD_LOGIC;

CA: inout STD_LOGIC;

OE: out STD_LOGIC;

nCS: inout STD_LOGIC;

COB: inout STD_LOGIC;

CBA : inout STD_LOGIC;

EER: out STD_LOGIC;

nRW: inout STD_LOGIC);

end CU;

architecture Behavioral of CU is

component l2CT port(

C00 : in STD_LOGIC;

nC01 : in STD_LOGIC;

nR0 : in STD_LOGIC;

Q : inout UNSIGNED (3 downto 0));

end component;

component l2DC port (

A : in STD_LOGIC_VECTOR (1 downto 0);

nE0 : in STD_LOGIC;

Ddc : out STD_LOGIC_VECTOR (3 downto 0));

end component;

component Invert_LN1 port (

nin : in STD_LOGIC;

nout : out STD_LOGIC);

end component;

component l2_LI1 port (

i1in : in STD_LOGIC;

i2in : in STD_LOGIC;

nout : out STD_LOGIC);

end component;

component ILI2_LL1 port (

i1in : in STD_LOGIC;

i2in : in STD_LOGIC;

nout : out STD_LOGIC);

end component;

component ILI2N_LE1 port (

i1in : in STD_LOGIC;

i2in : in STD_LOGIC;

nout : out STD_LOGIC);

end component;

component Trig_TM2 port (

nR : in STD_LOGIC;

D : in STD_LOGIC;

C : in STD_LOGIC;

neS : in STD_LOGIC;

Q : inout STD_LOGIC;

nQ : inout STD_LOGIC);

end component;

signal Qf: UNSIGNED (3 downto 0);

signal D1:STD_LOGIC_VECTOR (3 downto 0);

signal D2:STD_LOGIC_VECTOR (3 downto 0);

signal nQf2: STD_LOGIC; --инвертированные выходы счетчика

signal nQf3: STD_LOGIC;

signal MSm1: STD_LOGIC; --после 2и

signal CLK1: STD_LOGIC; --после 2и

signal AEN1: STD_LOGIC; --инвертированное AEN

signal TRnQ1: STD_LOGIC; --выходы триегеров инверсные

signal TRnQ2: STD_LOGIC;

signal TRnQ3: STD_LOGIC;

signal TRnQ4: STD_LOGIC;

signal nMR_MW: STD_LOGIC; --инвертированное MR_MW

signal nEVR: STD_LOGIC; --инвертированное MR_MW

signal TRQ1: STD_LOGIC; --сигнал с q

signal nD12: STD_LOGIC; ----инвертированный 2й выход 1 дешифратора

signal nD13: STD_LOGIC; ----инвертированный 3й выход 1 дешифратора

signal D12: STD_LOGIC; ----см схему

signal D22: STD_LOGIC; ----см схему

signal D13: STD_LOGIC; ----см схему

signal pust1: STD_LOGIC; ----см схему

begin

E1: l2_LI1 port map (MSm,nQf3,MSm1);

E2: l2_LI1 port map (CLK,MSm1,CLK1);

E3: Invert_LN1 port map (AEN,AEN1);

E4: l2CT port map (CLK1,Ucc,MSm1,Qf);

E5: l2DC port map (STD_LOGIC_VECTOR(Qf(1 downto 0)),STD_LOGIC(Qf(2)),D1);

E6: Invert_LN1 port map (STD_LOGIC(Qf(2)),nQf2);

E7: l2DC port map (STD_LOGIC_VECTOR(Qf(1 downto 0)),nQf2,D2);

E8: Invert_LN1 port map (STD_LOGIC(Qf(3)),nQf3);

E9: Trig_TM2 port map (nQf3,TRnQ2,AEN1,Ucc,CA,TRnQ2);

E10: Invert_LN1 port map (MR_MW,nMR_MW);

E11: Invert_LN1 port map (EVR,nEVR);

E12: Trig_TM2 port map (nQf3,nRW,nMR_MW,Ucc,TRQ1,nRW);

E13: Invert_LN1 port map (D1(2),nD12);

E14: Invert_LN1 port map (D1(3),nD13);

E15: ILI2N_LE1 port map (D1(2),TRQ1,D12);

E16: ILI2N_LE1 port map (D2(2),nEVR,EER);

E17: l2_LI1 port map (nD12,TRQ1,OE);

E18: l2_LI1 port map (nD13,TRQ1,D22);

E19: ILI2_LL1 port map (D12,D22,D13);

E20: Trig_TM2 port map (nQf3,TRnQ4,D22,Ucc,COB,TRnQ4);

E21: Trig_TM2 port map (D2(3),nCS,D13,Ucc,pust1,nCS);

E22: Trig_TM2 port map (nQf3,Ucc,nD12,Ucc,pust1,CBA);

end Behavioral;

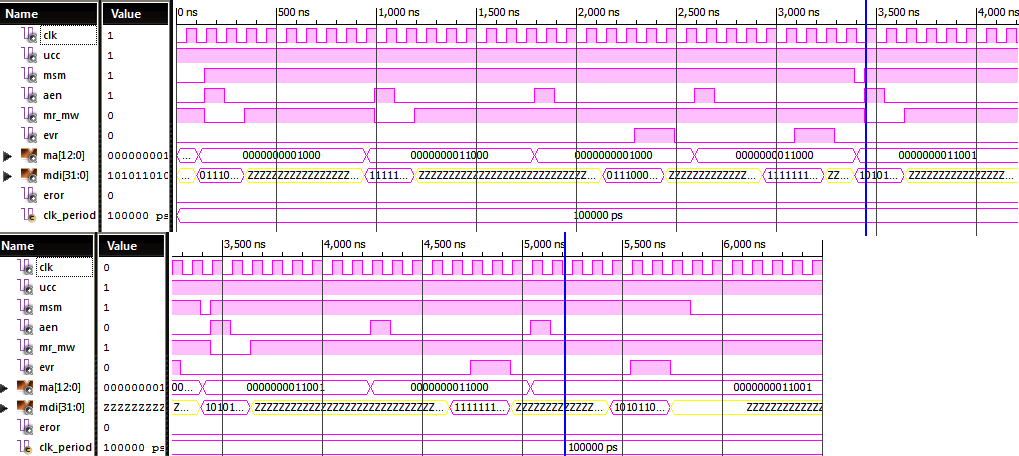

Временная диаграмма режима чтения,полученная при моделировании

Полную верификацию схемы УУ ЗУ можно провести только в составе общей модели ЗУ. Эту работу предполагает выполнение расчетного задания. Но все это можно выполнить заранее, начиная с данной лабораторной работы.

Заключение

Итак, в ходе выполнения лабораторных работ по этому разделу

НАДО.

1. ПАМЯТЬ.Разработать или взять сделанные студентами ранее HDL-модель микросхемы памяти и библиотеки моделей микросхем серий 1533-54 и описать схемы ЗУ на выбранном Вами HDL- VHDL или VERILOG, используя материалы своей курсовой работы по проекту ЗУ 6 семестра .

Модель микросхемы памяти должна включать операторы утверждений, контролирующие нарушения параметров управляющих сигналов (предустановка -удержание).

Построить тест-программу для верификации модели микросхемы памяти и проверить ее работу ( в стандартном режиме и с нарушением временных соотношений) Показать что при нарушении временных соотношений память не работает, а модель выдает соответствующие предупреждения

После этого можно применять модель микросхемы памяти в составе массива микросхем ЗУ

2. Управление. Блок местного управления ЗУ следует описывать структурно-(в графическом редакторе или текстом на VHDL) как схему принципиальную, построенную в элементном базисе K1533-54 – 74.

Если ваш блок УУ, построенный на 3 курсе, работает неверно, в крайнем случае и только по согласованию с преподавателем можно описать заново как автомат ( как это предполагает работа №3 в разделе ПЛИС) и проверив его синтез в базисе плис и добавив предполагаемые задержки микросхем СИС, использовать в модели ЗУ!

Если не хотите применять наши библиотеки К1533-54-74 серий , то вам придется создавать модели этих микросхем самим

3. Расчетное задание –имеются методические материалы по расчетному заданию. Ниже только краткое напоминание о этой работе.

Если емкость памяти в проекте ЗУ превысит предельные размеры памяти доступные ВАШЕЙ МОДЕЛИРУЮЩЕЙ СИСТЕМЕ или емкость ЗУ моделирующей машины(1 бит ЗУ моделируется на VHDL одним байтом ,а на VERILOG 2 битами), придется моделировать часть микросхем памяти ВАШЕГО КП ЗУ.

Построить модель схемы ЗУ и тест-программу для верификации модели своего проекта (включая тестовые наборы воспроизводящие как часть теста ту временную диаграмму ,что ВЫ строили для защиты

своего проекта на 3-м курсе.

Тест ЗУ должен быть полным, самопроверяющимся и включать

как обычные режимы работы чтения - записи ( например

запись - чтение по начальному , конечному и серединному адресу кодов состоящих из всех 0 и всех 1, запись –чтение адресов в эти же ячейки )так и

граничные и запрещенные режимы и режимы с нарушениями

временных соотношений

По временной диаграмме определить время цикла и время выборки (для режима считывания) и сравнить с ожидаемой, полученной на 3 курсе.

Рекомендуется сделать тестирующую программу самопроверяющейся . чтобы в случае отличия результата работы схемы и эталона программа печатала сообщение об ошибке

Провести модельный эксперимент и доказать правильность

своей модели