Лекция 5.2. Аппаратные средства поддержки проектирования и отладки систем реального времени. 162 6 страница

Однако, разработчику весьма полезно знать кроме максимальной и минимально возможную задержку. Однако, для большинства серийно выпускаемых микросхем значение минимальной задержки в ТУ не указано и, следовательно, изготовителем не гарантируется. Опыт работы схемотехника с данными элементами здесь бесполезен, поскольку кривая технологического разброса у разных изготовителей различна и к тому же чувствительна к перестройкам производства, что и иллюстрируют две кривые на рис.1. Поэтому если разработчик аппаратуры использует микросхемы, в паспорте которых не оговорено минимальное значение задержки, то он вынужден полагать минимальное время задержки равным нулю. Никаких юридических оснований считать, что это значение больше нуля, у него нет.

Уровень выхода элемента в течение отрезка времени от минимально возможного до максимально возможного значения задержки, когда фактическое состояние выхода элемента разработчику не известно, называют состоянием неопределенности и обозначают символом х. Состояние х, поступая на входы других логических элементов, может в зависимости от типа элемента порождать на их выходе или определенные состояния 1 или 0, или также неопределенное, обозначаемое X. Поведение логических элементов задается при этом законами уже не двоичной, а одного из видов троичной логики. Соотношения, расширяющие основные функции на третью переменную х, достаточно очевидны:

где х, x1 x2 - неопределенные значения сигналов на входах элементов.

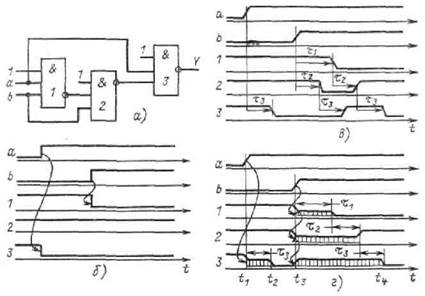

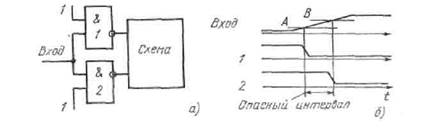

Эффективным средством анализа переходных процессов в схемах являются временные диаграммы. При их построении состояние неопределенности изображают одним из двух способов, которые показаны для элемента И (рис. 2а). Изображение на рис. 2б строже, но менее наглядно; изображение на рис. 2в нагляднее, но может быть спутано с состоянием высокого импеданса элемента, имеющего три состояния выхода.

Рисунок 2.- Способы изображения состояния неопределенности логического элемента

Линии со стрелками обозначают причинно-следственные отношения в цепочке переключений. Линия начинается на фронте, который непосредственно вызывает переключение рассматриваемого элемента и оканчивается стрелкой на фронте выходного сигнала этого элемента. Наличие таких указателей заметно облегчает понимание работы сложных схем.

На рис. 3а показан фрагмент схемы и варианты начертания временных диаграмм переходных процессов. Здесь и в дальнейшем для обозначения выходного сигнала элемента используется номер самого элемента. Диаграмма на рис.3б игнорирует переходные процессы в элементах и схеме. Такие диаграммы применяют, когда основной целью является иллюстрация логических и причинно-следственных отношений, а длительностью переходных процессов по сравнению с интервалами между поступлением сигналов можно пренебречь.

Диаграмма на рис. 3а построена в предположении, что все элементы имеют максимально возможные значения задержки. Эта диаграмма наглядна, поэтому удобна для первого знакомства с поведением сложной схемы. Но она годится лишь для оценки максимальной длительности переходного процесса. Делать по такой диаграмме выводы о состояниях элементов во время переходного процесса нельзя: это лишь один частный случай из множества возможных процессов.

Рисунок 3. - Временные диаграммы переходных процессов:

а - фрагмент схемы; б, в, г - изображение переходных процессов; б - без учета задержек элементов, в - в предположении, что задержки максимальны; г - с использованием состояния неопределенности

Диаграмма рис. 3г учитывает состояния неопределенности элементов в соответствии с (1). Она достаточно строго моделирует поведение схемы при любых комбинациях задержек, допускаемых паспортами элементов. Полезно сравнить диаграммы на рис. 3 в и г, обращая внимание на их расхождения, причиной которых является общность диаграммы г и частность диаграммы в.

Быстрое чтение и особенно построение временных диаграмм требуют некоторой тренировки. Полезно самостоятельно построить несколько вариантов диаграмм, изменяя моменты поступления входных сигналов и соотношения задержек элементов схемы на рис. 3а. Построение диаграммы нужно начинать с тех элементов, для которых известны все входные сигналы, в данном примере - с элемента 1. После определения выхода элемента 1 известными становятся все входы элемента 2 и т. д. Если построение диаграммы с учетом состояния неопределенности вызывает затруднение, можно рекомендовать сначала построить диаграмму с нулевыми задержками, показанной на рис. 3б, затем на том же чертеже наложить на нее диаграмму с максимальными задержками, после чего интервалы состояний неопределенности выделяются намного легче.

В организациях, специализирующихся на разработке логических схем, построение и анализ временных диаграмм выполняются на ЭВМ с помощью специальных моделирующих программ. Для выявления некоторых тонких случаев неопределенности используют не только троичные, но и пятеричные, и более сложные формы представления ситуаций во время переходных процессов. Введение состояния неопределенности позволяет выявить важный, хотя и не очевидный с первого взгляда эффект, который всегда нужно учитывать.

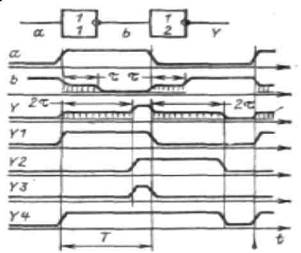

На рис. 4 показана цепочка из двух элементов, на вход которой поступает сигнал в виде единичного импульса длительностью Т. У выходного сигнала в его начале и конце будут зоны неопределенности длительностью по 2Т каждая. Если задержки включения и выключения равны и максимальны, то полученный сигнал Y2, будет сдвинут относительно выходного на 2Т. В результате может оказаться, что один и тот же сигнал, переданный по двум цепочкам на два блока устройства, запустит их не одновременно. Понятие одновременности расплывается и становится относительным.

Если задержки включения существенно отличаются от задержек выключения, получится укороченный на 2Т (Y3) или удлиненный на 2Т (Y4) сигнал. В случае Y4 укороченной окажется пауза между последовательными импульсами. Могут получиться и любые промежуточные формы рассмотренных частных случаев, причем предугадать характер эффекта заранее невозможно. Если цепочка содержит k элементов, то во всех рассмотренных случаях вместо двойки в качестве множителя при Т войдет k. У разработчика нет никаких официальных документов, позволяющих проигнорировать любой из возможных эффектов, и он вынужден проектировать схему так, чтобы ни один из них не привел к сбою в работе. Если на выходе цепочки требуется получить импульс с минимальной длительностью, то длительность импульса на входе цепочки должна быть на k% больше. Аналогично нужно обеспечивать на выходе цепочки и минимальную длительность паузы, и максимальную длительность импульса, если это требуется.

Рисунок 4. – Изменение задержки и длительности импульса при прохождении его по цепочке элементов

2. Гонки

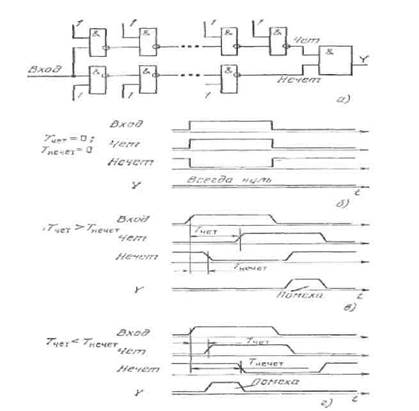

В логических схемах встречаются участки, где сигнал разветвляется, получившиеся два сигнала распространяются по двум независимым цепочкам элементов, а затем оба сигнала снова встречаются на входах одного элемента. Подобная ситуация показана на рис. 5а, где в рассматриваемый момент времени в представленном фрагменте схемы два тракта оказались прозрачными для входного сигнала благодаря тому, что все конъюнкторы фрагмента в этот момент открыты сигналами единичного уровня. Пусть в тракте чет четное число инверторов, а в тракте нечет - нечетное. Анализ подобной схемы методами алгебры Буля без учета задержек даст на ее выходе 0 при любом значении входного сигнала (рис. 5б). Но реальные элементы имеют конечную задержку срабатывания, и если обозначить задержки в трактах чет и нечет через Тчет и Тнечет, то в зависимости от соотношения этих величин получится один из процессов, изображенных на рис. 5 в и г. В обоих случаях в выходном сигнале появится помеха, не предусмотренная булевыми выражениями. Легко проверить, что замена последнего элемента И на элемент ИЛИ не ликвидирует помеху, а лишь проинвертирует ее и изменит момент появления.

Рисунок 5. - Варианты временных диаграмм (б, в, г), иллюстрирующие гонки в логической схеме (а)

Существенно, что полученная помеха - это не пренебрежимо короткий всплеск напряжения малой амплитуды. При достаточно большой разности Тчет и Тнечет помеха будет иметь длительность, во много раз превышающую время переключения элемента, и амплитуду, равную номинальному сигналу. Это уже полноценный логический сигнал, на который могут реагировать последующие элементы. Если выход схемы подключен к запоминающему элементу (триггеру), то помеха может запомниться, и будет влиять на последующие процессы в устройстве. Если выход схемы подан в качестве обратной связи на вход, там появится непредвиденный сигнал, который может вызвать непредвиденное повторное срабатывание этой же схемы.

Описанное явление называют гонками или состязаниями (races). Два сигнала идут разными путями, и схема может реагировать на них по-разному (верно или неверно) в зависимости от того, какой сигнал выиграет гонку.

Основная проблема в том, что разработчик, как правило, не знает, в каком тракте задержка окажется меньше. Изготовитель элементов гарантирует лишь максимальное время задержки элемента данного типа и ничего не говорит ни о конкретной задержке конкретного элемента, ни о минимально возможном времени задержки. Поэтому разработчик логических схем не может воспользоваться тем фактом, что число элементов в цепочке чет, скажем, больше, чем в цепочке нечет. При массовом производстве схем из произвольно взятых элементов найдется достаточно большое число таких узлов, в которых в цепочку чет попадут более быстрые элементы, а в цепочку нечет - более медленные и, вопреки ожидаемому, будет выполняться неравенство Тчет<Тнечет. Даже если в цепочке нечет один элемент, а в цепочке чет - два, то в последнюю вполне могут попасть элементы, имеющие время задержки втрое меньшее, чем элемент цепочки нечет.

Специальный подбор элементов по задержке в условиях современного автоматизированного массового производства недопустим, проверка реально получившегося соотношения задержек обычно неприемлема, так как сильно удорожает наладку аппаратуры. Кроме того, при изменении температуры и старении задержки различных элементов изменяются с разной скоростью, и по этому поводу изготовитель, как правило, никаких гарантий не дает. Единственное, что гарантирует изготовитель элементов и на что может опереться разработчик схем (фактически или хотя бы юридически), это то, что задержка не выйдет за пределы, указанные в ТУ на элемент, и если в борьбе с гонками разработчик хочет одержать победу, то он должен основывать свои расчеты лишь на этих данных.

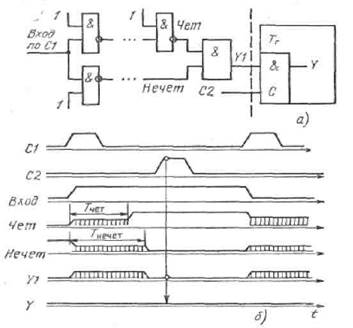

Распространены три метода борьбы с гонками: введение тактирования, построение противогоночных схем и учет минимального времени задержки. Наиболее универсальным, эффективным и поэтому широко используемым методом борьбы с гонками является тактирование. Основная суть его заключается в следующем. По всему цифровому устройству разводится единая система тактирующих (синхронизирующих) сигналов. В широко распространенной двухтактной или двухфазной системе синхронизации используются две периодические последовательности синхросигналов - синхросигнал С1 и синхросигнал С2. Взаимное расположение этих сигналов во времени показано на рис. 6б.

Схема (рис. 6а) разделена штриховой линией на две части. Левая принимает и обрабатывает сигнал ВХОД: ее выходной сигнал Y1 является входным для схемы правой части, которая запоминает результат в триггере Тг.

Рис. 5.6. Исключение помех, порожденных гонками, за счет тактирования

Если сигнал ВХОД каким-либо образом «привязан» к одной из синхросе-рий, например к С1, то этот сигнал будет изменяться только в момент поступления синхроимпульсов С1, а в промежутках между ними будет оставаться постоянным. Схема, показанная в левой части рис. 6а, имеет параллельные пути, в ней существуют гонки и возможно появление на выходе Y1 ложных сигналов. На рис. 6б эту ситуацию в общем виде отражают интервалы неопределенности трактов чет и нечет. На входной конъюнктор С правой части схемы подается сигнал син-хросерий С2. Обязательным условием является такой временной сдвиг С2 по отношению к С1, который превышает самый длинный интервал неопределенности, т. е. самую большую задержку из всех параллельных трактов схемы. Это значит, что сигнал С2 откроет конъюнктор С заведомо после окончания всех переходных процессов в схеме и пропустит логически правильное, не искаженное гонками установившееся значение функции Y1. Как правило, конъюнктор С вводят в состав триггера, что делает триггер синхронным. Такой триггер переключается только по команде синхросигнала и не воспринимает информацию при его отсутствии. Конъюнктор С применяют и без триггера - в тех случаях, когда запоминать выходной сигнал схемы не требуется, а нужно лишь очистить его от помех, порожденных гонками. Тогда сигнал, открывающий конъюнктор С, обычно называют не синхросигналом, а стробом, а сам процесс отсечки помех - стробированием.

Система синхронизации едина для всего цифрового устройства, и интервал между синхросигналами задается в начале разработки. Схемотехник, разрабатывая каждый фрагмент логической схемы, так подбирает число последовательно включаемых в нее элементов и их типы, чтобы все переходные процессы в этом фрагменте с гарантией закончились к моменту поступления очередного синхросигнала. Достоинство синхронизации как средства борьбы с гонками в том, что разработчику не требуется вникать в специфику протекания переходных процессов, в характер возникающих гоночных ситуаций, не нужно знать минимального значения задержки и т. д. Все, что должен знать разработчик - это максимально возможную задержку самого длинного тракта логической схемы, а это легко вычисляется по паспортным данным используемых элементов.

Противогоночные схемы - это схемы, построенные так, что в них если и возникают, то только неопасные гонки, то есть такие, при которых отсутствует риск появления на выходе сигналов, не предусмотренных логическим выражением. Примером неопасной гонки может служить гонка фронта по двум трактам, в каждом из которых содержится четное (или в каждом нечетное) число инверторов и которые объединяются на выходах элементом ИЛИ: кто бы ни выиграл гонку, результат все равно будет верный, изменится лишь задержка его получения. Для исключения опасных гонок можно вводить в схему дополнительные связи и элементы так, чтобы нежелательные параллельные пути запирались самим входным сигналом еще до достижения им опасной развилки тракта. Есть целый ряд других приемов, используемых при построении противогоночных схем.

Полезным свойством противогоночных схем оказывается их способность обрабатывать данные по мере поступления, асинхронно, то есть без привязки к тактирующим сигналам и связанным с этим потерям времени. Однако процедура построения таких схем очень сложна, она требует скрупулезного изучения характера протекания переходных процессов, выявления всех возможных гоночных путей, отделения опасных состязании от неопасных. С ростом числа элементов схемы разработчик очень скоро оказывается в плену невыполнимого по объему перебора вариантов. Специалистами разработан ряд удачных, остроумных асинхронных противогоночных схем, в основном - сложных типов триггеров с числом элементов в пределах десятка. Они широко применяются, в том числе и в тактируемых устройствах, для быстрого выполнения операций внутри самого такта.

Учет минимального времени задержки. Если известно минимально возможное время задержки элемента, то во многих практически важных случаях можно постулировать отсутствие гонок. Пусть в схеме на рис. 5а глубина цепочки Чет настолько больше глубины цепочки Нечет, что задержка в длинной цепочке, даже если последняя состоит только из самых быстрых элементов, будет все равно больше задержки сигнала в короткой цепочке, даже если в нее попадут только самые медленные элементы. Схема со столь большой разницей в длине путей всегда будет вести себя так, как показано на рис. 5в. То есть, пока входной сигнал равен единице, помеха на выходе не появится. Помеху после выключения входного сигнала можно ликвидировать введением дополнительной блокирующей связи. Можно, например, взять в качестве выходного элемента трехвходовой элемент и на его третий вход подать сам входной сигнал. В этом случае выход будет заперт сразу после перехода входного сигнала в нуль. Несложно предложить и другие формы использования для борьбы с гонками сведений о минимально возможной задержке или о наибольшей возможной кратности максимального и минимального значений задержки.

По возможностям применения этого метода борьбы с гонками разработчики, использующие различную элементную базу, находятся в неодинаковых условиях, В лучшем положении обычно находятся разработчики схем, предназначенных для реализации на поверхности кристалла. Результирующая задержка элементов на кристалле определяется длиной и шириной проводников межэлементных связей и временем переключения транзисторов, которое в свою очередь зависит от геометрических размеров элементов его маски. На все эти размеры разработчик схемы кристалла в может влиять, что позволяет ему в случаях, когда это важно, делать задержку одной группы элементов гарантированно больше задержки другой группы. Правда, по мере роста числа элементов, размещаемых на одном кристалле, разработчик логических схем все реже допускается к воздействию на геометрические размеры элементов маски. Технология автоматизированного проектирования схем на перспективных матричных кристаллах разрешает схемотехнику лишь соединять между собой проводниками стандартной ширины уже размещенные на кристалле стандартные транзисторы или логические элементы. Однако и здесь положение разработчика все-таки лучше, чем того, который использует отдельные микросхемы, поскольку задержки однотипных элементов, расположенных на одном кристалле, существенно между собой коррелируют, чего нельзя сказать о микросхемах даже одной закупочной партии, одного изготовителя. Эта корреляция позволяет изготовителю кристаллов после проведения соответствующих исследований постулировать для схемотехника максимально возможную кратность задержек элементов, расположенных на одном кристалле данного типа. С точки зрения борьбы с гонками это во многих случаях не хуже, чем знание минимально возможной задержки. Поэтому внутри интегральных схем метод борьбы с гонками за счет назначения параллельными путями таких соотношений задержек, при которых опасные гонки невозможны, используется, особенно при построении небольших узлов - типа триггеров, счетчиков и т. п.

В худшем положении находится разработчик, использующий готовые микросхемы, поскольку юридического документа о минимальном значении задержки он чаще всего не имеет. Правда, и тут опытный инженер может утверждать, что при использовании любой современной серии элементов и при любом их сочетании пробег сигнала по цепочке из, скажем, 64 элементов длится «наверняка» дольше, чем пробег сигнала по параллельной ветви из одного элемента. На сегодня нет серий, задержка элементов внутри которых отличалась бы в 64 раза. И в 32 раза тоже нет. И в 16, пожалуй, не найдется. Относительно восьми можно задуматься, в защиту четырех большинство специалистов серьезно спорить уже не станут, а отклонение времени задержки вдвое встретится в большинстве серий. Таким образом, если отсутствие гонок обосновывается большой кратностью числа элементов параллельных путей, то нужно отдавать себе отчет в том, что есть зоны явно допустимых решений (например, кратность 64) и зоны явно недопустимых (кратность 2), а граница между ними не определена. Каждый разработчик определяет ее для себя индивидуально в зависимости от опыта, соотношения поощрения за экономичную схему и наказания за сбои в ней из-за гонок. Проблема из технической становится психологической, организационной. В инженерной практике пользуются этим приемом и строят схемы, в которых в принципе, юридически, гонки возможны, но по утверждению разработчика их «наверняка» не будет.

В последние годы растет интерес к еще одному методу борьбы с гонками -построению самосинхронизирующихся схем. Рабочие узлы в этом случае строятся непротивогоночными, но они дополняются специальными схемами, которые обнаруживают факт окончания переходных процессов и вырабатывают разрешающий сигнал для следующих схем, играющий в каком-то смысле роль «асинхронного синхросигнала». Это направление рассматривается как весьма перспективное для построения БИС и особенно сверхБИС, где применение обычной синхронизации встречает ряд трудностей. Однако в схемах и микросхемах обычного размера и технологии это направление пока не находит применения ввиду как сложности построения такого рода схем, так и, приблизительно, удвоения их аппаратурных затрат

Проблема гонок в цифровой схемотехнике является очень серьезной. Большинство трудно обнаруживаемых и удивительно разнообразно проявляющихся ошибок в функциональных схемах связано с гонками, возможности появления которых разработчик не заметил. Основная причина - ограниченность поля внимания человека. При разработке сложной схемы все внимание поглощается конструированию главного пути распространения сигнала, непосредственно решающего поставленную задачу. При этом побочные, не нужные для дела пути выпадают из поля зрения, а в них и «таится погибель».

Гонки во вновь разработанной схеме нужно искать специально. Если есть такая возможность, то наиболее надежным и простым методом является моделирование работы схемы с помощью специальных программ. При поиске гонок «вручную» сначала нужно выявить все подозрительные места и затем методически их исследовать. Обнаружению таких мест способствуют специально предпринимаемые просмотры схемы, нацеленные на выявление всех возможных параллельных путей распространения сигнала. Полезен анализ временных диаграмм, в которых зоны неопределенности указывают на возможность появления ложных сигналов.

В борьбе с гонками наряду с излагаемым подходом, ориентированным на гарантированную работу даже при наиболее неблагоприятном сочетании задержек, существуют менее строгие походы, в основе которых лежит утверждение, что худший случай встречается редко, поэтому для оценки задержки схемы можно брать некоторое вероятностное значение, меньшее, чем максимально возможное время задержки. Подобные подходы, против которых в принципе возражать нельзя, для цифровой техники оказываются плодотворными, только если есть возможность провести абсолютно полное тестирование готового устройства во всех возможных режимах и условиях окружающей среды.

Если же надежность работы устройства основывается лишь на статистической правильности работы отдельных его цепей, то, когда цепей много, что типично для цифровой техники, даже небольшое уменьшение надежности срабатывания элементов приводит к резкому снижению надежности всего устройства. Можно подсчитать, что если в каждой цепочке допустить вероятность помехи из-за гонок всего в I %, то вероятность работоспособности устройства, содержащего 100 таких цепочек, будет около 37 %. В среднем из каждых трех устройств, два будут неработоспособны. Поэтому приемами, приносящими в жертву надежность срабатывания отдельных цепочек, в цифровой технике пользоваться не следует.

3. Гонки по входу Гонки по входу возникают, когда ветвящийся сигнал поступает на элементы, имеющие разброс по уровню срабатывания (рис. 7а), а фронт этого сигнала излишне пологий (рис. 7б). Если длительность фронта входного сигнала заметно больше времени срабатывания элементов, то где-то в середине фронта будет существовать отрезок времени, когда с точки зрения одного элемента входной сигнал уже равен 1, а с точки зрения другого - еще равен 0. Элементы будут реагировать на один и тот же сигнал как на два различных, а такая ситуация при проектировании схемы ее алгоритмом не предусматривается. В результате схема в течение этого времени может выработать ложные сигналы. Это явление и называют «гонки по входу». Гонки по входу не наблюдаются, если логическая схема собрана на элементах одной серии микросхем. Потенциально опасны схемы, собранные из элементов различных серий, имеющих одинаковый уровень сигналов, но существенно различные времена задержек и фронтов. Гонки по входу возникают в схемах некоторых БИС, если их межэлементные связи сильно заваливают фронты. Опасностью возникновения гонок по входу объясняются ограничения на максимальную длительность фронтов входных сигналов, приводимые в паспортах многих микросхем.

Рисунок 7. - Гонки по входу: иллюстрация условий их возникновения

Если нет возможности увеличить крутизну фронта, то единственным средством борьбы с гонками по входу остается тактирование, поскольку в тактированном устройстве выходной сигнал схемы не используется до тех пор, пока в этой схеме не окончатся абсолютно все переходные процессы независимо от их физической природы. Однако тактирование не спасает от гонок по самому тактирующему входу. Поэтому, если крутизна фронтов синхросигналов мала, то нужно применять такие синхронные триггеры, в которых гонки по входу не возникают.

Контрольные вопросы: 1.

41. Дайте характеристику статическому и динамическому перемещению при выделении ресурсов.

42. Какие способы структуризации виртуального адресного пространства Вы знаете?

43. Какие подходы используются при преобразовании виртуальных адресов в физические.

44. Сравните методы управления, используемые в СРВ и многопользовательских системах с разделением времени.

45. Из чего слагается задержка логической схемы?

46. В чем сложность учета задержек?

47. От чего зависит задержка каждого конкретного элемента?

48. Какие средства анализа переходных процессов в логических схемах Вы знаете?

49. Дайте характеристику гонкам. В чем суть гонок?

50. Какие методы борьбы с гонками Вы знаете?

51. Дайте характеристику методу тактирования.

52. Какие схемы называются противогоночными? Дайте их характеристику.

53. Дайте характеристику самосинхронизирующимся схемам.

54. Когда возникают гонки по входу?

Тема 3. Операционные системы реального времени

Лекция 3.1. Архитектура систем реального времени

1. Основные параметры и механизмы операционных систем реального времени.

2. Базовые концепции построения операционных систем реального времени.

3. Монолитная архитектура.

4. Модульная архитектура на основе микроядра.

5. Объектная архитектура на основе объектов – микроядер.

1. Основные параметры и механизмы операционных систем реального времени

Одно из коренных внешних отличий систем реального времени от систем общего назначения - четкое разграничение систем разработки и систем исполнения. Система исполнения операционных системах реального времени - набор инструментов (ядро, драйверы, исполняемые модули), обеспечивающих функционирование приложения реального времени.

Большинство современных ведущих операционных систем реального времени поддерживают целый спектр аппаратных архитектур, на которых работают системы исполнения (Intel, Motorola, RISC,MIPS, PowerPC, и другие). Это объясняется тем, что набор аппаратных средств является частью комплекса реального времени и аппаратура должна быть также адекватна решаемой задаче. Поэтому ведущие операционные системы реального времени перекрывают целый ряд наиболее популярных архитектур, чтобы удовлетворить самым разным требованиям по части аппаратуры. Систему исполнения операционных системах реального времени и компьютер, на котором она исполняется называют "целевой" (target) системой. Система разработки – это набор средств, обеспечивающих создание и отладку приложения реального времени.

Системы разработки работают, как правило, в популярных и распространенных ОС, таких, как UNIX. Кроме того, многие операционные системы реального времени имеют и так называемые резидентные средства разработки, исполняющиеся в среде самой операционной системы реального времени - особенно это относится к операционным системам реального времени класса "ядра".

Функционально средства разработки операционных систем реального времени отличаются от привычных систем разработки, таких, например, как Developers Studio, TaskBuilder, так как часто они содержат средства удаленной отладки, средства профилирования (измерение времен выполнения отдельных участков кода), средства эмуляции целевого процессора, специальные средства отладки взаимодействующих задач, а иногда и средства моделирования. Рассмотрим основные параметры операционных системах реального времени.

Время реакции системы.Практически все производители систем реального времени приводят такой параметр, как время реакции системы на прерывание (interrupt latency). Если главным для системы реального времени является ее способность вовремя отреагировать на внешние события, то такой параметр, как время реакции системы является ключевым.