Обобщенная архитектура параллельных систем

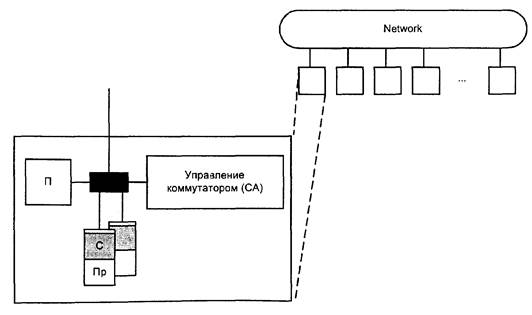

Рассматривая эволюцию ОСНОВНЫХ ПОДХОДОВ К параллельным архитектурам, можно заметить взаимопроникновение архитектур рассмотренных вычислительных систем и наличие общей типовой параллельной машинной организации, показанной на рис. 9.15. Типовая параллельная вычислительная система включает в себя множество законченных компьютеров, содержащих один или несколько процессоров (Пр) с кэш-буферами (С) и память (П), соединенных между собой через масштабируемую коммуникационную сеть. Управлять генерацией выходных сообщений или приемом входных сообщений помогает вспомогательный процессорный блок (СА) — контроллер.

С одной стороны, объединение всех подходов к построению параллельных систем в рамках одной общей структуры может показаться существенным ограничением в области дизайна. С другой стороны, все многообразие описанных выше подходов реализуется в (СА) — контроллере. Все дело в функциональности, которая должна быть им обеспечена, т. е. каков должен быть интерфейс между процессором, системой памяти и сетью.

Не удивительно, что различные программные модели определяют собственные, отличные от других требования к дизайну СА и определяют, какие системные операции являются общими и должны быть оптимизированы. В случае разделяемой памяти СА крепко интегрируется с системой памяти (П), для того чтобы управлять событиями в памяти, которые могут потребовать взаимодействия с другими узлами системы. СА должен также управлять приемом сообщений, доступом к памяти и устанавливать транзит по направлению к другому узлу системы. В случае МРА, коммуникация инициализируется четкой акцией системного или пользовательского уровня, т. е. не требуется "наблюдаемости" системных событий в памяти. Вместо этого необходимо наличие возможности быстрой посылки сообщения и формирования ответа на входящее сообщение. Можно потребовать, чтобы под ответом подразумевалось выполнение операции сравнения тэгов на совпадение, чтобы буфера были локализованы, чтобы передача данных комментировалась. Параллельные данные и систолические подходы делают акцент на

Рис. 9.15. Обобщенная масштабируемая структура параллельных систем

быстрой глобальной синхронизации, которая может быть прямо поддержана сетевыми механизмами или СА.Dataflow-архитектура делает акцент на быстром, динамическом распределении вычислений, основанном на входных сообщениях. Систолические алгоритмы предоставляют возможность использовать общие алгоритмические модели в специальных задачах синхронизации параллельного взаимодействия. Даже при этих различиях важно заметить, что все из рассмотренных подходов имеют много общего, т. е. они требуют инициировать сетевую транзакцию как результат специфичных процессорных событий, и они требуют реализации прямых операций на удаленном узле системы для выполнения необходимых программных действий.

Мы также видим, что произошло разделение между программной моделью и машинной организацией, как только среда параллельного программирования достигла своей зрелости.