Организация прямого доступа к памяти

Рис. 1. Принципиальная схема центрального процессорного устройства

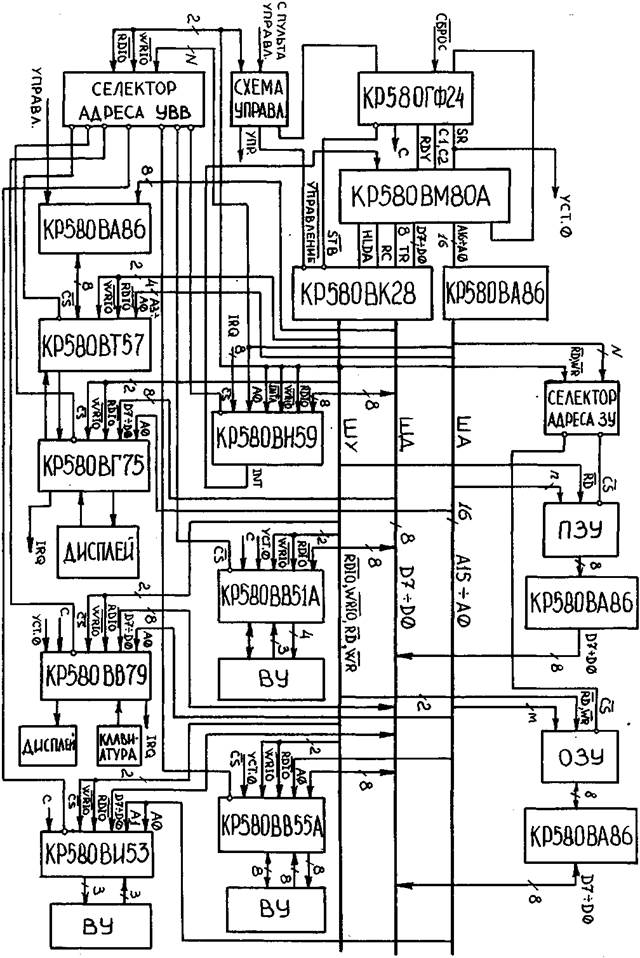

Рис. 2. Типовая схема МП системы на базе МПК серии КР580.

Состав и функциональное назначение серии К580 представлено в таблице.

| ИМС | Функциональное назначение | Заруб. аналог | Тип корпуса |

| ВГ18 ГФ24 ВК28 ВК38 ВТ42 BВ51А ВИ53 ВВ55А ВТ57 ВН59 ВГ75 ВВ79 ВМ80А ИР82 ИР83 ВА86 ВА87 ВК91А ВГ92 ВГ93 ВГ72 ВР43 ВТ42 | Контроллер шины И41 Генератор тактовых сигналов Системный контроллер и шинный формирователь. -//- Адресный мультиплексор и счетчик для динамического ОЗУ с объемом 16К Синхронно-асинхронный приемопередатчик Программируемый таймер интервалов Программируемый интерфейс параллельной связи Программируемый контроллер ПДП Программируемый контролер прерываний Программ. контроллер видеотерминала Программ. контроллер клавиатуры и индикации Центральный процессорный элемент Адресный буферный регистр Инвертированный ----//------- Шинные 8-разрядные формирователи -//- --//-- (инвер.) МП канал общего пользования (приемопередатчик на общую шину) Контроллер интерфейса МП - канал общего пользования Приемопередатчик МП - канала общего пользования Контроллер НГМД одинарный и двойной плотности записи Схема расширения ввода-вывода Адресный мультиплексор и счетчик для динамического ОЗУ с объемом 16К | 8251А 8255А 8080А 8291А 8272А | 2123.40-2 238.16-2 2121.28-4 -//- 2121.28-5 2120.24-3 2123.40-2 2123.40-2 2121.28-5 2123.40-2 2123.40-2 2123.40-2 2140.20-1 2140.20-1 2140.20-1 2123.40-2 2121.28-10 |

Фирма Intel выпускает для МП 8080/8085 множество микросхем.

Например, выпускается 4 микросхемы PIO:

а) i8155 - имеет 3 порта, ЗУПВ 256 байт, 14-битный счетчик;

б) i8255 - имеет 3 порта;

в) i8355 - имеет 2 порта, ПЗУ 2 Кбайта;

г) i8755 - имеет 2 порта, СППЗУ 2 Кбайта.

i8231 - арифметический процессор (+,-,*,/, тригонометрич. и log функции);

i8232 - МП чисел с плавающей запятой (32 и 64 битные);

i8202 - контроллер динамических ЗУПВ;

i8253 - счетчик-таймер;

i8048 - три порта, один счетчик, ЗУПВ 64 байта, ПЗУ 1 Кбайт;

i8035 - три порта, один счетчик, ЗУПВ 64 байта, ПЗУ нет;

i8748 - три порта, один счетчик, ЗУПВ 64 байта, СПП3У 1 Кбайт;

i8049 - три порта, один счетчик, ЗУПВ 128 байт, ПЗУ 2 Кбайт;

i8022 - три порта, один счетчик, ЗУПВ 64байта, ПЗУ 1Кбайт, один АЦПУ;

i8051 - три порта, один счетчик, ЗУПВ 64 байта, ПЗУ 4 Кбайт.

Основные МП периферийные устройства, выпускаемые фирмой Intel

Microprocessor peripherals

8202A - Dynamic RAM Controller

8203 - 64Ê Dynamic RAM Controller

8206 - Error Detection and Correction Unit

8207 - Advanced Dynamic RAM Controller

8231 - Arithmetic Processing Unit

8232 - Floating Point Processing Unit

8251A - Programmable interval Timer

8254 - Programmable interval Timer (8253/8253-5)

8255A/8255-5 - Programmable Peripheral interface

8256 - Multifunction Universal Asynchronous Receiver-Transmitter

8271/8271-6 - Programmable Floppy Disk Controller

8272A - Single/Double Density Floppy Disk Controller

8273, 8273-4, 8273-8 - Programmable HDLC/SDLC Protocol Controller

8274 - Multi-Protocol Serial Controller (MPSC)

8275H - Programmable CRT Controller

8276H - Smalle System CRT Controller

8279/8279-5 - Programmable Keyboard/Display interface

8291A - GPIB Talker/Listener

8292 - GIPB Controller

8293 - GIPB Transceiver

8294A - Data Encryption Unit

8295 - Dot Matrix Printer Controller

82062 - Winchester Disk Controller

82051 - Ethernet Serial interface

82586 - Local Communications Controller

82720 - Graphics Display Controller

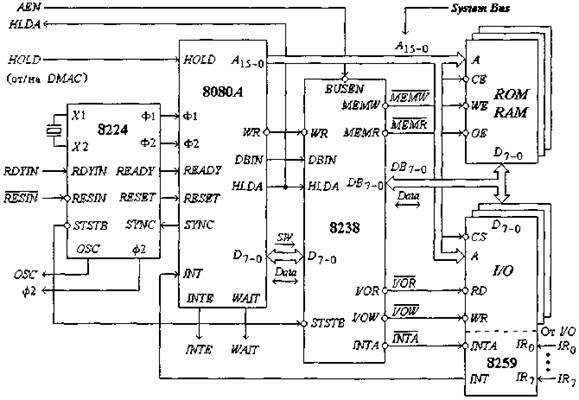

Рис. 3. Структурная схема МП системы на основе МП 8080А

БИС общего назначения

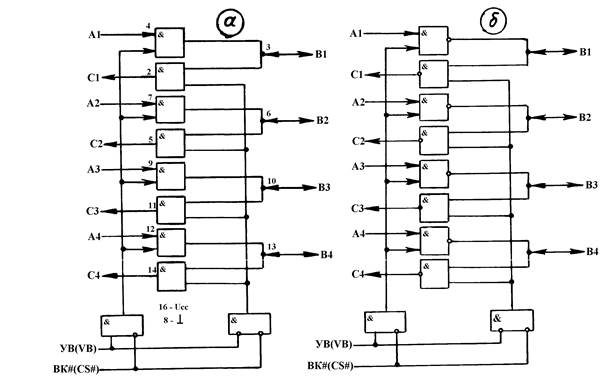

Шинный формирователь К589АП16(26)

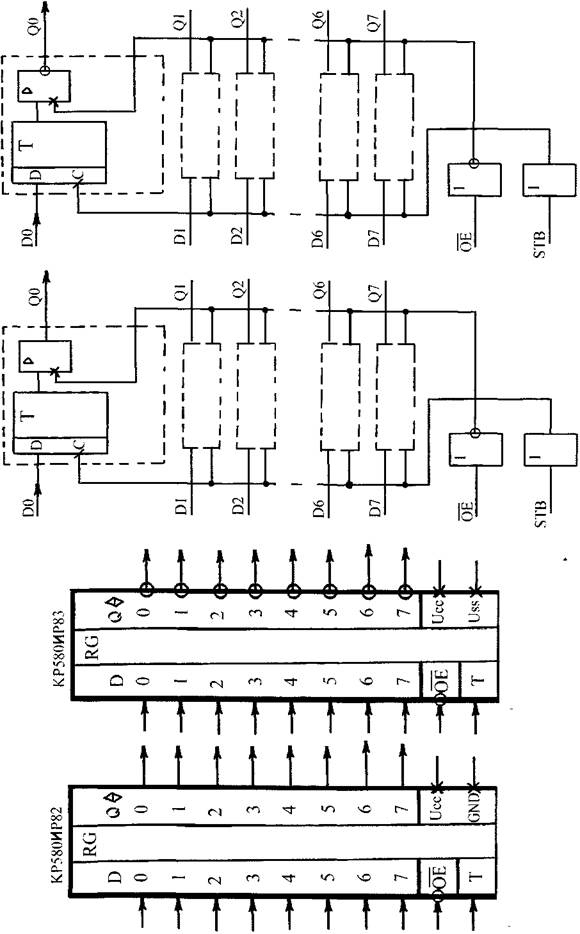

Рис. 4. Шинные формирователи К589АП16, К589АП26.

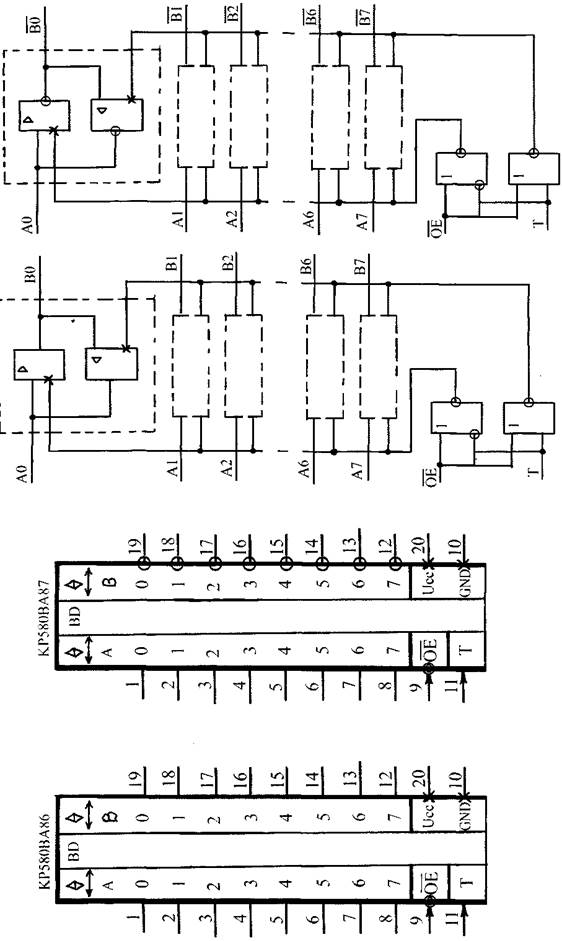

Буферный усилитель данных

i8286(87) - КР580ВА86(87)

Адресный буферный регистр

i8282(83) - КР580ИР82(83)

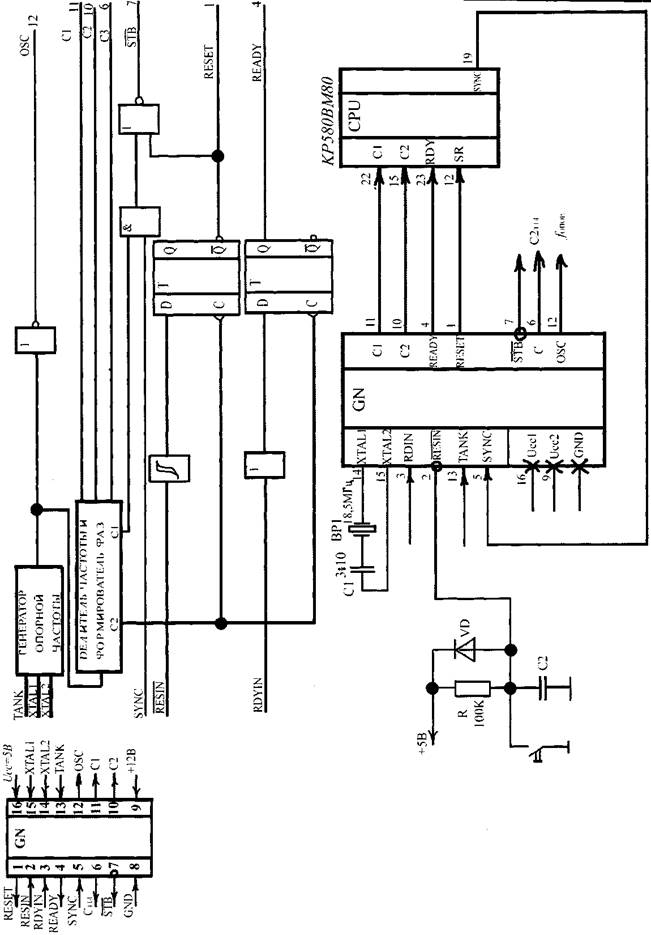

Генератор тактовых импульсов С1,С2

i8224 (КР580ГФ24)

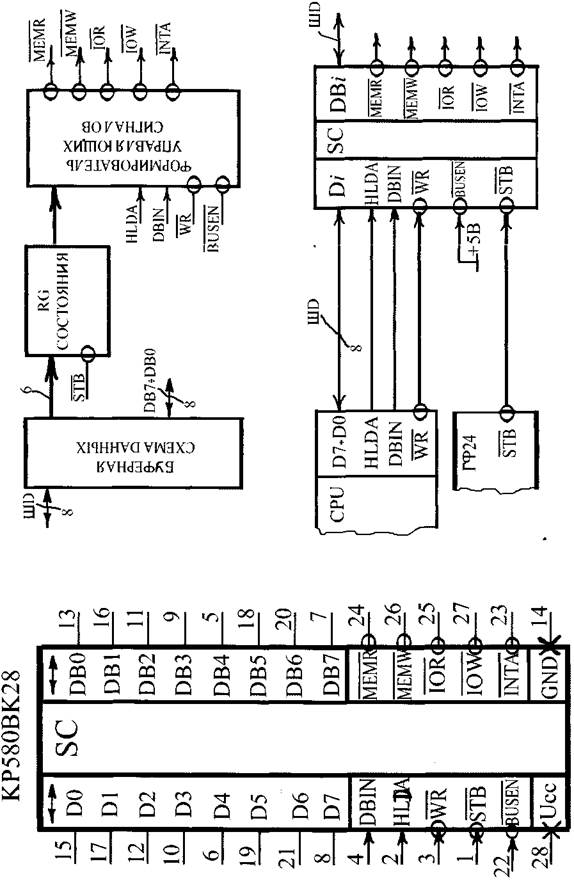

СИСТЕМНЫЙ КОНТРОЛЛЕР КР580ВК28(38)

(аналог i8228/38)

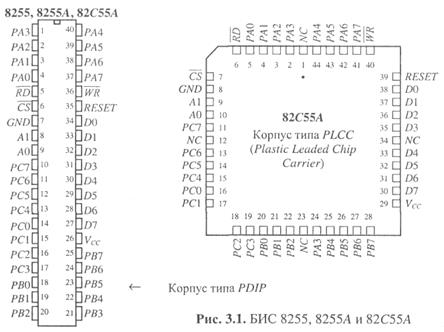

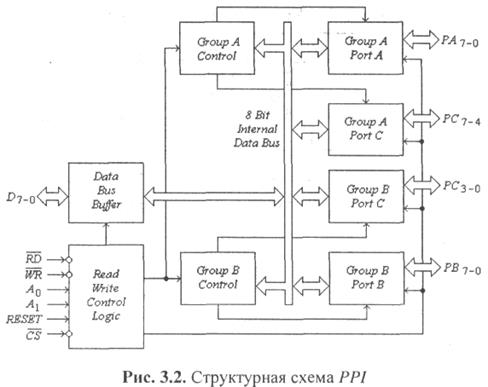

Программируемый параллельный интерфейс (ППИ)

i8255А (КР580ВВ55А)

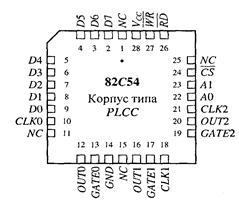

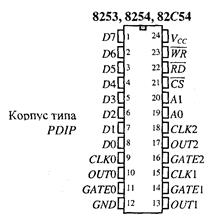

Программируемый интервальный таймер (ПИТ)

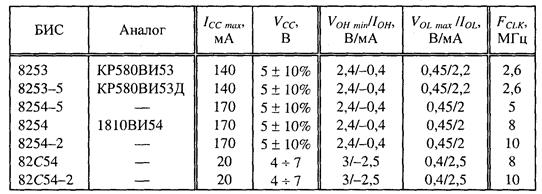

i8253 (КР580ВИ53)

Таблица. Основные параметры БИС таймеров

|

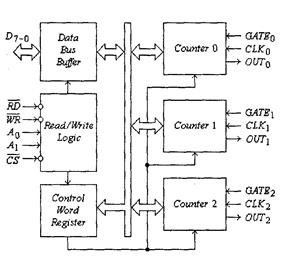

рис. 10. Структурная схема рис. 11. Структурная схема

одного таймера канала таймера

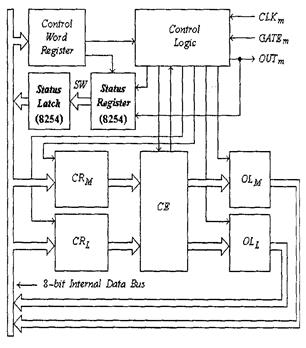

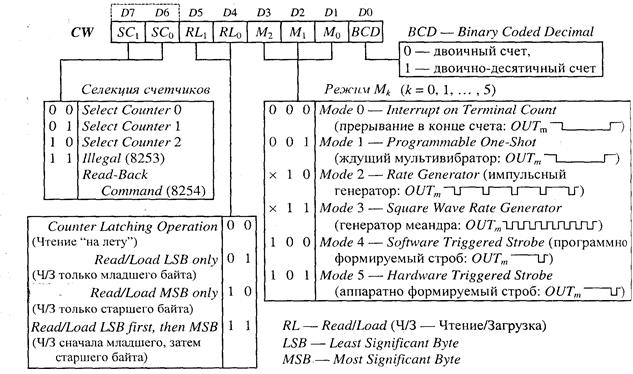

Рис. 12. Слово управления (CW – Сommand Word) таймера

SC (Select Counter) - выбор счетчика

RL (Read/Load) - чтение/загрузка

M (Mode) - режим

BCD (Binary Coded Decimal) - двоично-десятичный код

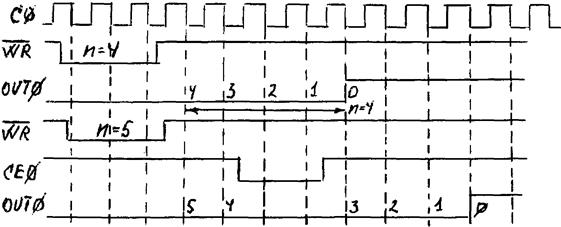

Рис. 13. Временная диаграмма работы таймера в 0 режиме

Рис. 14. Временная диаграмма работы таймера в 1 режиме

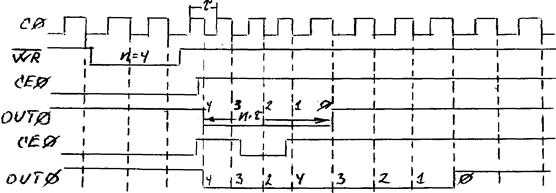

Рис. 15. Временная диаграмма работы таймера во 2 режиме

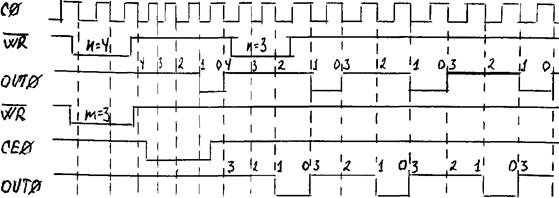

Рис. 16. Временная диаграмма работы таймера в 4 режиме

Рис. 17. Временная диаграмма работы таймера в 5 режиме

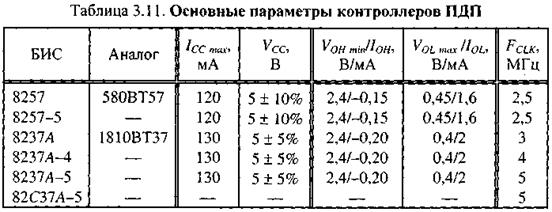

Организация прямого доступа к памяти

|

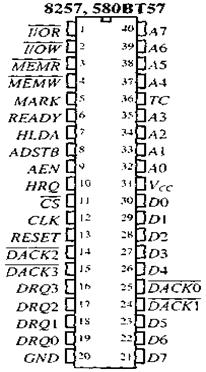

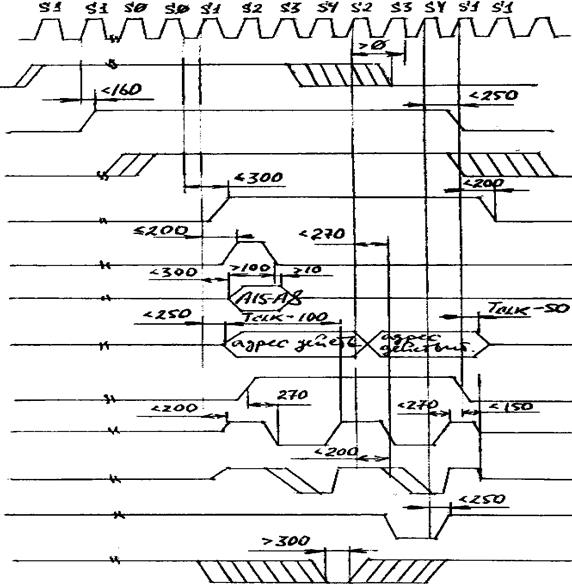

Рис. 18. Выводы БИС контроллера i8257

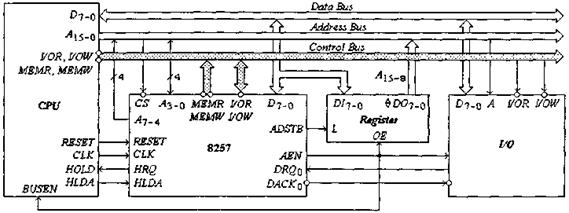

Рис. 19. Схема подключения DMAC к системной шине.

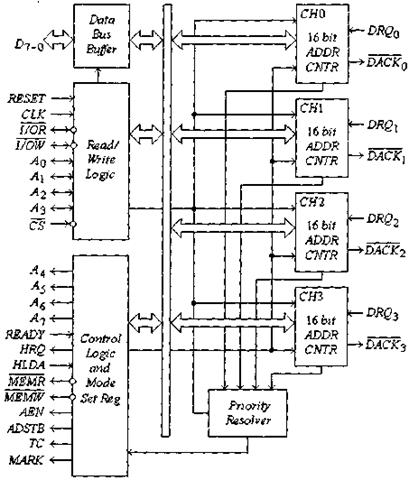

Рис. 20. Структурная схема БИС К580ВТ57

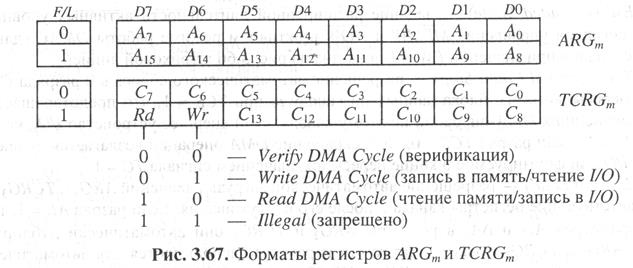

| Регистр | Байт | Адрес. входы А3 А2 А1 А0 | Двунаправленная ШД D7 D6 D5 D4 D3 D2 D1 D0 |

| Адрес ПД в канале 0 | Младший Старший | 0 0 0 0 0 0 0 0 | А7 А6 А5 А4 А3 А2 А1 А0 А15 А14 А13 А12 А11 А10 А9 А8 |

| N-1 циклов в канале 0 | Младший Старший | 0 0 0 1 0 0 0 1 | С7 С6 С5 С4 С3 С2 С1 С0 ЧтП ЗпП С13 С12 С11 С10 С9 С8 |

| Адрес ПД в канале 1 | Младший Старший | 0 0 1 0 0 0 1 0 | То же, что и для канала 0 |

| N-1 циклов в канале 1 | Младший Старший | 0 0 1 1 0 0 1 1 | |

| Адрес ПД в канале 2 | Младший Старший | 0 1 0 0 0 1 0 0 | То же, что и для канала 0 |

| N-1 циклов в канале 2 | Младший Старший | 0 1 0 1 0 1 0 1 | |

| Адрес ПД в канале 3 | Младший Старший | 0 1 1 0 0 1 1 0 | То же, что и для канала 0 |

| N-1 циклов в канале 3 | Младший Старший | 0 1 1 1 0 1 1 1 |

Установка режима 1 0 0 0 А3 КС- УЗ ЦСП РКЗ РК2 РК1 РК0

(только записыв.) стоп

(только записыв.) стоп

Регистр состояния 1 0 0 0 0 0 0 ФОД ТС3 ТС2 ТС1 ТС0

(только читается)

АЗ - Автозагрузка

АЗ - Автозагрузка

УЗ - Удлиненная запись

ЦСП - Циклический сдвиг приоритета

РКi - Разрешение i-го канала

ФОД - Флаг обновления данных

|

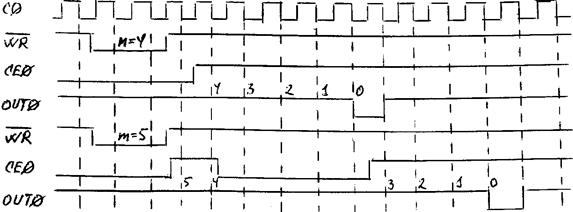

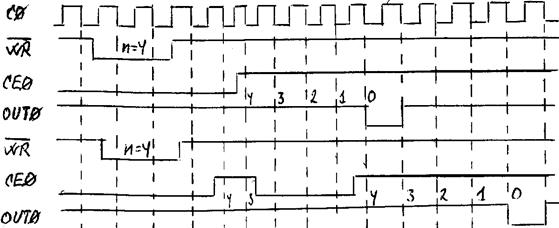

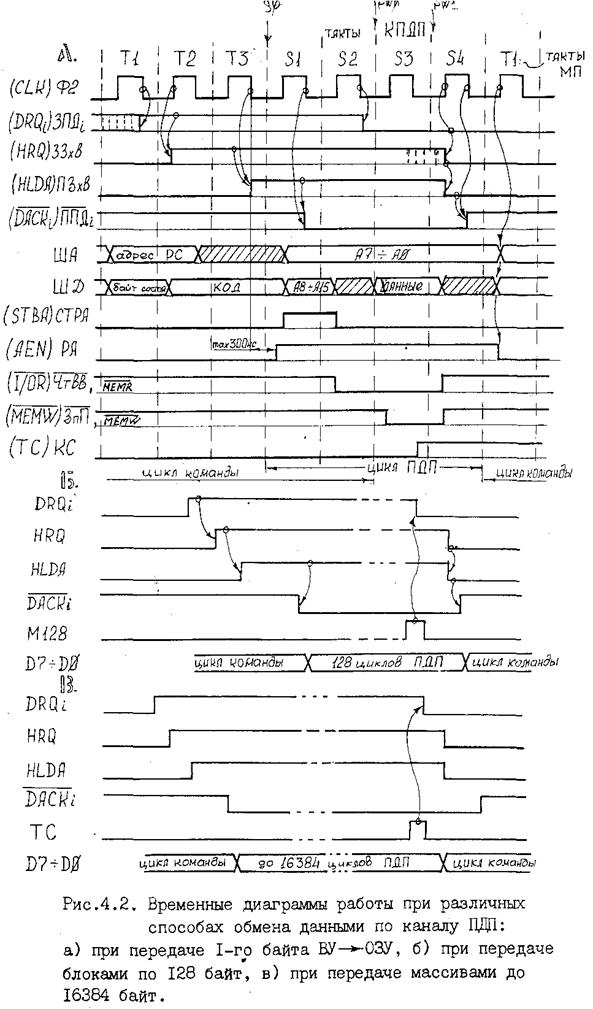

Нарисуем временную диаграмму работы КПДП i8237 (см. рис. ).

CLK

DREQ

HRQ

HLDA

AEN

ADSTB

DB7-DB0

A7-A0

DACK

IOR#,MEMR#

IOW#,MEMW#

INT,EOP#

EXT,EOP#

Рис. 21. Временная диаграмма работы DMAC i8237

Последовательный интерфейс

Рис. 23. Синхронный обмен информацией.

Рис. 24. Асинхронный режим обмена информацией.

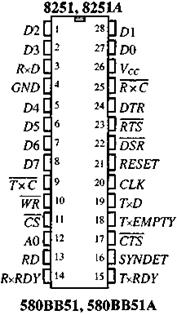

Рис. 25. Выводы БИС USART 8251/8251А

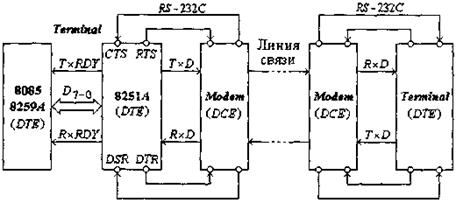

Рис. 26. Структурная схема дуплексного канала связи.

ШД ВыхПд СПд# ГПрТ# ГПд# СПр# ГПр ВхПр

TxD TxC# CTS# TxRDY RxC# RxRDY RxD

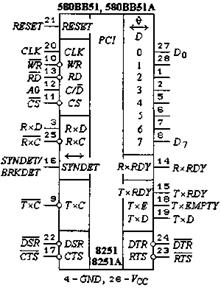

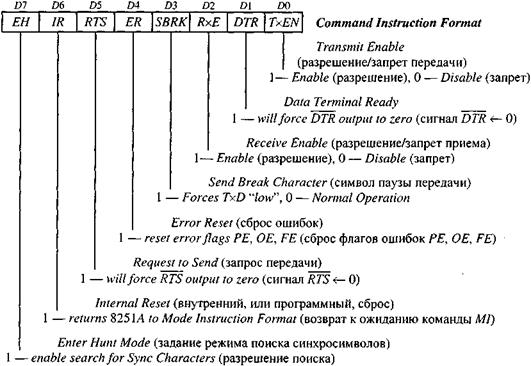

Рис 27. Структурная схема PCI 8251А

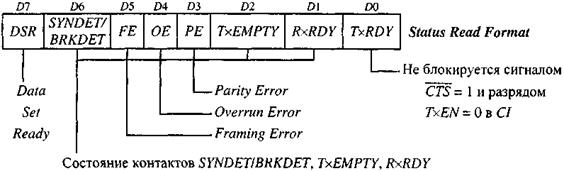

Рис. 28. Формат инструкции команд CI.

Рис. 29. Формат слова состояния SW.

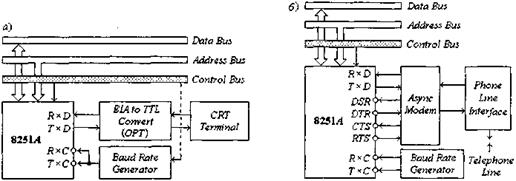

Рис. 30. Сигналы ВВ51 при передаче и приёме информации.

Рис. 31. Асинхронные интерфейсы.

Рис. 32. Синхронные интерфейсы.

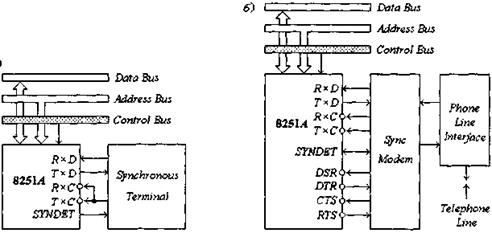

Рис. 33. Типичная последовательная линия связи между компьютерами

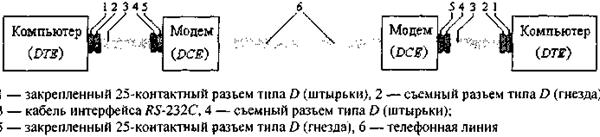

Рис. 34. Кабель нуль-модема.

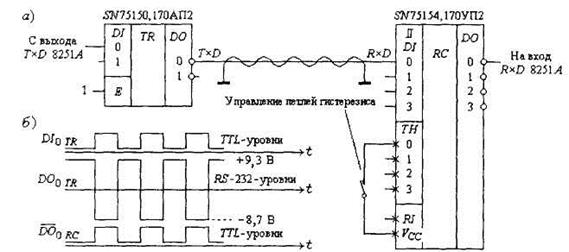

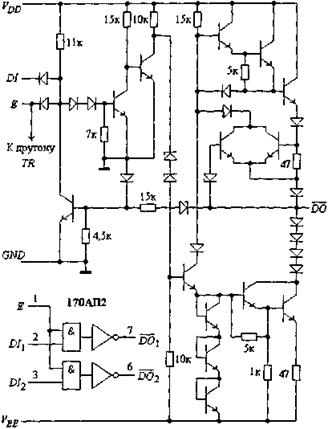

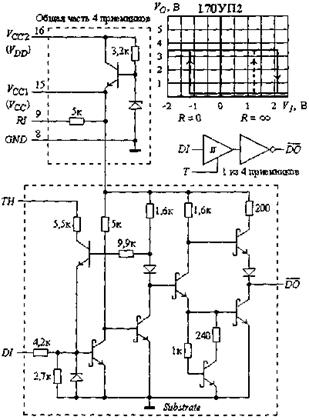

Рис. 35. Линия связи на основе интерфейса RS-232

Рис. 36. Принципиальная схема одного Рис. 37. Принципиальная схема одного

передатчика типа SN75150 приемника типа SN75154

Рис. 38. Использование ВВ51 в интерфейсе RS-232C с символьными обозначениями

линий управления.

Таблица № 2

| Обозначение EIA(CCITT) | Кон такт | Название | Описание |

| АА (101) АВ (102) ВА (103) ВВ (104) СА (105) СВ (106) СС (107) CF (109) CD (108/2) СЕ (125) СQ (110) СН (111) CI (112) DA (113) DB (114) DD (115) SBB (119) SBA (118) SCA (120) SСВ (121) SCF (122) | Защитная земля Сигнальная земля Передаваемые данные Принимаемые данные Запрос передачи Сброс передачи Готовность модема Детектор сигнала приемной Готовность терминала Индикатор звонка Детектор качества сигнала Селектор скорости сигналов данных (источник DTE) Селектор скорости сигналов данных (источник DСE) Синхронизация передатчика (источник DTE) Синхронизация приемника (источник DCE) Синхронизация приемника Вторичные принимаемые данные Вторичные передаваемые данные Вторичный запрос передачи Вторичный сброс передачи Детектор принятого сигнала на вторичной линии | Используется как проводник заземления оборудования Используется как общая земля для всех сигналов Для вывода данных в модем Для вывода данных из модема В модем для включения и выключения передатчика модема при работе в полудуплексном режиме Из модема, указывает что модем готов передавать Из модема, указывает, что модем включен и не находится в автономном режиме Из модема, указывает, что модем принимает сигнал от линии модема на другом конце линии связи В модем, готовит его к подключению к линии связи и началу передачи Из модема, указывает, что в линии обнаружен сигнал звонка Из модема активен при малой вероятности ошибки в принятых данных В модем, указывает модему одну из двух синхронных скоростей данных или один из диапазонов скоростей Из модема, указывает интерфейсу или терминалу одну из двух синхронных скоростей данных или один из диапазонов скоростей В модем, сигнал синхронизации передатчика модема Из модема, обеспечивает интерфейс или терминал сигналом синхронизации передатчика Из модема, обеспечивает интерфейс или терминал сигналом синхронизации приемника В модем, для ввода данных с низкой скоростью В модем, для ввода данных с низкой скоростью В модем, для включения вторичного передатчика модема Из модема, показывает готовность вторичного передатчика Из модема, показывает, что на вторичной линии обнаружен сигнал |

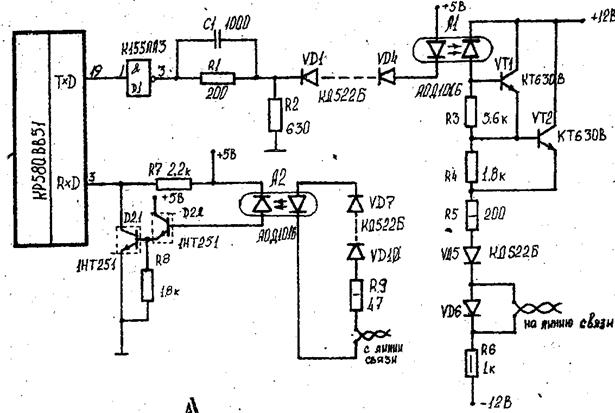

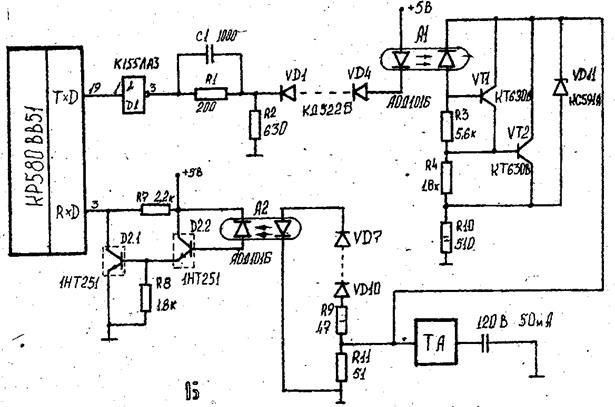

Рис. 39. Принципиальная схема сопряжения КР580ВВ51 с каналом связи ИРПС:

А – по связи “токовая петля 20 mA”; Б – по связи “токовая петля 40 mA”.

Таблица № 3 Разводка разъема DB9

| Номер контакта | Назначение контакта (со стороны компьютера) | Вход или выход |

| Детектор принимаемого с линии сигнала (Data Carrier Detect, DCD) Принимаемые данные (Received Data, RD) Передаваемые данные (Transmitted Data, TD) Готовность выходных данных (Data Terminal Ready, DTR) Сигнальное заземление (Signal Ground, SG) Готовность данных (Data Set Ready, DSR) Запрос для передачи (Request to Send, RTS) Сброс для передачи (Clear to Send, CTS) Индикатор вызова (Ring Indicator, RI) | Вход Вход Выход Выход - Вход Выход Вход Вход |

Таблица № 4 Разводка разъема DB25

| Номер контакта | Направление передачи сигнала | Сигнал | Назначение контакта (со стороны компьютера) |

| — k DCE к DTE k DCE к DTE к DTE — к DTE к DTE к DTE kDCE к DTE к DTE k DCE к DTE к DTE к DTE k DCE k DCE k DCE к DTE к DTE к DTE k DCE к DTE | FG TxD RxD RTS CTS DSR SG DCD — — QM SDCD SCTS STxD TxC SRxD RxC DCR SRTS DTR SQ RI DRS TC — | Защитное заземление (Frame Ground, FG) Передаваемые данные (Transmitted Data, TD) Принимаемые данные (Received Data, RD) Запрос передачи данных (Request to Send, RTS) Сброс передачи (Clear to Send, CTS) Готовность данных (Data Set Ready, DSR) Сигнальное заземление (Signal Ground, SG) Обнаружение несущей данных (Детектор принимаемого с линии сигнала)(Data Carrier Detect, DCD) Полож. контрольное напряжение (+12 В, 20 мА) Отриц. контрольное напряжение (-12 В, 20 мА) Выбор частоты передачи Обнаружение несущей дополнительного канала Сброс передачи дополнительного канала Передаваемые данные дополнительного канала Синхронизация передачи Принимаемые данные дополнительного канала Синхронизация приема Свободный (местный шлейф) Запрос передачи дополнительного канала Готовность терминала принимать данные (Data Terminal Ready, DTR) Детектор качества сигнала (Не используется) Индикатор вызова (звонка) (Ring Indicator, RI) Переключатель скорости передачи данных (не используется) Внешняя синхронизация передачи Свободный (индикатор тестирования) |

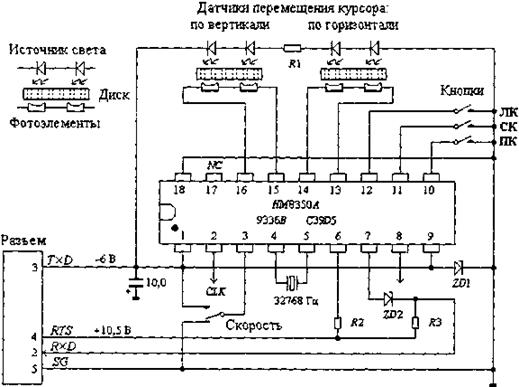

Рис. 40. Контроллер последовательной мыши.

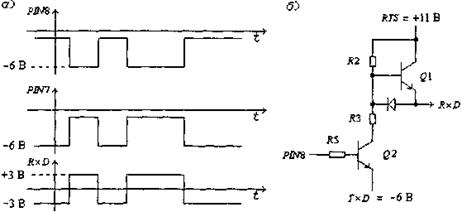

Рис. 41. Временные диаграммы мыши (а);

выходной каскад мыши для интерфейса RS-232 (б).

Таблица 5. Сравнительные параметры интерфейсов RS-232С, RS-422A, RS-423A и RS-485

| Параметр | RS-232С | RS-422A | RS-423A | RS-485 |

| Тип линии связи | Несиммет ричная | Симмет ричная | Несиммет ричная | Симмет ричная |

| Максим, длина линии связи, м | ||||

| Максим, скорость передачи данных, Мбод | 0,02 | 0,10 | ||

| Маркер (данные 1) | -3В | А<В | А отрицат. | А<В |

| Пробел (данные 0) | +3В | А>В | А положит. | А>В |

| Максим, входн. напряжение приемника, В | ±25 | ±1 | ±12 | -7-+12 |

| Выходное напряжение передатчика: | ||||

| минимальное, В | ±5 | ±2 | ±3,6 | ±1,5 |

| максимальное, В | ±15 | ±5 | ±5,4 | ±5 |

| Чувствительность приемника, В | ±3 | ±0,2 | ±0,2 | ±0,2 |

| Миним. входн. сопротивл. приемника, кОм | 3-7 | |||

| Максим, ток короткого замыкания, мА |

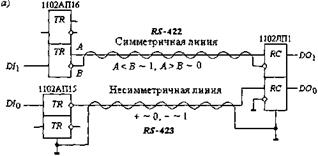

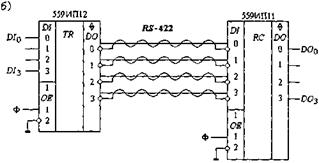

Рис. 42. Линии связи на основе интерфейсов RS-422A и RS-423A.

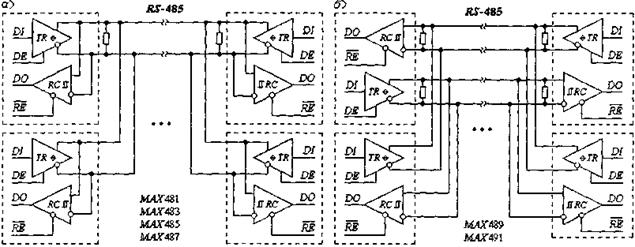

Рис. 43. Линии связи на основе интерфейса RS-485