Регистры состояния и управления

Используя эти регистры можно получать информацию о результате выполнения команд и влиять на состояние самого МП.

Регистр указатель команд IP (Instruction Pointer register)

Регистр содержит смещение (эффективный адрес) следующей подлежащей выполнению команды относительно содержимого сегментного регистра CS в текущем сегменте кода. Напрямую изменять его содержимое нельзя, но процессор делает это сам. При выполнении обычных команд значение IP увеличивается каждый раз на размер выполненной команды. Существуют также команды передачи управления, которые изменяют значение IP для осуществления переходов внутри программы (команды условных и безусловных переходов, вызова процедур и возврата из процедур обработки прерываний и т. д.).

Регистр флагов FLAGS (Flags register)

Отдельные биты данного регистра имеют определенное функциональное назначение и называются флагами (см. рис.2.4).

Имеется три типа флагов: флаги состояния (6 флагов CF, PF, AF, ZF, SF, OF), флаги управления (флаг DF) и системные флаги (флаги TF и IF). Назначение флагов представлено в табл.2.1.

Рис. 2.4. Флаговый регистр процессора Intel 8086

Таблица 2.1. Назначение флагов флагового регистра

| № бита | Обозначение флага | Описание и основное назначение флага |

| CF Флаг переноса (Carry Flag) | 1 – арифметическая операция произвела перенос из старшего бита (результат операции не уместился в приемнике) или заем в старший бит результата; 0 – переноса или заема не было. (старшим является 7, 15 или 31-й бит в зависимости от размерности операнда) (операции над числами без знака) |

Окончание табл. 2.1.

| PF Флаг четности (Parity Flag) | 1 – восемь младших разрядов (младший байт) результата содержат четное число единиц; 0 – восемь младших разрядов результата содержат нечетное число единиц. (этот флаг только для восьми младших разрядов операнда любого размера) | |

| AF Вспом. флаг переноса (Auxiliary Carry Flag) | 1 – арифметическая операция произвела перенос из третьего бита или заем в третий бит результата; 0 – переноса или заема не было. (операции над числами в двоично-десятичном формате) | |

| ZF Флаг нуля (Zero Flag) | 1 – результат операции нулевой; 0 – результат операции ненулевой. | |

| SF Флаг знака (Sign Flag) | 1 – старший бит результата операции равен 1; 0 – старший бит результата операции равен 0. | |

| TF Флаг трассировки (пошаговое выполнение) (Trap Flag) | 1 – после каждой выполненной команды происходит прерывание работы МП и вызов обработчика прерываний; 0 – обычная работа. (предназначен для организации пошаговой работы МП, например, отладчиками) | |

| IF Флаг разрешения прерываний (Interrupt Enable Flag) | 1 – аппаратные (внешние маскируемые) прерывания обрабатываются; 0 – аппаратные (внешние маскируемые) прерывания игнорируются. | |

| DF Флаг направления (Direction Flag) | 1 – обработка от конца строки к ее началу (в порядке убывания адресов, содержимое регистров SI и DI уменьшается); 0 – обработка от начала строки к концу (в порядке возрастания адресов). (используется цепочечными командами (MOVS, CMPS, SCAS, LODS и STOS)) | |

| OF Флаг переполнения (Overflow Flag) | 1 – арифметическая операция привела к переносу (заему) в знаковый (самый старший) бит результата, но не привела к переносу (заему) из самого старшего бита, или наоборот. 0 – переноса или заема не было (результат не выходит за допустимый диапазон). (операции над числами со знака) |

Шина представляет собой группу параллельных проводников, с помощью которых данные передаются от одного элемента микропроцессорной системы к другому. Обычно системная шина компьютера состоит из трех разных шин: шины данных (ШД), шины управления (ШУ) и шины адреса (ША). Шина данных используется для обмена команд и данных между МП, оперативной памятью и устройствами ввода-вывода. По шине управления передаются специальные сигналы, синхронизирующие работу всех устройств, подключенных к системной шине. Шина адреса используется для указания адреса ячейки памяти в ОЗУ или адреса устройства ввода-вывода, к которому в текущий момент происходит обращение со стороны МП. Важной характеристикой шины является ее разрядность, которая определяется, как число бит данных, которое может быть передано за один цикл или такт. У процессоров Intel 8086 размер (разрядность) шины адреса составляет 20 бит (то есть физически 20 проводников). Разрядность шины данных составляет 16 бит.

Оперативная память (оперативное запоминающее устройство (ОЗУ)) (англ. Random Access Memory (RAM) – память с произвольным доступом) – физическая память в которой временно хранятся данные и команды, необходимые процессору для выполнения им операций. ОЗУ организованно как массив ячеек памяти, размер каждой ячейки памяти составляет 1 байт. Каждой ячейке соответствует ее уникальный адрес (номер), который называется физическим адресом. Доступ к ОЗУ осуществляется через ША (на эту шину выставляется адрес той ячейки, к которой необходимо получить доступ на запись или считывание информации (данные, код, стек)) и ШД (по этой шине передаются данные от МП к ОЗУ или в обратном направлении). Следовательно, диапазон доступных значений физических адресов и диапазон доступной памяти определяется разрядностью ША.

В процессорах Intel 8086 разрядность ША составляет 20 бит. Адрес первой доступной ячейки 00000H, адрес последней доступной ячейки FFFFFH. Количество доступных значений физических адресов  можно определить по формуле:

можно определить по формуле:

=

=  , (2.1)

, (2.1)

где  – разрядность шины адреса или выставляемого на шину адреса.

– разрядность шины адреса или выставляемого на шину адреса.

Тогда

=

=  = 1048576 шт.

= 1048576 шт.

Объем адресуемой памяти  , байт, определяется по формуле:

, байт, определяется по формуле:

=

=  , (2.2)

, (2.2)

где  – объем одной ячейки памяти, байт.

– объем одной ячейки памяти, байт.

Тогда (  = 1 байт)

= 1 байт)

=

=  = 1048576 байт = 1 Мбайт.

= 1048576 байт = 1 Мбайт.

Для операционной системы и программ пользователю доступно только порядка 640 Кбайт, остальная память зарезервирована для аппаратной части компьютера (таблица векторов прерываний, видеопамять, BIOS и т.д.).

Однако, как уже отмечалось, процессор Intel 8086 имеет 16-разрядную архитектуру (все регистры 16-разрядные). А адрес конкретной ячейки МП может взять только из регистра. Объем памяти, который можно адресовать этими шестнадцатью разрядами по формулам (2.1) и (2.2) будет составлять

=

=  = 65536 байт = 64 Кбайт.

= 65536 байт = 64 Кбайт.

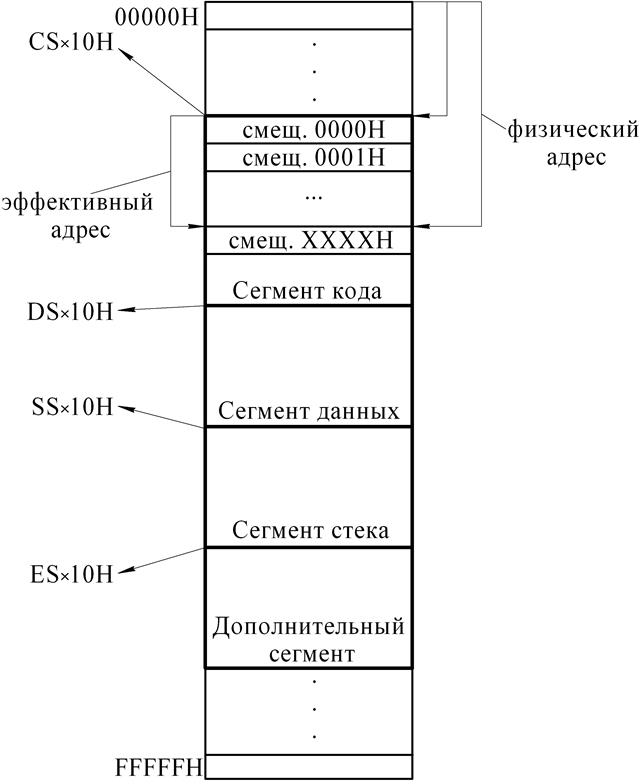

Это несоответствие в процессорах Intel 8086 ликвидируется специальной организацией памяти, называемой сегментированная модель памяти реального режима (режима реальных адресов). Ее схема показана на рис.2.5.

Как уже отмечалось выше программа, при ее размещении в памяти, состоит из сегментов. В общем случае она может состоять из любого количества сегментов, но доступ МП при выполнении программы имеет только к четырем сегментам – сегменту кода, сегменту данных, сегменту стека и дополнительному сегменту данных. Размещает сегменты в памяти операционная система (например, MS-DOS) и определить заранее по каким физическим адресам это произойдет невозможно. Физический адрес (20-разрядный) начала каждого сегмента помещается в соответствующий сегментный регистр (16-разрядный). Однако операционная система размещает сегменты в памяти не случайным образом, а так, чтобы адрес начала сегмента был кратен  =

=  (говорится, что сегмент выравнивается по границе параграфа). В этом случае последние четыре бита адреса начала любого сегмента всегда равны нулю и при записи его в сегментный регистр опускаются. И, наоборот, при обращении МП к началу сегмента эти нули добавляются к адресу путем сдвига значения, содержащегося в сегментном регистре, влево на четыре разряда. Эта операция выполняется аппаратно и для программного обеспечения абсолютно прозрачна.

(говорится, что сегмент выравнивается по границе параграфа). В этом случае последние четыре бита адреса начала любого сегмента всегда равны нулю и при записи его в сегментный регистр опускаются. И, наоборот, при обращении МП к началу сегмента эти нули добавляются к адресу путем сдвига значения, содержащегося в сегментном регистре, влево на четыре разряда. Эта операция выполняется аппаратно и для программного обеспечения абсолютно прозрачна.

Однако возникает необходимость обращения МП к информации внутри любого сегмента. Информация внутри сегмента адресуется относительно начала сегмента, начиная с нуля. Этот относительный адрес называется смещением или эффективным адресом. Понятно, что смещение может быть только 16-разрядным (добавление и опускание нулей здесь уже не имеет смысла, так как нарушится непрерывность сегмента). Следовательно, максимальный размер любого сегмента составляет 64 Кбайт.

Для вычисления физического адреса справедлива формула:

(2.3)

(2.3)

Например, если в сегментном регистре содержится значение  , а смещение составляет

, а смещение составляет  , то физический адрес ячейки памяти, в которой содержится необходимая информация (кода, данные, стек), будет

, то физический адрес ячейки памяти, в которой содержится необходимая информация (кода, данные, стек), будет

.

.

Если в сегментном регистре содержится значение  , и смещение составляет

, и смещение составляет  , то физический адрес ячейки памяти, в которой содержится необходимая информация, будет

, то физический адрес ячейки памяти, в которой содержится необходимая информация, будет

.

.

В этом случае в процессорах Intel 8086 старший бит игнорировался и доступ осуществлялся к информации в старших адресах.

Эффективный адрес (смещение) может браться из самой команды или регистров процессора (BX, SI, DI, BP, IP). Сегментная составляющая адреса (адрес начала сегмента) обычно подставляется по умолчанию исходя из логики команды (при работе с данными по умолчанию подставляется значение регистра DS, с кодом – CS, со стеком – SS).

Данный механизм образования физического адреса позволяет сделать работу программ независимой от конкретных адресов их загрузки в память.

Адрес в памяти состоит из двух составляющих – сегмента и смещения, которые в программах на языке ассемблера записываются в виде:

сегмент:смещение

В частности адрес следующей выполняемой команды находится по адресу CS:IP. Адрес ячейки памяти, откуда или куда необходимо записать данные, определяется как DS:смещение (смещение задается в команде или регистре).

Рис. 2.5. Сегментированная модель памяти реального режима

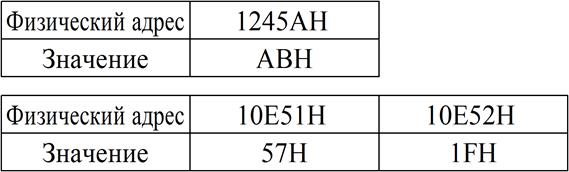

Микропроцессоры Intel имеют важную особенность работы с памятью – младший байт всегда хранится по меньшему адресу. Адресом слова считается адрес его младшего байта. Адрес старшего байта может быть использован для доступа к старшей половине слова.

Например, однобайтовая константа ABH хранится в одной ячейке памяти, например с физическим адресом 1245AH. Если двухбайтовая константа (слово) 1F57H имеет физический адрес 10E51H, то это означает, что по физическому адресу 10E51H хранится младший байт (57H), а старший байт (1FH) хранится по физическому адресу 10E52H (то есть в памяти информация хранится в обратном порядке – см. рис.2.6). То же самое относится к информации, состоящей из большего числа байт.

Рис. 2.6. Расположение данных в памяти

При записи или чтении слова целиком такой переворот выполняется аппаратно (автоматически). Однако указанный момент надо учитывать при обращении к отдельным байтам записанного слова.

Вопросы для самопроверки

1. Какое минимальное и максимальное число без знака можно было бы записать в регистр, если бы он имел только 9 разрядов?

2. Какое минимальное и максимальное число со знаком можно было бы записать в регистр, если бы он имел только 11 разрядов?

3. Регистр AX содержит значение 1A2BH. Что содержит регистр AL?

4. Какой объем памяти можно было бы адресовать в реальном режиме, если бы шина адреса была 18-ти разрядной (ячейка памяти 1 байт)? 8-ми разрядной? 4-х разрядной?

5. Какой объем памяти можно было бы адресовать в реальном режиме, если бы шина адреса была бы 12-ти разрядной, а ячейка памяти имела размер 9 бит?

6. При выполнении программы в регистрах оказались следующие значения: CS = 1AEFH, DS = ABC5Н, IP = 0104H. Какой физический адрес в памяти у следующей к выполнению команды?

7. При выполнении программы в регистрах оказались следующие значения: CS = 1788H, DS = 1599Н, IP = 0BBBH. Смещение данных в сегменте данных равно EEFBH. Какой физический адрес у ячейки памяти, из которой будут считаны данные?

8. Какой регистр можно использовать для подсчета числа циклов?

9. Какой регистр можно использовать для индикации нулевого результата операции?