Условные обозначения, принятые в таблице 3

| ` | - команда оказывает влияние на все признаки |

| `` | - команда оказывает влияние на признак C |

| ``` | - команда оказывает влияние на все признаки, кроме признака C |

| R, R1 | - содержимое регистров A, B, C, D, E, H, L или ячейки памяти M(HL) |

| YZ | - содержимое регистровой пары BC, DE, HL, или регистра SP |

| YZ* | - содержимое регистровой пары BC или DE |

| YZ** | - содержимое регистровой пары BC, DE, HL или PSW |

| SP | - содержимое указателя стека перед выполнением команды |

| D8 | - 8-разрядный операнд (содержимое второго байта команды) |

| (N) | - содержимое порта ввода или вывода с адресом N (N=0,1,…, 255) |

| D16 | - 16-разрядный операнд (содержимое второго и третьего байтов команды) |

| ADR | - 16-разрядный адрес в трехбайтовой команде |

| M( ) | - содержимое ячейки памяти (адрес указан в скобках) |

| -CON | - часть мнемоники команды, определяющая условие передачи управления, вызова и возврата из подпрограммы (-CON в мнемонике заменяется на NZ, Z, NC, C, PO, PE, P или M-) |

Команда DAA предназначена для выполнения операции двоично-десятичного сложения (команда десятичной коррекции).

Очень часто при написании программ используются команды INR R, DEC R, INR M, DEC M, INX YZ, DCX YZ, служащие для увеличения или уменьшения содержимого регистра микропроцессора R, ячейки памяти M или регистровой пары YZ. Многие команды этой группы воздействуют на различные биты регистра признаков F.

Группа команд арифметических и логических операций с двумя операндами.Перед началом выполнения любой команды из этой группы один из операндов должен быть помещен в регистр A, а другой операнд (если команда однобайтовая) в один из внутренних регистров микропроцессора или ячейку памяти, адресуемую содержимым регистровой пары HL. В двухбайтовой команде значение второго операнда непосредственно задается во втором байте команды. Результат выполнения команды помещается в регистр A.

Команды ADD R, ADD M или ADI D8 позволяют сложить два операнда. Сложение двух операндов со значением признака переноса C происходит по команде ADC R, ADC M или ACI D8. Вычитание из содержимого аккумулятора второго операнда и учет значения бита заема производится соответственно командами SUB R, SUB M, SUI D8, SBB R, SBB M или SBI D8.

Операции поразрядного логического умножения (операция “И”) содержимого аккумулятора со вторым операндом происходит при выполнении команд ANA R и ANI D8. При этом результатом выполнения является двоичное 8-разрядное число, отдельные разряды которого равны 1 только тогда, когда соответствующие разряды у обоих операндов тоже равны 1.

При выполнении поразрядного логического сложения (операция “ИЛИ”) с помощью команд ORA R или ORA D8 образуется двоичное число, отдельные разряды которого равны 1 если хотя бы у одного из операндов или у обоих операндов соответствующий разряд равен 1.

Результатом выполнения операции “ИСКЛЮЧАЮЩЕЕ ИЛИ” командами XRA R или XRI D8 является байт, отдельные разряды которого равны единице в случае, когда соответствующие разряды операндов имеют противоположные значения.

После выполнения рассмотренных команд логической обработки двух операндов значения признаков C и AC регистра признаков всегда равны 0.

Команды CMP R и CPI D8 позволяют сравнивать два операнда. Сравнение происходит вычитанием из первого операнда, хранящегося в аккумуляторе, второго. Если в результате операции вычитания окажется, что операнды равны, то признак нуля Z устанавливается в 1, если же значение операнда, хранящегося в аккумуляторе, меньше значения второго операнда, устанавливается в 1 признак переноса C.

Есть в системе команд микропроцессора команды DAD B, DAD D, DAD H, DAD SP, позволяющие сложить два 16-разрядных числа. Одно из этих чисел должно быть записано в регистровую пару HL, а другое – регистровую пару BC, DE, HL или SP. Результат операции помещается в пару HL.

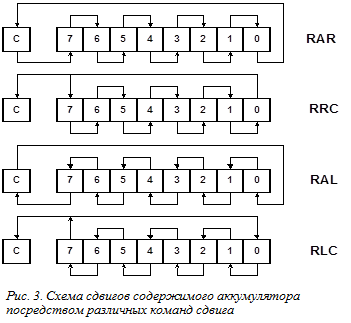

Группа команд сдвигов содержимого аккумулятора. На рис 3 схематически показано, как происходит сдвиг содержимого аккумулятора влево или вправо командами сдвига RAL или RAR и командами циклического сдвига RLC и RRC. В операциях сдвига участвует бит переноса C регистра признаков F Под воздействием каждой из этих команд происходит сдвиг содержимого аккумулятора только на один разряд. Если необходимо сдвинуть содержимое аккумулятора на большее число разрядов, то команду следует повторить требуемое число раз.

Группа команд сдвигов содержимого аккумулятора. На рис 3 схематически показано, как происходит сдвиг содержимого аккумулятора влево или вправо командами сдвига RAL или RAR и командами циклического сдвига RLC и RRC. В операциях сдвига участвует бит переноса C регистра признаков F Под воздействием каждой из этих команд происходит сдвиг содержимого аккумулятора только на один разряд. Если необходимо сдвинуть содержимое аккумулятора на большее число разрядов, то команду следует повторить требуемое число раз.

Группа команд передачи управления и работы с подпрограммами. Эти команды играют особую роль в организации выполнения программ. Пока в программе не встречаются команды этой группы, счетчик команд PC постоянно увеличивает свое значение, и микропроцессор выполняет команду за командой в порядке их расположения в памяти.

Порядок выполнения программы может быть изменен, если занести в регистр счетчика команд микропроцессора код адреса, отличающийся от адреса очередной команды. Это вызовет передачу управления работой микропроцессора другой части программы. Такая передача управления (или переход в программе) может быть выполнена с помощью трехбайтовой команд безусловного перехода – JMP ADR. Как только такая команда встретится в программе, в регистр счетчика команд PC микропроцессора запишется ADR. Таки образом, следующей командой, которую будет выполнять микропроцессор за командой JMP ADR, будет команда, код операции которой записан в ячейке с адресом, равным значению ADR.

Безусловную передачу управления можно осуществить также с помощью команды PCHL, в результате выполнения которой произойдет передача управления по адресу, хранящемуся в регистровой паре HL.

Кроме команд безусловного перехода микропроцессор КР580ВМ80А имеет восемь трехбайтовых команд условного перехода. При появлении команды условного перехода передача управления по адресу, указанному в команде происходит только в случае выполнения определенного условия. Если условие не удовлетворяется, то выполняется команда, непосредственно следующая за командой условного перехода.

Условия, с которыми оперируют команды условной передачи управления, определяются состоянием битов (разрядов) регистра признаков F:

| NZ (NOT ZERO) | - ненулевой результат Z = 0 |

| Z (ZERO) | - нулевой результат Z = 1 |

| NC (NOT CARRY) | - отсутствие переноса, CY = 0 |

| C (CARRY) | - перенос, CY = 1 |

| PO (PARITY ODD) | - нечетный результат, P = 0 |

| PE (PARITY EVEN) | - четный результат, P = 1 |

| P (PLUS) | - число неотрицательное, S = 0 |

| M (MINUS) | - число отрицательное, S = 1 |

Эти условия проверяются командами перехода JNZ ADR, JZ ADR, JNC ADR, JC ADR, JPO ADR, JPE ADR, JP ADR, JM ADR соответственно.

При написании программ, обычно можно выделить одинаковые последовательности команд, часто встречающиеся в разных частях программы. Для того, чтобы многократно не переписывать такие последовательности команд, их объединяют в подпрограммы. В любой части основной программы программист может поставить трехбайтовую команду безусловного вызова подпрограммы CALL ADR, во втором и третьем байте которой указывается адрес вызываемой подпрограммы. Выполнение команды CALL ADR начинается с побайтовой засылки в стек адреса следующей после этой команд ячейки памяти. Этот адрес называется адресом возврата из подпрограммы. Он необходим для того, чтобы по окончании выполнения подпрограммы вернуться к продолжению выполнения основной программы.

После записи в стек адреса возврата из подпрограммы в счетчик команд PC МП загружается величина ADR, т.е. адрес первой команды вызываемой подпрограммы. Таким образом, управление передается вызываемой подпрограмме.

Выполнение подпрограммы всегда заканчивается командой возврата из подпрограммы, например, однобайтовой командой безусловного возврата из подпрограммы RET. При этом содержимое стека, т.е. адрес возврата из подпрограммы пересылается из стека в программный счетчик PC микропроцессора и управление вновь передается основной программе.

Кроме трехбайтовой команды безусловного вызова подпрограммы CALL ADR, в системе команд МП имеется восемь однобайтовых команд RST 0 – RST 7 вызова подпрограмм, расположенных по фиксированному адресу. Появление в основной программе любой из этих команд вызывает запись в стек возврата из подпрограммы и передачу управления на соответствующую ячейку памяти, где расположена первая команда подпрограммы. В таблице 4 дано соответствие между командами RST 0 – RST 7 и шестнадцатеричными адресами ячеек памяти, куда передается управление при их выполнении.

Таблица 4