Разработка функциональной схемы

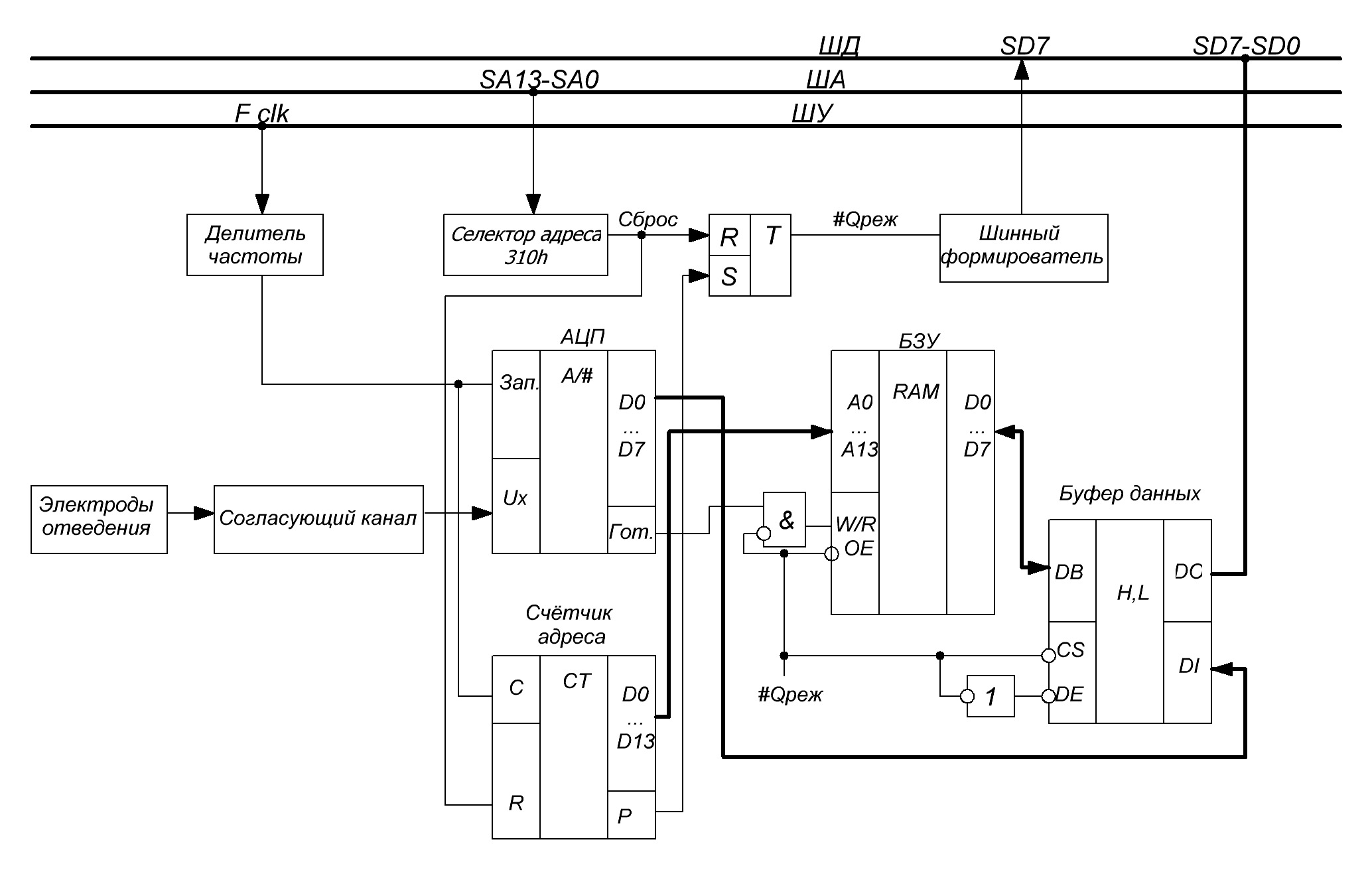

На основании ТЗ разработаем функциональную схему устройства. Для этого представим разрабатываемое устройство в виде функциональных узлов.

3.1 Согласующий канал

Входной сигнал прибора имеет максимальную амплитуду 30 мВ и может включать в себя высокочастотные помехи. Это обуславливает необходимость применения согласующего канала, в котором будет реализовано усиление и фильтрация входного сигнала. Также согласующий канал будет обеспечивать высокое входное сопротивление канала.

3.2 АЦП

Для выполнения главной функции устройства – преобразования сигнала из аналоговой формы в цифровую – используем АЦП. Разрядность и частоту дискретизации АЦП выберем в соответствии с расчётами, приведёнными в предыдущем пункте. Для дальнейших расчётов выберем диапазон входных сигналов АЦП. Практически во всех современных АЦП он задаётся с помощью подачи опорного напряжения требуемой величины на соответствующий вход АЦП. Шиной ISA уже предусмотрено наличие питания 5 В, поэтому зададим его в качестве опорного, чтобы не разрабатывать отдельный источник напряжения.

3.3 Счётчик адреса

Для генерации адреса ячейки памяти, в которой будет храниться отсчёт, будем использовать счётчик адреса. Счётчик адреса должен иметь выход сигнала переполнения, служащий индикатором того, что все отсчёты сигнала оцифрованы.

3.4 Буферное запоминающее устройство

Для временного хранения снятых отсчётов используем буферное запоминающее устройство. Объем памяти устройства выберем в соответствии с расчётами, приведёнными в предыдущем пункте.

3.5 Буфер данных

Для записи оцифрованных отсчётов из АЦП в БЗУ и передачи хранимой в БЗУ информации в память ПК необходимо использовать буфер данных. Также необходимо будет использовать делитель частоты, выполняющий преобразование тактовой частота шины ISA в частоту дискретизации АЦП. Коэффициент деления частоты  . Такой коэффициент деления можно получить, используя счётчик.

. Такой коэффициент деления можно получить, используя счётчик.

Рисунок 1 – Функциональная схема разрабатываемого прибора

Схема работает следующим образом [8]. Вначале реализуется работа схемы в режиме 1 – оцифровка аналогового сигнала, поступающего с электродов отведения через согласующий канал, с записью цифровых эквивалентов в БЗУ. В режиме 2 (чтение БЗУ) сформированные данные из БЗУ передаются под управлением программы в основную память МПС (ОЗУ). Смена режимов задаётся программно. Фиксация режима производится путём установки триггера в значение Qреж = 0 (режим 1) или Qреж = 1 (режим 2). Установка триггера в ноль производится сигналом «Сброс» от ядра МПС, установка в единицу – сигналом переноса, выдаваемым счётчиком адреса после формирования им всех адресов от 0 до (214 – 1) включительно и соответственно завершения цикла записи в БЗУ всех отсчётов сигнала. Установка триггера в единицу свидетельствует о том, что массив данных в БЗУ полностью сформирован (преобразование завершено). Процессор МПС анализирует бит режима Qреж, и если он равен единице, то система считывает данные из БЗУ в ОЗУ ядра МПС.

В режиме 1 формирование адресов производится с частотой fД, в режиме 2 – с частотой следования сигналов ЧтВУ, обеспечивающих передачу данных из выбранной ячейки БЗУ в память ядра через буферную схему F.

4 Разработка, описание и расчёт принципиальной схемы