Типовые комбинационные цифровые устройства

Рисунок 2.1 – Логическая схема, поясняющая механизм возникновения статического риска в КЦУ (а) и временные диаграммы ее работы (б, в и г)

Рисунок 2.2 – Условное графическое обозначение двоичного дешифратора со входом разрешения

Таблица 2.1 – Таблица истинности двоичного дешифратора

| Логические аргументы | Логические функции | |||||

| x1 | x2 | y0 | y1 | y2 | y3 |

| x | x | |||||

| Примечание – Знаком «x» обозначен произвольный сигнал (0 или 1). |

Рисунок 2.3 – Логическая схема двоичного дешифратора со входом разрешения

Рисунок 2.4 – Упрощенная логическая схема двухступенчатого дешифратора при n = 4

Рисунок 2.5 – Схема наращивания разрядности двоичного дешифратора

Рисунок 2.6 – Условное графическое обозначение двоичного шифратора

Таблица 2.2 – Таблица истинности двоичного шифратора

| Логические аргументы | Логические функции | ||||

| y0 | y1 | y2 | y3 | x1 | x2 |

Рисунок 2.7 – Логическая схема двоичного шифратора

Рисунок 2.8 – Условное графическое обозначение микросхемы приоритетного шифратора К555ИВ1

Рисунок 2.9 – Условное графическое обозначение преобразователя кода 8421 в код с избытком 3

Таблица 2.3 – Таблица истинности преобразователя кода 8421 в код 2421

| Логические аргументы | Промежуточная переменная | Логические функции | ||||||

| x3 | x2 | x1 | x0 | zi | y3 | y2 | y1 | y0 |

| z0 | ||||||||

| z1 | ||||||||

| z2 | ||||||||

| z3 | ||||||||

| z4 | ||||||||

| z5 | ||||||||

| z6 | ||||||||

| z7 | ||||||||

| z8 | ||||||||

| z9 |

Рисунок 2.10 – Карты Карно для преобразователя кода 8421 в код с избытком 3

Рисунок 2.11 – Логическая схема ПК 8421 в код с избытком 3 в основном базисе

Рисунок 2.12 – Преобразователь кода с частично регулярной структурой

Рисунок 2.13 – Преобразователь кода на основе ПЗУ

Рисунок 2.14 – Условное графическое обозначение одноразрядного мультиплексора для m = 4

Таблица 2.4 – Таблица истинности одноразрядного мультиплексора для m = 4

| Логические аргументы | Логическая функция | |||||

| x0 | x1 | x2 | x3 | а1 | а0 | y |

| x x | x x | x x | ||||

| x x | x x | x x | ||||

| x x | x x | x x | ||||

| x x | x x | x x |

Рисунок 2.15 – Одноразрядный мультиплексор для m=4. Логическая схема неструктурированная (а) и структурированная (б)

Окончание рисунка 2.15

| MUX1 |

Рисунок 2.16 – Схема наращивания числа информационных входов мультиплексора

Рисунок 2.17 – Схема реализации неравнозначности при настройке УЛМ константами

Рисунок 2.18 – Условное графическое обозначение одноразрядного демультиплексора для m = 4

Таблица 2.5 – Таблица истинности одноразрядного демультиплексора для m = 4

| Логические аргументы | Логические функции | |||||

| x | a1 | a0 | y0 | y1 | y2 | y3 |

а)

б)

Рисунок 2.19 – Одноразрядный демультиплексор.

Логическая схема неструктурированная (а) и структурированная (б)

Рисунок 2.20 – Условное графическое обозначение ОДС

Таблица 2.6 – Таблица истинности ОДС

| Логические аргументы | Логические функции | |||

| ai | bi | ci | si | ci+1 |

Рисунок 2.21 – Минимизация функций ОДС. Карты Карно для выхода суммы si (а) и выхода переноса ci+1 (б)

Рисунок 2.22 – Логическая схема ОДС

Рисунок 2.23 – Логическая схема МДС последовательного действия

Рисунок 2.24 – Логическая схема МДС параллельного действия с последовательным переносом

Рисунок 2.25 – Функциональная схема четырехразрядной секции сумматора с ускоренным (параллельным) переносом

Рисунок 2.26 – Базовая структура ПЛМ

Рисунок 2.27 – Схема ПЛМ на вентильном уровне

Рисунок 2.28 – ПЛМ схемотехники ТТЛШ. Элементы связей в матрицах И (а) и ИЛИ (б)

Триггерные устройства

Таблица 2.7 – Условное графическое обозначение входов синхронизации С и временные диаграммы процессов переключения

| Тип входа С | Условное графическое обозначение | Временные диаграммы процессов переключения |

| Прямой статический | ||

| Инверсный статический | ||

| Прямой динамический | ||

| Инверсный динамический | ||

| Инверсный статический |

Рисунок 2.29 – Определение параметров предустановки и выдержки для синхронных триггеров

Рисунок 2.30 – Условное графическое обозначение асинхронного RS-триггера

Таблица 2.8 – Таблица состояний асинхронного RS-триггера

| Логические аргументы | Логическая функция | Режим работы | ||

| Qn | Sn | Rn | Qn+1 | |

| 0 1 | 0 0 | 0 0 | 0 1 | Хранение |

| 0 1 | 1 1 | 0 0 | 1 1 | Установка 1 Подтверждение 1 |

| Подтверждение 0 Установка 0 | ||||

| Ф Ф | Неопределенность | |||

| Примечания 1 «Qn» – предыдущее состояние триггера. 2 «Qn+1» – следующее состояние триггера. |

Рисунок 2.31 – Карты Карно для минимизации выходных функций асинхронного RS-триггера в ДНФ.

Рисунок 2.32 – Логические схемы асинхронного RS-триггера в базисе ИЛИ-НЕ

Таблица 2.9 – Таблица переходов RS-триггера

| Текущее состояние | Следующее состояние | Требуемые состояния входов | |

| Qn | Qn+1 | Sn | Rn |

| X | X |

Рисунок 2.33 – Временные диаграммы работы асинхронного RS-триггера в базисе ИЛИ-НЕ

Рисунок 2.34 – Логические схемы асинхронного R̅S̅-триггера на элементах И-НЕ (а, б, в) и условное графическое обозначение (г)

Таблица 2.10 – Таблица состояний асинхронного R̅S̅-триггера.

| Логические аргументы | Логическая функция | Режим работы | ||

| Qn | R̅n | S̅n | Qn+1 | |

| 0 1 | 1 1 | 1 1 | 0 1 | Хранение |

| 0 1 | 0 0 | 1 1 | 0 0 | Подтверждение 0 Установка 0 |

| 0 1 | 1 1 | 0 0 | 1 1 | Установка 1 Подтверждение 1 |

| 0 1 | 0 0 | 0 0 | Ф Ф | Неопределенность Неопределенность |

Рисунок 2.35 – Синхронный RS-триггер со статическим управлением.

Структурная схема (а) и логическая схема (б)

Таблица 2.11 – Таблица состояний синхронного RS-триггера, совмещенная с таблицей истинности комбинационной схемы.

| Логические аргументы | Логические функции | Режим работы | |||||

| Cn | Qn | Sn | Rn | Qn+1 | S̅n | R̅n | |

| 0 0 | 0 1 | 0 0 | 0 0 | 1 Х | Х 1 | Хранение | |

| 0 0 | 0 1 | 1 1 | 0 0 | 0 1 | 1 Х | Х 1 | |

| 0 0 | 0 1 | 0 0 | 1 1 | 0 1 | 1 Х | Х 1 | |

| 0 0 | 0 1 | 1 1 | 1 1 | 0 1 | 1 Х | Х 1 | |

| 1 1 | 0 1 | 0 0 | 0 0 | 0 1 | 1 Х | Х 1 | Хранение |

| 1 1 | 0 1 | 1 1 | 0 0 | 1 1 | 0 Х | 1 1 | Загрузка 1 Подтверждение 1 |

| 1 1 | 0 1 | 0 0 | 1 1 | 0 0 | 1 1 | Х 0 | Подтверждение 0 Загрузка 0 |

| 1 1 | 0 1 | 1 1 | Ф Ф | Х Х | Х Х | Неопределенность |

Рисунок 2.36 – Карты Карно для функций S̅n и R̅n синхронного RS-триггера со статическим управлением

Рисунок 2.37 – Синхронный RS-триггер на элементах И-НЕ. условное графическое обозначение (а) и логическая схема (б)

Рисунок 2.38 – Синхронный D-триггер со статическим управлением на элементах И-НЕ. Структурная схема (а) и логическая схема (б)

Таблица 2.12 – Таблица состояний синхронного D-триггера со статическим управлением, совмещенная с таблицей истинности комбинационной схемы

| Логические аргументы | Логические функции | Режим работы | ||||

| Сn | Dn | Qn | Qn+1 | S̅n | R̅n | |

| X X | X X | Хранение | ||||

| X | X | Подтверждение 0 Загрузка 0 Загрузка 1 Подтверждение 1 |

Рисунок 2.39 - Карты Карно для функций S̅n и R̅n синхронного D-триггера со статическим управлением

Рисунок 2.40 – Карта Карно для функции R̅n синхронного D-триггера со статическим управлением

Рисунок 2.41 – Синхронный D-триггер со статическим управлением. Логическая схема (а) и условное графическое обозначение (б)

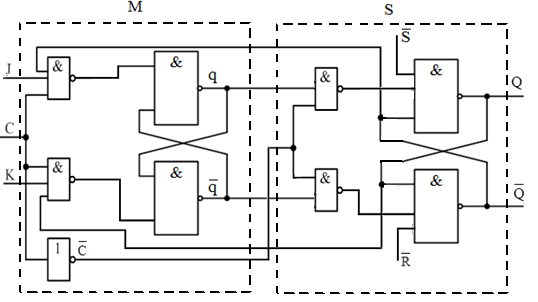

Рисунок 2.42 – JK-триггер со статическим управлением. Структурная схема (а) и логическая схема (б)

Таблица 2.13 – Таблица состояний JK-триггера со статическим управлением, совмещенная с таблицей истинности комбинационной схемы

| Логические аргументы | Логические функции | Режим работы | |||||

| Сn | Qn | Jn | Kn | Qn+1 | S̅n | R̅n | |

| X | X | Хранение | |||||

| X | X | ||||||

| X | X | ||||||

| X | X | ||||||

| X | X | Хранение | |||||

| X | Загрузка 1 Подтверждение 1 | ||||||

| X | Подтверждение 0 Загрузка 0 | ||||||

| Переключение (счетный) |

Рисунок 2.43 – Карты Карно для JK-триггера со статическим управлением

Рисунок 2.44 – Двухступенчатый JK-триггер с инвертором

Рисунок 2.45 – Условное графическое обозначение двухступенчатого JK-триггера со статическим управлением

Рисунок 2.46 – Т-триггер на основе JK-триггера (а) и D-триггера (б)

Таблица 2.14 – Таблицы переходов D- и T-триггеров

| Текущее состояние | Следующее состояние | D-триггер | Т-триггер |

| Qn | Qn+1 | Dn | Tn |

| 0 0 1 1 | 0 1 0 1 | 0 1 0 1 | 0 1 1 0 |

Рисунок 2.47 – Т-триггер на основе D-триггера

Рисунок 2.48 – Схема делителя частоты на два на основе D-триггера (а) и его временные диаграммы (б)

Рисунок 2.49 – Синхронный D-триггер с динамическим управлением.

Условное графическое обозначение (а) и логическая схема (б)

Регистры памяти и сдвига

Рисунок 2.50 – Параллельный регистр на D-триггерах с прямым динамическим входом синхронизации. Условное графическое обозначение (а) и логическая схема (б)

а)

Рисунок 2.51 — Регистр сдвига со сдвигом вправо на D-триггерах с прямым динамическим входом синхронизации. Условное графическое обозначение (а) и логическая схема (б)

б)

Окончание рисунка 2.51

Рисунок 2.52 — Временные диаграммы при сдвиге вправо кодового слова 1000 (DSR=0)

Рисунок 2.53 – Четырехразрядный счетчик Джонсона. Логическая схема (а) и временные диаграммы работы (б)

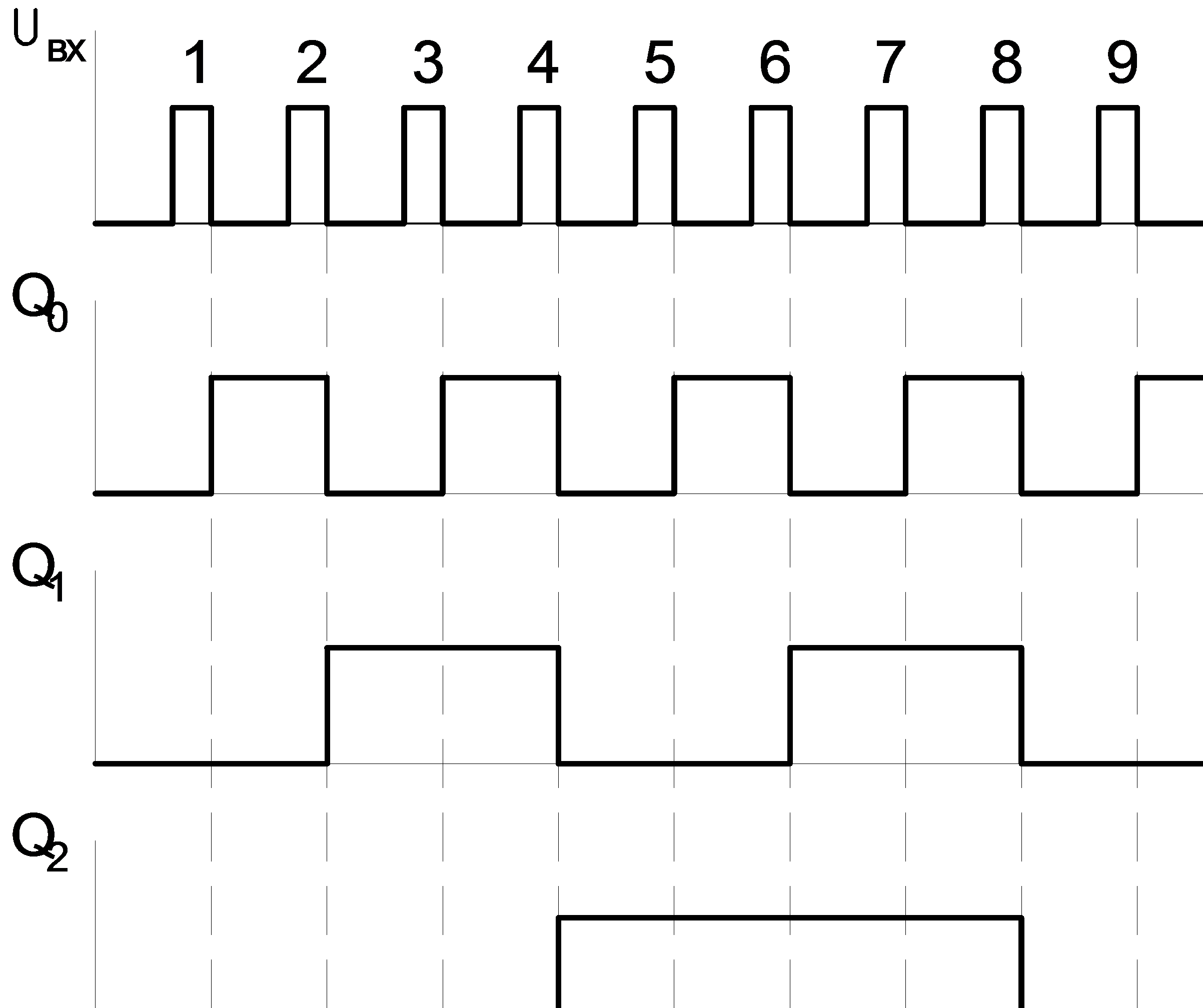

Счетчики и делители частоты

| Суммирующие выходы |

| Вычитающие выходы |

б)

Рисунок 2.54 — Четырехразрядный асинхронный двоичный суммирующий счетчик с последовательным переносом на JK-триггерах. Условное графическое обозначение (а) и логическая схема (б)

Таблица 2.15 – Таблица состояний двоичного счетчика

| Номер входного импульса | Режим сложения | Режим вычитания | ||||||

| Q3 | Q2 | Q1 | Q0 | Q̅3 | Q̅2 | Q̅1 | Q̅0 | |

| … | … | … | … | … | … | … | … | … |

Рисунок 2.55 – Временные диаграммы, поясняющие работу четырехразрядного двоичного суммирующего счетчика

Таблица 2.16 – Таблица состояний для i-го разряда синхронного счетчика с параллельным переносом

| Логические аргументы | Логические функции | ||

| Qi | Ci | Qi+1 | Ci+1 |

| Примечания «Qi» – предыдущее состояние триггера i – го разряда; «Ci» – перенос на информационном входе Т триггера i – го разряда; «Qi+1» – следующее состояние триггера i – го разряда; «Ci+1» – перенос в соседний старший разряд. |

Рисунок 2.56 – Логическая схема четырехразрядного синхронного двоичного суммирующего счетчика с параллельным переносом

Рисунок 2.57 — Упрощенная логическая схема восьмиразрядного синхронного двоичного счетчика с групповым переносом

Рисунок 2.58 – Условное графическое обозначение микросхемы счетчика ЭКР1554ИЕ18

Таблица 2.17 – Таблица состояний микросхемы счетчика ЭКР1554ИЕ18

| Входы | Выходы | Режим работы | |||||||

|  | СЕР | СЕТ | С | Q3 | Q2 | Q1 | Q0 | |

| X | X | X | ↑ | Сброс на «0» | |||||

| X | X | ↑ | D3 | D2 | D1 | D0 | Предустановка | ||

| ↑ | Счет на увеличение | Счет | |||||||

| X | ↑ | Без изменений | Хранение | ||||||

| X | ↑ | ||||||||

| X | X | X | ↓ | ||||||

| Примечание – «Х» - произвольный уровень сигнала (0 или 1). |

Таблица 2.18 – Таблица переходов JK-триггера

| Вид перехода триггера | Уровни сигналов на входах | |

| J | K | |

| 0 ® 0 | X | |

| 0 ® 1 | X | |

| 1 ® 0 | X | |

| 1 ® 1 | X |

Таблица 2.19 – Таблица состояний счетчика с коэффициентом пересчета Кпер = 10, совмещенная с таблицей истинности для входов J и K триггеров.

| Номер входного импульса | Текущее состояние | Следующее состояние | Уровни сигналов на входах триггеров | ||||||||||||||

| Q3 | Q2 | Q1 | Q0 | Q3 | Q2 | Q1 | Q0 | J3 | K3 | J2 | K2 | J1 | K1 | J0 | K0 | ||

| X | X | X | X | ||||||||||||||

| X | X | X | X | ||||||||||||||

| X | X | X | X | ||||||||||||||

| X | X | X | X | ||||||||||||||

| X | X | X | X | ||||||||||||||

| X | X | X | X | ||||||||||||||

| X | X | X | X | ||||||||||||||

| X | X | X | X | ||||||||||||||

| X | X | X | X | ||||||||||||||

| X | X | X | X |

Рисунок 2.59 – Карты Карно для двоично-десятичного счетчика

Окончание рисунка 2.59

Рисунок 2.60 – Логическая схема синхронного двоично-десятичного счетчика на JK-триггерах

Рисунок 2.61 – Временные диаграммы, поясняющие работу синхронного двоично-десятичного счетчика

Рисунок 2.62 – Счетчик с управляемым асинхронным сбросом с коэффициентом пересчета Кпер = 10 на основе микросхемы ЭКР1554ИЕ23. Схема включения (а) и временные диаграммы работы (б)