Pentium II,Pentium Pro

УРК- устр распред команд.

Процессор имеет суперскалярную архитектуру и на кристалле располагается двухуровневая КЭШ. 16кб КЭШ команд и 16кб КЭШ данных. КЭШ 2-го ур-ня (общая)(128k-2mb). Одновременно работают до5-ти аппаратных ресурса (5 команд может выполн одновременно). Проц имеет 11-ти ступ конвейер т.е. все команды выполняются за 11 тактов. Команда из КЭШ памяти поступает в ДШК, УРК формирует блоки из кодов команд и операндов ктр загружаются в пул команд, ДШ команд из цикла выбирает те команды которые для которых определены операнды и есть свободные аппаратные ресурсы, команды выполн аппаратными ресурсами и возвращаются обратно в пул команд. Блок отката выбирает из пула команд выполненные ком-ды и восстанавливает последовательность выполнения команд в соотв с программой. Результат отправляется в КЭШ данных 1-го уровня.

Процессор относится к разряду машин управляемых потоком данных. Проц имеет несколько напряж питания : вычислительное ядро запитывается напряж-ем 2,3В, микросхема обвязки (внешний уровень) повышенным, мощность потребл достигает 40Вт. Прой имеет встроенный датчик температуры и встроенный АЦП, а также требует внешней системы охлаждения. Потребляемый ток 15-20 А.

Pentuim IV

Внутренняя архитектура гарвардского типа (раздельная память команд и память данных), наличие КЭШ 2-го уровня на одном кристалле (в PIII для этого использовался отдельный кристалл). Конвейерное выполнение команд(20-ти ступенчатый конвейер). Суперскалярная архитектура (одновременное выполнение нескольких команд на разных аппаратных ресурсах. Спекулятивное (опережающее) выполнение команд (машина управляемая потоком данных)

БЦР- блок целочисленных регистров

FPU- сопроцессор с плавающей запятой

MMX-Multi Media Extraction

Процессор обращается к внешн модулям памяти и с СМ с мах скоростью записывает коды команд и операнды в КЭШ 2-го уровня. Блок трансляции адресов выбирает код следующей команды. Здесь же команда предварительно дешифрир и если это команда усл или безусл перехода вкл блок предсказания ветвления переходов в котором хранится 4к(4096) адресов последних переходов. Есть 2 дополн бита в адресах которые сигнализируют том как часто происх ветвление по данному адресу.

11-почти всегда

10-часто

01-редко

00-практически никогда

Если по адресу обратились то увел на 1, если не угадали то -1.

При обращении по предсказанному адресу код адреса автомати-чески инкрементируется (мах 11 так и остается) Если обращение по адр не произошло происх декрементация. (min 00).

ДШК дешифрирует очередную команду, из управляющей памяти микропрограмм выбир-ся последовательность МК, которая запис в КЭШ м/команд. Блок распр регистров выбирает свободнее регистры(или те которые указаны в командах) которые требуются для выполнения данной команды. Выбранные МК ставятся в очередь МК, в очереди нах-ся до 126 МК это позволяет блоку распредел ресурсов выбирать из очереди МК те МК для которых свободны аппаратные ресурсы(спекулятивная выборка команд). 126 МК позволяют заглянуть вперед на 40 команд ассемблера.

SISD - 1 команда - 1 данные(32р слова)

SISD - 1 команда - 1 данные(32р слова)

SIMD – 1 команда –группа данных

64 разр Рг=1х64р/слова=2х32р/слова=

=8хр/слова. В команде до 8 байтовых данных.

В БУР содержится 128-32р регистровю Блок ММХ содержит 8ММХ (0..7) 64 разр регистров для реализации функций SIMD арифметики с фикс запятой.

Блок FPU содержит SI(0..7)-64 разр регистра.

SEE –предназначен для реализации команд SIMD арифм с плавающ запятой SEE(0..7) -128р рег-ров.

Главная задача процессора (РIV) обработка мультимедийный приложений.

Результат выполненный в одном из аппар ресурсов помещ к КЭШ 1-го ур-ня. Последовательность восстановл требуемой цепочки команд осущ двумя блоками формирования адреса (БФА)(Блок отката для РII)

| Вид приложения | Повышение производ по сравн с PIII |

| 1)Обработка целых чисел(Spec Int200) | 23% |

| 2)Обработка чисел с плавающ запятой (Spec fp2000) | 79% |

| 3)Кодирование аудио сигналов MP3 Plud 1.3 | 25% |

| 4)Распознавание речи | 27% |

| 5)3D игры (Quake III) | 44% |

ППИ

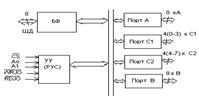

Микросхема КР580ВВ55. ППИ предн. для подкл. периферийных устройств к СМ.

Все 4 канала независимы друг от друга и могут использ. как на ввод так и на вывод инфы. Порт- совокупность регистра и ШФ. РУС –регистр управляющего слова.

| ШД®А | ШД→В | ШД→С | ШД→РУС | |

| CS | ||||

| WRJO | ||||

| RDJO | ||||

| A0 | ||||

| A1 |

| ШД→А | ШД→В | ШД→С | |

| CS | |||

| WRJO | |||

| RDJO | |||

| A0 | |||

| A1 |

ППИ может раб-ть в одном из 3 режимов. Режим задается в регистре управляющего слова (РУС).

РУС

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

D0-к С1 (0-ввод 1- вывод;)

D1-к В (0-ввод 1- вывод;)

D2- реж работы кВ и кС1 (0-реж “0”,1-реж “1”)

D3-к С2 (0-ввод 1- вывод;)

D4-к А (0-ввод 1- вывод;)

D5D6-номер режима для кА и кС2 (00-“0”)(01-“1”)(1х-“2”)

D7-1 признак РУС

Режим “0” предн. для синхронных обменов инфой, каждый из каналов независимо друг от друга может передавать или принимать сигналы в зависимости от РУС.

Режим “1” предн. для асинхронного обмена. В этом режиме данные передаются по каналам А и В, канал С исп-ся для формирования битов квитирования.

Если в режиме 0 или 1 требуется поменять направление передачи инфы ППИ необходимо перепрогр-ть(тратится время). Для скоростного обмена инф-й исп-ся режим 2. В режиме 2 данные могут передаваться только по каналу А. Напр. передачи опред-ся сигналами RDJO, WRJO.

Порт С используется для формирования битов квитирования. В любом из режимов возм-на побитная установка канала С. В этом случае обращение происходит по адресу упр слова А0А1=1 ат только в РУС старший бит=0 (D7=0).

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

D0-то что нужно записать D3D2D1-двоичный номер разр в кан С.

М/О ч/з ППИ.

По сбросу проц-ры программируют ППИ в режим 0 (или 1). Каналы С1 и С2 прогр-ся на передачу слов состояния(битов квитирования => асинхр способ обиена). Каналы А и В на ввод или вывод инфы, чтобы не изменять ПО для 2-х однотипных устройств в кабеле м/у ППИ делается перекоммутация канала А на В и наоборот, тогда сохр-ся направление передачи инф-ии.

Организация м/о n-машин ч/з ППИ.

Пр-р1 – ведущий, все остальные ведомые. По вкл-ю питания пр-р1 прогр-т ППИ в режим 0, к-лы В и С настраиваются на вывод, кА на ввод – вывод. Пр-р1 записывает в кВ адрес внешнего устройства (с помощью ППИ формируется новая СМ, отдельная для внешних устройств).Если Пр-р1 надо получить инфу от внешнего уст-ва, то пр-р1 записывает в кС бит RD*. Комбинация адреса Дш1 и сигнал RD* открывает шинный формирователь N и инфа от регистра пр-ра N поступает в кА ППИ (в этом случае кА настроен на ввод).Пр-р N ч/з шинный формирователь может периодически считывать предназначенные для него инфу кА. Количество машин в этом случае ограничено загруженностью портов ППИ и длиной линии связи.

Обмен инфы последовательным кодом.

При передаче инфы на большие расстояния число линий связи ограничено(радиоканал, оптоволокно). В этом случае передача инфы идет в последовательном коде. При передаче инфы следует решить следующие задачи:

1)опр-ть сост. получ. инфы (выкл.,занят, свободен)

2)опр-ся направление передачи инфы

3)достоверность переданной инфы

4)преобр-ть парал.код в послед. и наоборот.

УСАПП

ПРД-передатчик, ПРМ-приемник сх.синхронизации,

С/D=А0-команда или данные(1 и 0), WRJ0-запись на внешнее устройство, CLC-тактовая чостота, DTR-запрос готовности передатчика ВУ, СTS-готовность приемника ВУ, DSR-готовность передатчика от ВУ, RTS- запрос готовности приемника ВУ, TxD-передатчик данных последовательным кодом, CxT-внешняя тактовая частота для асинхронизации, E- конец передачи (TxE), RDY- готовность передатчика, RxD-вход приемника последовательным кодом, CxD-внешняя синхронизация приемника, SYNDET – бит синхронизации( показывает какая синхр внешн или внутр).

В УСАПП есть режимы как синхр., так и асинхронного программирования.

После сброс (по вкл. питания) осущ-ся программирование УСАПП. Программирование осущ-ся 2 типами управляющих слов:

1)инструкция режима

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

Режимы(D0D1)

00-режим синхр.

01-асинхр. 1:1

10-асинхр1:16

11-асинхр. 1:64

Формат слов(D3D2)

00-5-ти битное слово

01-6-ти битное слово

10-7-ти битное слово

11-8-ти битное слово

Контроль(D5D4)

x0-нет, 01-на нечетность, 11-на четность

Длина стоповой посылки(D7D6)

00-запретная комб-я, 01-1 бит, 10-1,5 бита, 11-2 бита

RS-232

RS-232

RS-485

RS-422

Ряд

4800 9000 14800 49200 56000 …

1:64, 1 бит передается за 64 такта входной частоты

если стоповый бит 1,5 то при частоте 1:16 (за 24 такта), а 1:64(96)

При асинхронной передаче 1 инф-й бит передается столько периодов тактовой частоты, ск-ко задано битами D0D1 в инстр-ции режима. После стопового бита(1 выс ур-нь) передача начин стартовым битом(0 низ ур), затем идут инф-е биты, начиная с D0; по окончании инф-й посылки может быть контрольный бит9задается битами D5D4 инстр режима) после чего формируется стоповый бит ур.1.Тактовая частота задается внешними делителями по станд.ряду, соотв.интерфейсу типа RS

При синхронном режиме в паузах непрерывно передаются синхросимволы. Синхросимволы-собств. имя УСАПП. Если УСАПП настроен на прием, то он в получ. инфе отыскиваем сигналы одного или двух синхросимволов. Если УСАПП настроен на передачу в синхронном режиме перед передаваемыми данными УСАПП выдает собств.имя получателя (1 или 2 байта синхронизации). Затем выдается информационный байт о том, что байты синхронизации совпали УСАПП символ. наличием сигнала SYNDET. При синхронном режиме тактов частота также может подаваться на вход SYNDET.При сихр реж каждому периоду тактовой частоты соответствует 1 бит инфы.

Контролер ПДП.

Intel 82237

Центральная задача:

1)КПДП берет на себя функции управления СМ и формирование ША при отключении ЦП от СМ.

2)Осуществляет арбитраж между разными устройствами, запрашивающими режим ПДП.

Классическое периферийное устройство ВУ

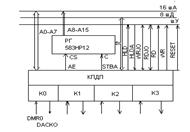

DMR-запрос на ПДП от ВУ, DACK-разрешение на ПДП от ВУ, HLD-запрос от пр-ра, HLDA-разрешение от пр-ра.

Контролер всегда имеет в паре: RDJ0, WR,RD, WRJ0.

Контролер имеет 4 идент. канала К0-К3. Каждый канал содержит 16 разр. регистр адреса и 14 разр. счетчик циклов. По включении питания ЦП в программе нач. пуска (BIOS) прогр-т все периферийные микросхемы, в том числе контролер ПДП. В контролере ПДП проц для каждого канала (ВУ) задает нач. адрес (перв.ячейку памяти запис-ся в РгА канала) и задается число циклов(зап-ся число циклов в канал).Адрес формируется путем инкрементирования РгА (соот-но после каждого цикла число циклов декрементируется). Режим ПДП заканчивается, когда счетчик циклов=0. В этот момент времени формируется сигнал TC т.е. последний цикл. Максимальный размер этого блока=16 кбайт, т.к. счетчик циклов 14р, максимальный объем памяти перегоняемый в ПДП=214 или 16 кбайт (ПДП не может слишком долго, так как СМ занята и невозможна регенерация динам памяти).

Как контролер ПДП подключается к СМ: STBA-строб адреса.

При программировании контролера использ-ся разряды ША А0÷А3 и CS=0. Помимо прогр-я каждого канала в отдельности запис-ся управл-ее слово(только после того как все каналы запрогр-ся).

Управл-ее слово задает приоритеты между каналами, устанавливается флаги конца цикла ПДП в слове состояния (СС).

ЦП период-ки считывает СС контр-ра ПДП , в котором определяет происходил ли обмен инфой по конкретным каналам (т.е свежая ли проц инф и забран ли от проца готовый предыдущий рез-т). Если цикл ПДП прошел, обмен инфой состоялся, пр-р перепрограммирует контр-р по данному каналу(это делает ОС).

STBA стробирует адрес на ША.

М128-каждый 128 цикл формируется строб, длительностью один цикл.чтобы показать что система не зависла, а идут циклы ПДП.